文章编号: 1006-626% 2007) 10-0051-03

# TG12864B 液晶显示器及其应用

赵晓荣,郎 兵

(北京交通大学电气工程学院,北京 100044)

摘 要: 描述了 TG12864B 的功能特点和 MB90F594A 的主要性能,详细分析了 TG12864B 的接口时序,并采用软件模拟方法实现了 TG12864B 与 MB90F594A 的接口技术。

关键词: TG12864B; MB90F594A; 时序; 软件模拟中图分类号: TN949.192 文献标识码: A

# The Liquid Crystal Display TG12864B and Its Application

ZHAO Xiao- rong, LANG Bing

(Beijing Jiaotong University, School of Electrical Engineering, Beijing 100044, China)

Abstract: This paper describes the function of the TG12864B and the main properties of the MB90F594A. And it analyses time sequence of the TG12864B in details. It also realizes the interface technology between the TG12864B and MB90F594A with software simulation.

Keywords: TG12864B; MB90F594A; time sequence; software simulation

### 1 引 言

MB90F594A 是富士通生产的 16 位微处理器,以其出色的性价比得到了广泛的应用,但是由于它不是总线处理器,其标准接口很有限,因此在与外围器件一起使用时,常常会遇到与接口不匹配的困难,采用软件模拟时序的方法可以有效地解决这一难题。本文讨论了一种采用软件模拟总线复用时序的方法来实现并行液晶显示芯片TG12864B 与 MB90F594A 的接口技术。在微机机电保护平台中通过 TG12864B 很好地实现了数据和信息的显示。

# 2 TG12864B 与 MB90F594A 概述

TG12864B 是一种图形点阵液晶显示器,它主要由行驱动器 / 列驱动器及 128× 64 全点阵液晶显示器组成。可完成图形显示,也可以显示 8×4 个(16×16 点阵) 汉字,全屏幕点阵,7 种指令,与 CPU接口采用 8 位数据总线并行输入输出和 8 条控制线,占空比 1/64。但是它没有字库,需要在软件中自带字库,该应用中通过汇编查表实现了各种信息的显示。模块的外部接口如表 1 所示。

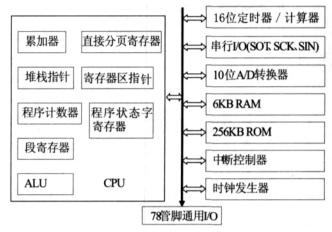

MB90F594A 最小机器时钟为 62.5ns/16MHz, 内有 256KB 的 ROM 和 6KB 的 RAM, 32 位的累

表 1 模块的外部接口

| 引脚   | 名称              | 电平    | 功能                            |

|------|-----------------|-------|-------------------------------|

| 1    | Vss             | 0V    | 电池地                           |

| 2    | V <sub>DD</sub> | 5.0V  | 电源电压                          |

| 3    | V <sub>0</sub>  | _     | 液晶显示驱动电压输入                    |

| 4    | D/I             | H/L   | H: DB0-DB8 为显示数据 L: DB0-DB8   |

|      |                 |       | 为显示指令数据                       |

| 5    | R/W             | H/L   | R/W=H, E=H 数据被读到 DB0 ~DB8; R/ |

|      |                 |       | W=L, E=H 变成 L, DB0 ~DB7 的数据被  |

|      |                 |       | 读到 IR 或 DR                    |

| 6    | E               | H/L   | 使能信号 R/W=L, E 信号下降沿锁存数        |

|      |                 |       | 据;R/W=H,E=H,DRAM 数据读到         |

|      |                 |       | DB0- DB7                      |

| 7~14 | DB0 ~DB7        | H/L   | 数据线                           |

| 15   | CS1             | H/L   | H: 选择芯片 1 信号                  |

| 16   | CS2             | H/L   | H: 选择芯片 2 信号                  |

| 17   | /RES            | H/L   | 复位信号                          |

| 18   | VEE             | - 10V | LCD 驱动负电压输入                   |

| 19   | LED+            | +5V   | 背光电源+                         |

| 20   | LED-            | 0V    | 背光接地                          |

|      |                 |       |                               |

加器可以进行长字数据操作,提高了算术计算的精确度,增强了有符号数的乘除。扩充了寻址方式,可达16MB的寻址空间,支持高级语言和多任务处理的指令集,内核支持高级语言。有专门的程序下载口,程序下载到芯片内不同于装在 ROM 中保密性好。

MB90F594A 的具体特性如下:(1)3通道的UART可选时钟同步/异步,具有专用的波特率发生率1,200~62,500bps);(2)1通道的时钟同步的3线串口,可选择从最高位 MSB)或最低位 LSB)开始传输;(3)2个CAN控制器,符合CAN2.0A和B的规范,具有16个双向缓冲区,传输速率达1Mbps;(4)8通道的8/10位A/D转换器,可单通道转换或扫描转换;(5)4通道的步进电机控制器,其中可包括2通道的8位PWM脉冲发生器,4通道的大电流输出;(6)8通道的外部中断,可选择上升沿、下降沿、边沿触发和高低电平触发;(7)6个独立的PPG单元,每个单元具有2通道的8位PPG,可输出任意占空比的脉冲,每个单元既可以单通道运行,又可以2个通道作为一个16位的PPG运行;(8)2通道的16位重载入定时器,选择边沿触发,可

以重装载、单次事件计数;选择高电平或低电平触发,可以进行脉冲宽度计算;(9)6通道的输入捕捉,6通道的输出比较;(10)具有78个I/O引脚,其中24个可通过软件设置上拉电阻,8个具有大电流驱动能力。

图 1 MB90F594A 的结构图

## 3 TG12864B 的接口时序分析及模拟

TG12864B 的数据线和地址线是相同的接口线DB0~DB7, 而 MB90F594A 不是总线型微处理器,没有专门的读写数据总线,所以在接口时序上是不匹配的,由于 MB90F594A 的大部分管脚都是复用的通用输入输出引脚,所以考虑采用软件模拟的方法来模拟 TG12864B 的时序来实现两者的接口匹配。该方法采用纯软件实现,无需外围器件,方便可靠。

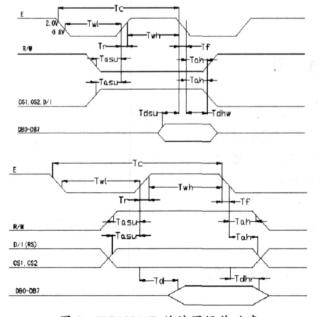

图 2 TG12864B 的读写操作时序

软件模拟的任务就是用软件编程的方法对 MB90F594A的 I/O 口操作模拟出符合图 2 所要求的 时序,从而实现读写操作的目的。要模拟出图2的时序 需要 MB90F594A 的 13 条 I/O 线, 其中 5 条控制线, 分别与 TG12864B 的 E、R/W、D/I、CSA 和 CSB 相对 应。在此假设仅对前64列进行操作,从表1可以看出 片选是高电平有效, 所以置 CSA 为高 CSB 为低。8条 为数据地址复用线, 分别与 DB0~DB7 相对应。5 条控 制线均设置为输出口,而8位数据线则不同,在一个读 周期,令其为输入口,用于传送数据,主要用来检测 LCD 的状态; 在一个写周期, 应设置为输出口向 LCD 写入指令或数据,但同时要检测 LCD 的状态是否忙, 当忙时禁止任何操作。使能控制E在下降沿时锁存数据。

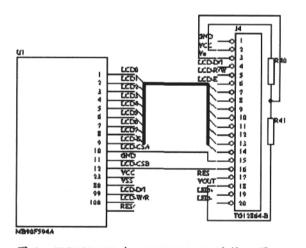

如图 3 所示, P1.6~P1.7、P3.0~P3.2 是控制 线, P2.0~P2.7 是数据和地址复用线, 他们的功能 和一般的 I/O 复用引脚相同,并且可以通过设置端 口方向寄存器 DDR 使其成为输出口还是输入口,设 置为 0 是输入口, 1 是输出口; 通过设置数据寄存器 PDR 来设定 I/O 口的初始值, 是 0 还是 1。

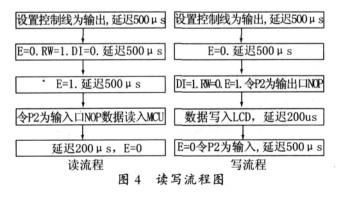

图 3 TG12864B 与 MB90F594A 的接口图 图 4 是对 TG12864B 读一字节数据和写入一 字节数据或指令的软件流程图。

写指令: 写指令: SETB DDR9:PINE: SETB DDR9:PINE; 置控制口为输出口 置控制口为输出口 SETB DDR8:PINRW SETB DDR8:PINRW SETB DDR8:PINDI SETB DDR8:PINDI SETB DDRO:PINCSA SETB DDRO:PINCSA SETB DDRO:PINCSB SETB DDRO:PINCSB CLRB PDR9:PINE: E清0 CLRB PDR9:PINE: E清0 SETB PDR8:PINRW; 读 CALL T500U CLRB PDR8:PINDI; 指令 PDR8:PINDI: 指令 CLRB CALL T500U: 延迟500us CLRB PDR8:PINRW; 写 SETB PDR9:PINE: E置1 SETB PDR9:PINE: E置1 CALL T500U; 延迟500us MOV DDR1, #OFFH: DDR1, #00H; 置为输出口 MOV 置为输入口 NOP NOP MOV PDR1, A; 指令送入端口 BBC PDR1:4, TESTBUSY; CALL T200U; 状态检测 延迟200us CALL T200U; 延迟200us CLRB PDR9:PINE TESTBUSY: NOP PDR1:7, TURE\_WRITE BBC MOV DDR1, #00H CALL T200U CALL T500U

基于上述硬件电路和软件设计思想,实现的对 TG12864B 的读写操作。

## 结语

本文在分析了 TG12864B 读写时序的基础上, 讨论了采用软件模拟的方法实现与 MB90F594A 的 接口技术,该方法接口简单,方便可靠,在解决低速 外设与高速 MCU 的接口问题上具有实际应用意 义, 另外 MB90F594A 应用较少, 为其开发应用提供 了参考材料。

#### 参考文献:

- [1] 钟华等. 富士通 16 位微控制器开发与应用. 北 京: 机械工业出版社, 2005: 11-137.

- [2] 宋豫全, 张延彬. DS12887 在 TMS320LF2407 应用系统中的接口技术 [J]. 微机算机信息, 2004, 20 11).

- [3] 王文根等. 液晶电视材料进展[J]. 现代显示, 2006 7): 45-49.

作者简介: 赵晓荣 1982-), 男, 在读硕士, 就读于北 京交通大学电气工程学院, 主要研究方向为微机继 电保护, Email: zhxr131ysy@163.com。

Oct., 2007, 总第80期