# ASIC LIBRARY DESIGN

3

*Key concepts:* Tau, logical effort, and the prediction of delay • Sizes of cells, and their drive strengths • Cell importance • The difference between gate-array macros, standard cells, and datapath cells

ASIC design uses predefined and precharacterized cells from a library—so we need to design or buy a cell library. A knowledge of ASIC library design is not necessary but makes it easier to use library cells effectively.

3.1 Transistors as Resistors

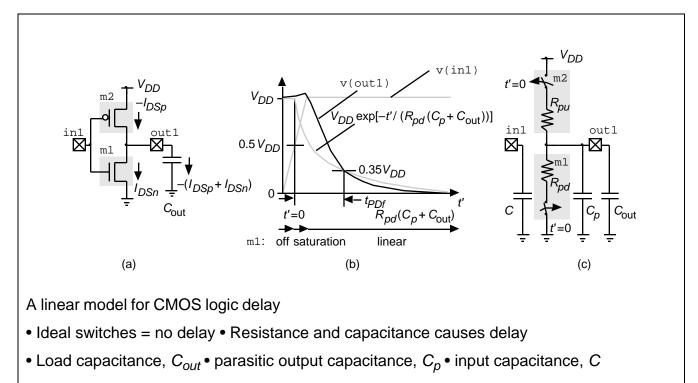

$-t_{PDf}$   $0.35 V_{DD} = V_{DD} \exp - \frac{-t_{PDf}}{R_{pd} (C_{out} + C_p)}$

An output trip point of 0.35 is convenient because  $\ln(1/0.35)=1.04$  1 and thus  $t_{PDf} = R_{pd}(C_{out} + C_p) \ln(1/0.35)$   $R_{pd}(C_{out} + C_p)$ For output trip points of 0.1/0.9 we multiply by  $-\ln(0.1) = 2.3$ , because exp (-2.3) = 0.100

- Linearize the switch resistance Pull-up resistance,  $R_{pu}$  pull-down resistance,  $R_{pd}$

- Measure and compare the input, v(in1) and output, v(out1)

- Input trip point of 0.5 output trip points are 0.35 (falling) and 0.65 (rising)

- The linear prop–ramp model: falling propagation delay,  $t_{PDf} R_{pd}(C_p + C_{out})$

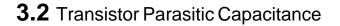

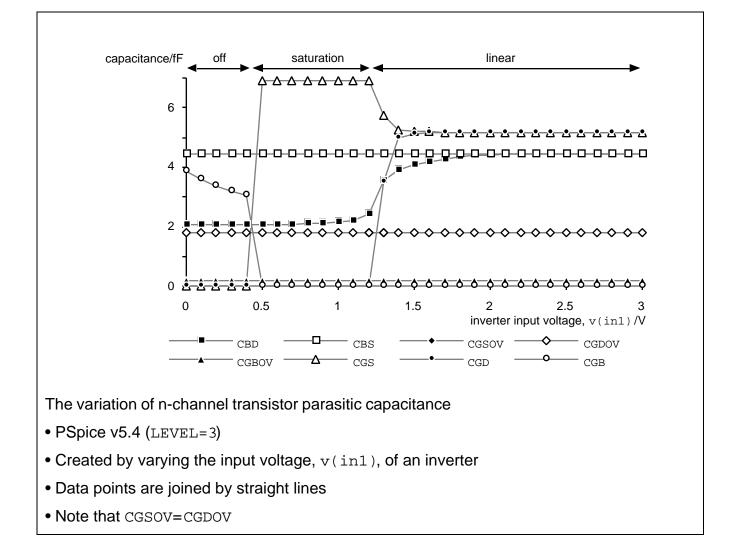

- $C_{BS}$  and  $C_{BD}$  are the sum of the area ( $C_{BSJ}$ ,  $C_{BDJ}$ ), sidewall ( $C_{BSSW}$ ,  $C_{BDSW}$ ), and channel edge ( $C_{BSJGATE}$ ,  $C_{BDJGATE}$ ) capacitances

- $L_D$  is the lateral diffusion  $T_{FOX}$  is the field-oxide thickness

| NAME  | ml       | m2        |

|-------|----------|-----------|

| MODEL | CMOSN    | CMOSP     |

| ID    | 7.49E-11 | -7.49E-11 |

| VGS   | 0.00E+00 | -3.00E+00 |

| VDS   | 3.00E+00 | -4.40E-08 |

| VBS   | 0.00E+00 | 0.00E+00  |

| VTH   | 4.14E-01 | -8.96E-01 |

| VDSAT | 3.51E-02 | -1.78E+00 |

| GM    | 1.75E-09 | 2.52E-11  |

| GDS   | 1.24E-10 | 1.72E-03  |

| GMB   | 6.02E-10 | 7.02E-12  |

| CBD   | 2.06E-15 | 1.71E-14  |

| CBS   | 4.45E-15 | 1.71E-14  |

| CGSOV | 1.80E-15 | 2.88E-15  |

| CGDOV | 1.80E-15 | 2.88E-15  |

| CGBOV | 2.00E-16 | 2.01E-16  |

| CGS   | 0.00E+00 | 1.10E-14  |

| CGD   | 0.00E+00 | 1.10E-14  |

| CGB   | 3.88E-15 | 0.00E+00  |

- ID ( $I_{DS}$ ), VGS, VDS, VBS, VTH ( $V_t$ ), and VDSAT ( $V_{DS(sat)}$ ) are DC parameters

- GM, GDS, and GMB are small-signal conductances (corresponding to  $I_{DS}/V_{GS}$ ,  $I_{DS}/V_{DS}$ , and  $I_{DS}/V_{BS}$ , respectively)

| PSpice             | Equation                                                                                                                                                                  | Values <sup>1</sup> for $V_{GS}$ =0V, $V_{DS}$ =3V, $V_{SB}$ =0V                                                       |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| CBD                |                                                                                                                                                                           | $C_{BD} = 1.855 \times 10^{-13} + 2.04 \times 10^{-16} = 2.06 \times$                                                  |

|                    | $C_{BD} = C_{BDJ} + C_{BDSW}$                                                                                                                                             | 10 <sup>-13</sup> F                                                                                                    |

|                    | $C_{BDJ} + A_D C_J (1 + V_{DB}/B)^{-mJ} (B = PB)$                                                                                                                         | $C_{BDJ}$ = (4.032 × 10 <sup>-15</sup> )(1 + (3/1)) <sup>-0.56</sup> = 1.86 × 10 <sup>-15</sup> F                      |

|                    | $C_{BDSW} = P_D C_{JSW} (1 + V_{DB}/B)^{-mJSW}$<br>( $P_D$ may or may not include channel edge)                                                                           | $C_{BDSW}$ = (4.2 × 10 <sup>-16</sup> )(1 + (3/1)) <sup>-0.5</sup> = 2.04 × 10 <sup>-16</sup> F                        |

| CBS                | $C_{BS} = C_{BSJ} + C_{BSSW}$                                                                                                                                             | $C_{BS} = 4.032 \times 10^{-15} + 4.2 \times 10^{-16} = 4.45 \times 10^{-15} \text{ F}$                                |

|                    | $C_{BSJ}$ + A <sub>S</sub> C <sub>J</sub> (1 + V <sub>SB</sub> /B) <sup>-mJ</sup>                                                                                         | $A_{S} C_{J} = (7.2 \times 10^{-15})(5.6 \times 10^{-4}) = 4.03 \times 10^{-15} F$                                     |

|                    | $C_{BSSW} = P_S C_{JSW} (1 + V_{SB}/B)^{-mJSW}$                                                                                                                           | $P_{S}C_{JSW} = (8.4 \times 10^{-6})(5 \times 10^{-11}) = 4.2 \times 10^{-16} \text{ F}$                               |

| CGSOV              | $C_{GSOV}=W_{EFF}C_{GSO}$ ; $W_{EFF}=W-2W$<br>D                                                                                                                           | $C_{GSOV} = (6 \times 10^{-6})(3 \times 10^{-10}) = 1.8 \times 10^{-16} \text{ F}$                                     |

| CGDOV              | $C_{GDOV} = W_{EFF}C_{GSO}$                                                                                                                                               | $C_{GDOV} = (6 \times 10^{-6})(3 \times 10^{-10}) = 1.8 \times 10^{-15} \text{ F}$                                     |

| CGBOV              | $C_{GBOV} = L_{EFF}C_{GBO}$ ; $L_{EFF} = L - 2L_{D}$                                                                                                                      | $C_{GDOV} = (0.5 \times 10^{-6})(4 \times 10^{-10}) = 2 \times 10^{-16} \text{ F}$                                     |

| CGS                | $C_{GS}/C_{O} = 0$ (off), 0.5 (lin.), 0.66 (sat.)<br>$C_{O}$ (oxide capacitance) = $W_{EF}L_{EFF}$ ox<br>/ $T_{ox}$                                                       | $C_{O} = (6 \times 10^{-6})(0.5 \times 10^{-6})(0.00345) = 1.03 \times 10^{-14} \text{ F}$<br>$C_{GS} = 0.0 \text{ F}$ |

| CGD                | C <sub>GD</sub> /C <sub>O</sub> = 0 (off), 0.5 (lin.), 0 (sat.)                                                                                                           | $C_{\rm GD} = 0.0 \; {\rm F}$                                                                                          |

| CGB                | $C_{GB} = 0$ (on), = C <sub>O</sub> in series with $C_{GS}$ (off)                                                                                                         | $C_{GB} = 3.88 \times 10^{-15}$ F, $C_{S}$ =depletion capacitance                                                      |

| <sup>1</sup> Input | VTO=0.65 DELTA=0.7<br>+ LD=5E-08 KP=2E-04 UO=550 T<br>NSUB=1.4E+17 NFS=6E+11<br>+ VMAX=2E+05 ETA=3.7E-02 KAP<br>CGSO=3.0E-10 CGBO=4.0E-10<br>+ CJ=5.6E-04 MJ=0.56 CJSW=5E | PA=2.9E-02 CGDO=3.0E-10                                                                                                |

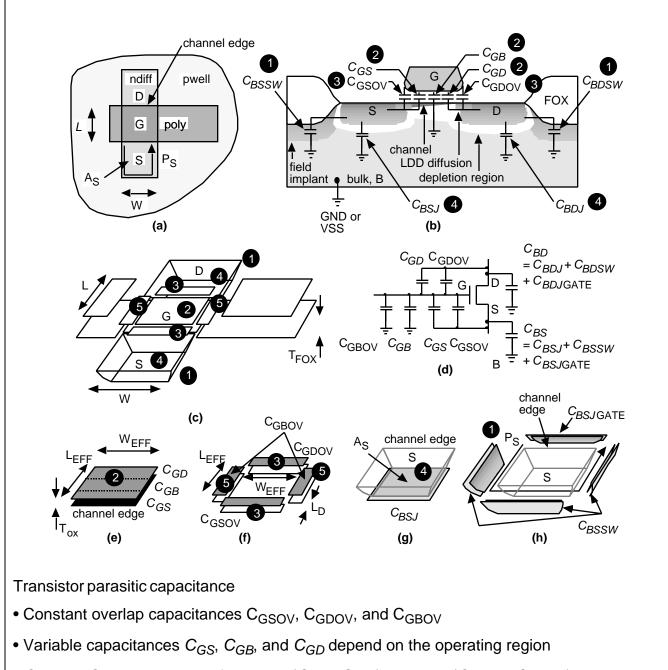

#### 3.2.1 Junction Capacitance

• Junction capacitances,  $C_{BD}$  and  $C_{BS}$ , consist of two parts: junction area and sidewall

• Both  $C_{BD}$  and  $C_{BS}$  have different physical characteristics with parameters: CJ and MJ for the junction, CJSW and MJSW for the sidewall, and PB is common

•  $C_{BD}$  and  $C_{BS}$  depend on the voltage across the junction ( $V_{DB}$  and  $V_{SB}$ )

• The sidewalls facing the channel ( $C_{BSJGATE}$  and  $C_{BDJGATE}$ ) are different from the sidewalls that face the field

• It is a mistake to exclude the gate edge assuming it is in the rest of the model-it is not

• In HSPICE there is a separate mechanism to account for the channel edge capacitance (using parameters ACM and CJGATE)

#### 3.2.2 Overlap Capacitance

- The overlap capacitance calculations for C<sub>GSOV</sub> and C<sub>GDOV</sub> account for lateral diffusion

- SPICE parameter LD=5E-08 or LD=0.05 µm

- Not all SPICE versions use the equivalent parameter for width reduction,  $\mathtt{WD},$  in calculating  $C_{GDOV}$

Not all SPICE versions subtract W<sub>D</sub> to form W<sub>EFF</sub>

#### 3.2.3 Gate Capacitance

• The gate capacitance depends on the operating region

• The gate–source capacitance  $C_{GS}$  varies from zero (off) to  $0.5C_{O}$  in the linear region to (2/3) $C_{O}$  in the saturation region

• The gate–drain capacitance  $C_{GD}$  varies from zero (off) to 0.5C<sub>O</sub> (linear region) and back to zero (saturation region)

• The gate–bulk capacitance  $C_{GB}$  is two capacitors in series: the fixed gate-oxide capacitance,  $C_{O}$ , and the variable depletion capacitance,  $C_{S}$

• As the transistor turns on the channel shields the bulk from the gate—and  $C_{GB}$  falls to zero

• Even with  $V_{GS}$ =0V, the depletion width under the gate is finite and thus  $C_{GB}$  is less than  $C_O$

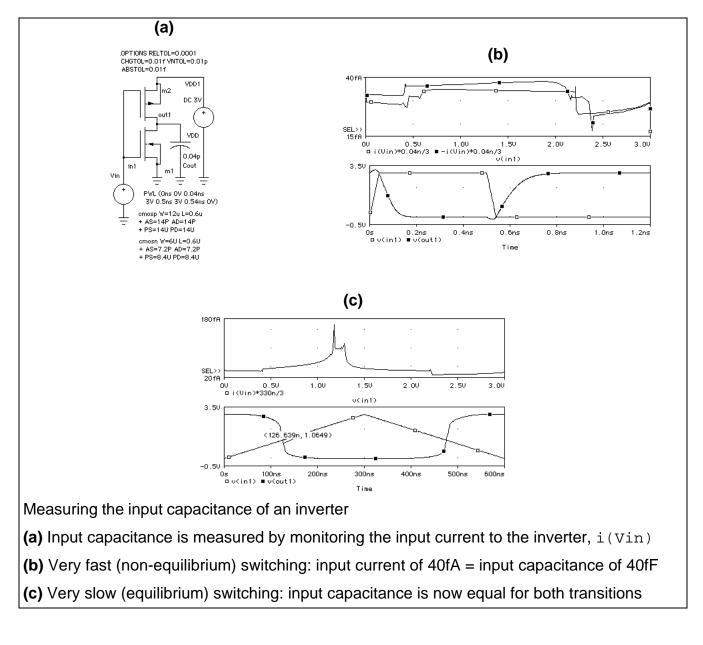

#### 3.2.4 Input Slew Rate

Parasitic capacitance measurement

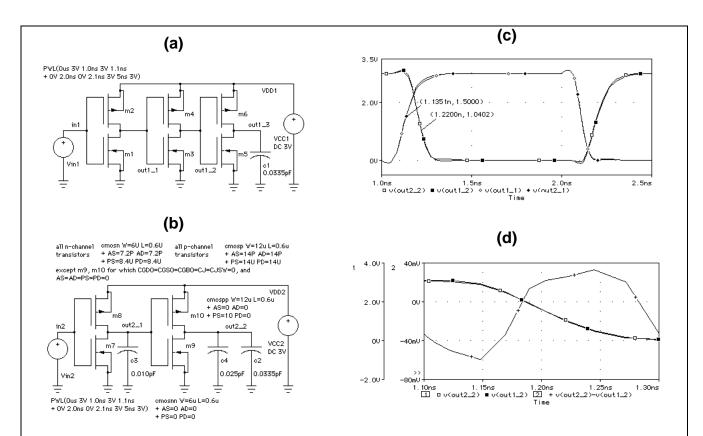

(a) All devices in this circuit include parasitic capacitance

(b) This circuit uses linear capacitors to model the parasitic capacitance of m9/10.

• The load formed by the inverter (m5 and m6) is modeled by a 0.0335pF capacitor (c2)

• The parasitic capacitance due to the overlap of the gates of  $m_3$  and  $m_4$  with their source, drain, and bulk terminals is modeled by a 0.01pF capacitor (c3)

• The effect of the parasitic capacitance at the drain terminals of m3 and m4 is modeled by a 0.025pF capacitor (c4)

(c) Comparison of (a) and (b). The delay (1.22-1.135=0.085ns) is equal to  $t_{PDf}$  for the inverter m3/4

(d) An exact match would have both waveforms equal at the 0.35 trip point (1.05V).

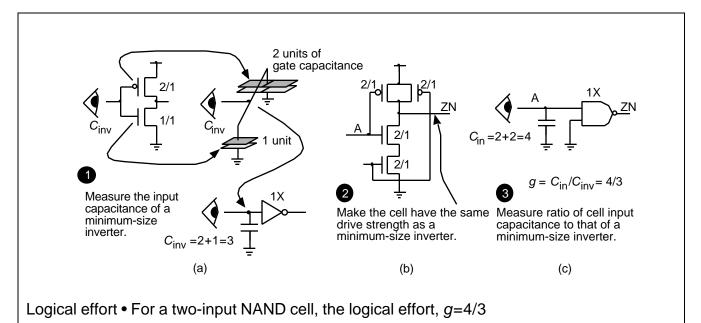

### **3.3** Logical Effort

We extend the prop-ramp model with a "catch all" term,  $t_{q}$ , that includes:

- delay due to internal parasitic capacitance

- the time for the input to reach the switching threshold of the cell

- the dependence of the delay on the slew rate of the input waveform

$t_{PD} = R(C_{out} + C_p) + t_q$ We can **scale** any logic cell by a scaling factor s:  $t_{PD} = (R/s) \cdot (C_{out} + sC_p) + st_q$

$$t_{PD} = RC - C_{out} + RC_p + st_q$$

$$C_{in}$$

The time constant **tau**,  $= R_{inv} C_{inv}$ , is a basic property of any CMOS technology

The delay equation is the sum of three terms, d = f + p + q or delay = effort delay + parasitic delay + nonideal delay

The effort delay f is the product of **logical effort**, g, and **electrical effort**, h: f = gh

Thus, delay = logical effort × electrical effort + parasitic delay + nonideal delay

• R and C will change as we scale a logic cell, but the RC product stays the same

• Logical effort is independent of the size of a logic cell

• We can find logical effort by scaling a logic cell to have the same drive as a 1X minimum-size inverter

• Then the logical effort, g, is the ratio of the input capacitance,  $C_{in}$ , of the 1X logic cell to  $C_{inv}$

(a) Find the input capacitance,  $C_{inv}$ , looking into the input of a minimum-size inverter in terms of the gate capacitance of a minimum-size device

(b) Size a logic cell to have the same drive strength as a minimum-size inverter (assuming a logic ratio of 2). The input capacitance looking into one of the logic-cell terminals is then  $C_{in}$

(c) The logical effort of a cell is  $C_{in}/C_{inv}$

The *h* depends only on the load capacitance  $C_{out}$  connected to the output of the logic cell and the input capacitance of the logic cell,  $C_{in}$ ; thus

#### electrical effort $h = C_{out} / C_{in}$

**parasitic delay**  $p = RC_p$  (the parasitic delay of a minimum-size inverter is:  $p_{inv} = C_p / C_{inv}$ )

**nonideal delay**  $q = st_q / dt_q$

| Cell effort, paras | sitic delay, and no            | nideal delay (in ur                    | nits of ) for single-     | stage CMOS cells          |

|--------------------|--------------------------------|----------------------------------------|---------------------------|---------------------------|

| Cell               | Cell effort<br>(logic ratio=2) | Cell effort<br>(logic ratio=r)         | Parasitic delay/          | Nonideal delay/           |

| inverter           | 1 (by definition)              | 1 (by definition)                      | $p_{inv}$ (by definition) | $q_{inv}$ (by definition) |

| n-input NAND       | ( <i>n</i> +2)/3               | ( <i>n</i> + <i>r</i> )/( <i>r</i> +1) | np <sub>inv</sub>         | nq <sub>inv</sub>         |

| n-input NOR        | (2 <i>n</i> +1)/3              | ( <i>nr</i> +1)/( <i>r</i> +1)         | np <sub>inv</sub>         | nq <sub>inv</sub>         |

#### ASICS... THE COURSE

#### 3.3.1 Predicting Delay

- Example: predict the delay of a three-input NOR logic cell

- 2X drive

- driving a net with a fanout of four

0.3pF total load capacitance (input capacitance of cells we are driving plus the interconnect)

- $p=3p_{inv}$  and  $q=3q_{inv}$  for this cell

- the input gate capacitance of a 1X drive, three-input NOR logic cell is equal to gCinv

- for a 2X logic cell,  $C_{in} = 2gC_{inv}$

$gh = g \quad \frac{C_{\text{out}}}{C_{\text{in}}} = \frac{g \cdot (0.3 \text{ pF})}{2gC_{\text{inv}}} = \frac{(0.3 \text{ pF})}{(2) \cdot (0.036 \text{ pF})}$  (Notice g cancels out in this equation)

The delay of the NOR logic cell, in units of , is thus

$$d = gh + p + q = \frac{0.3 \times 10^{-12}}{(2) \cdot (0.036 \times 10^{-12})} + (3) \cdot (1) + (3) \cdot (1.7)$$

= 4.1666667 + 3 + 5.1

= 12.266667 equivalent to an absolute delay,  $t_{PD}$  12.3×0.06ns=0.74ns

The delay for a 2X drive, three-input NOR logic cell is  $t_{PD} = (0.03 + 0.72C_{out} + 0.60)$  ns

With  $C_{out}$ =0.3pF,  $t_{PD}$ = 0.03 + (0.72)·(0.3) + 0.60 = 0.846 ns compared to our prediction of 0.74ns

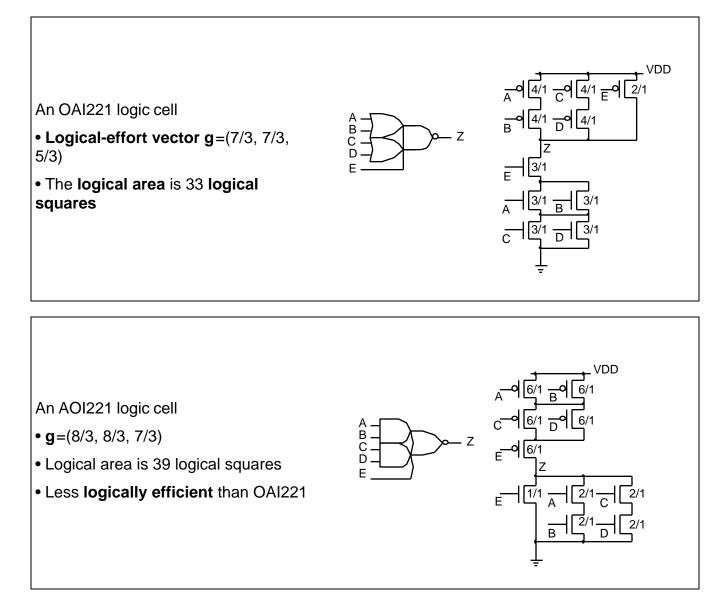

#### 3.3.2 Logical Area and Logical Efficiency

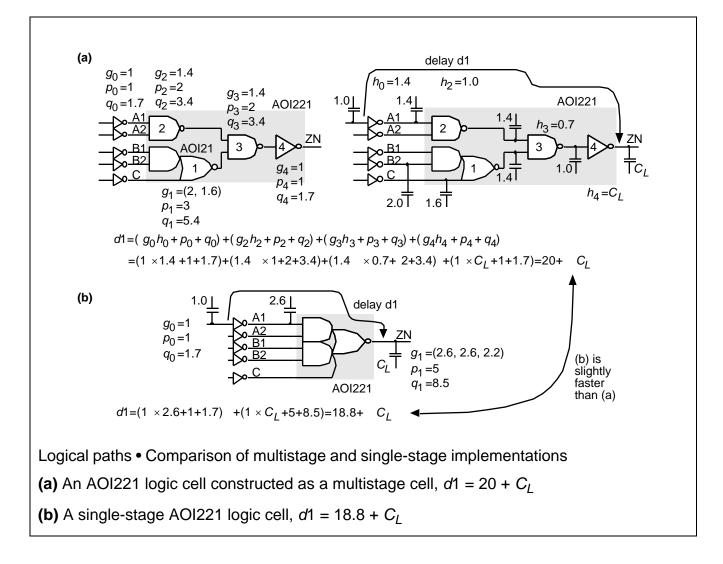

#### 3.3.3 Logical Paths

path delay  $D = g_i h_i + (p_i + q_i)$ *i* path *i* path

#### 3.3.4 Multistage Cells

#### 3.3.5 Optimum Delay

path logical effort G = gi i path C<sub>out</sub> h<sub>i</sub> path electrical effort H =Cin i path  $C_{out}$  is the load and  $C_{in}$  is the first input capacitance on the path path effort F = GH $f^{n}_{i} = g_{i}h_{i} \qquad = F^{1/N}$ optimum effort delay  $D^{\Lambda} = NF^{1/N} = N(GH)^{1/N} + P + Q$ optimum path delay P + Q = $p_i + h_i$

> i path

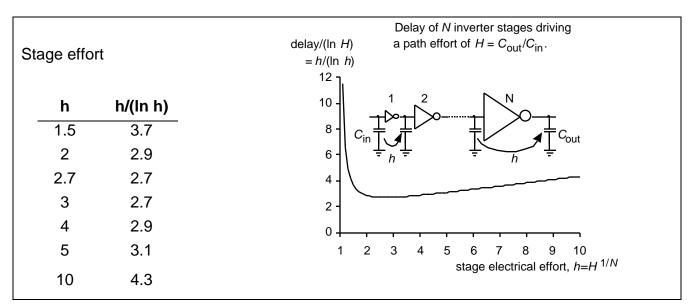

### 3.3.6 Optimum Number of Stages

• Chain of *N* inverters each with equal stage effort, *f=gh*

• Total path delay is Nf=Ngh=Nh, since g=1 for an inverter

- To drive a path electrical effort H,  $h^N = H$ , or  $N \ln h = \ln H$

- Delay, Nh = hln H/ln h

- Since In*H* is fixed, we can only vary *h*/In(*h*)

- $h/\ln(h)$  is a shallow function with a minimum at h=e 2.718

- Total delay is *N*e=eIn *H*

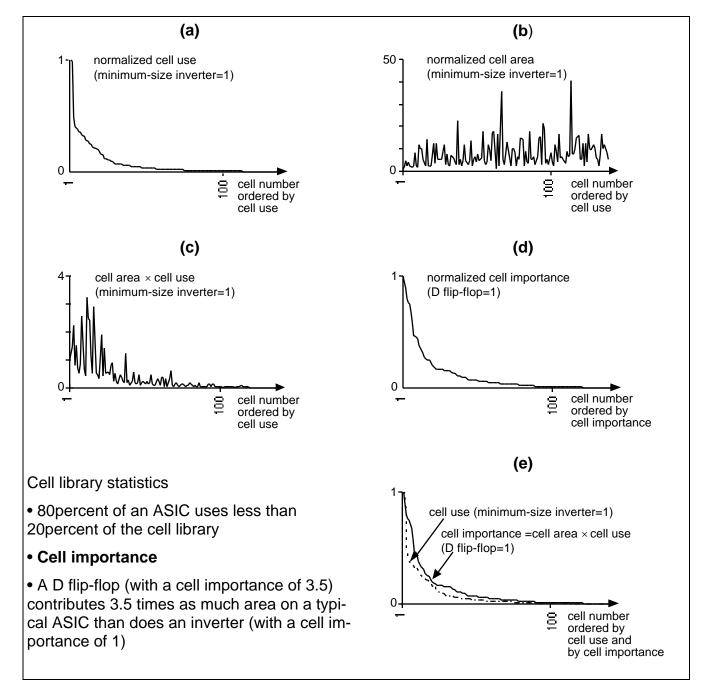

### 3.4 Library-Cell Design

- A big problem in library design is dealing with design rules

- Sometimes we can **waive** design rules

- **Symbolic layout**, **sticks** or **logs** can decrease the library design time (9 months for Virtual Silicon–currently the most sophisticated standard-cell library)

- Mapping symbolic layout uses 10–20 percent more area (5–10 percent with compaction)

- Allowing 45° layout decreases silicon area (some companies do not allow 45° layout)

### 3.5 Library Architecture

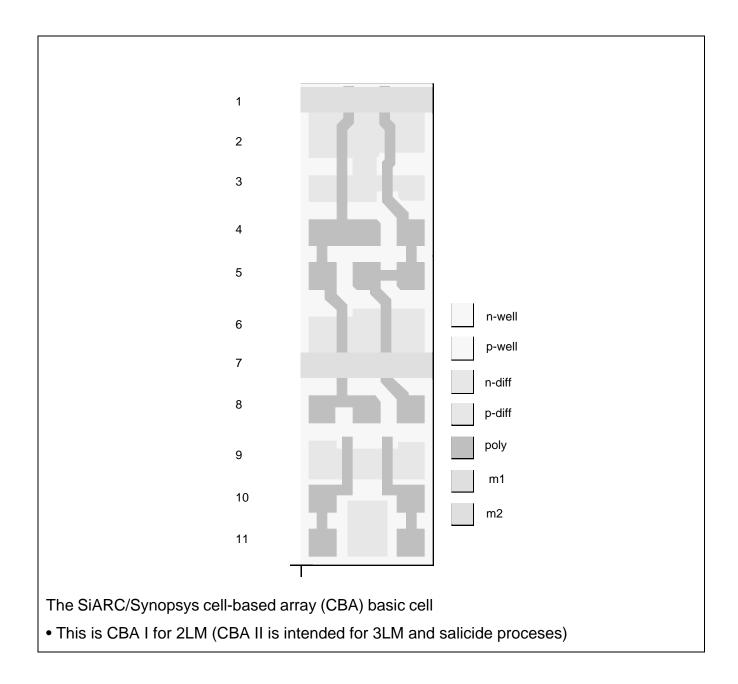

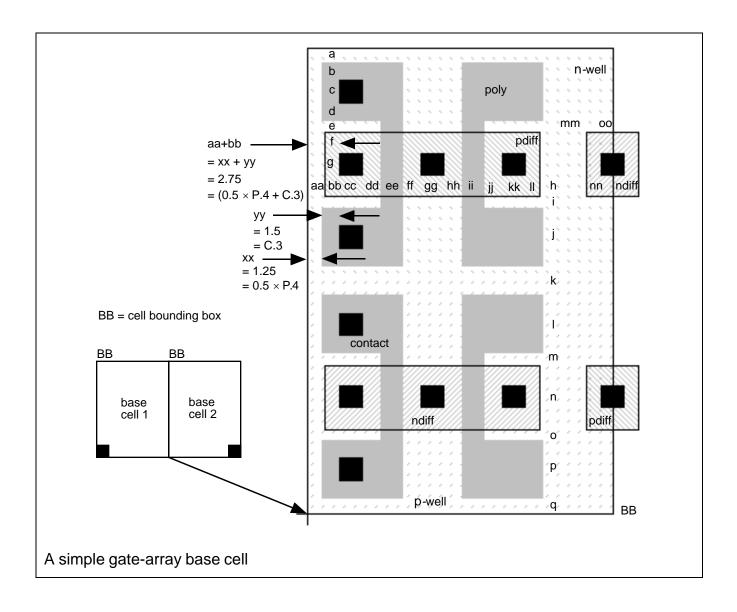

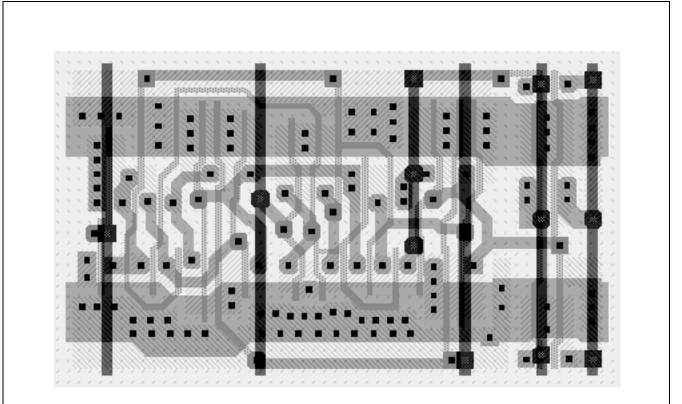

### 3.6 Gate-Array Design

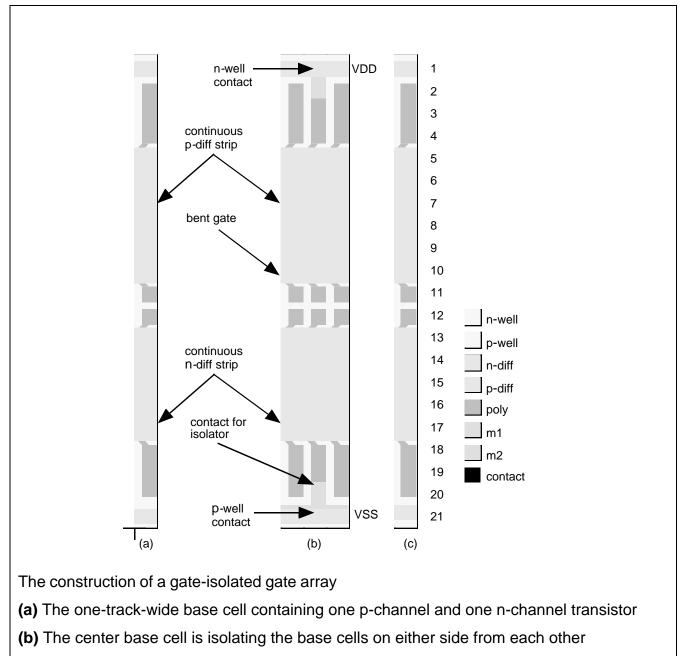

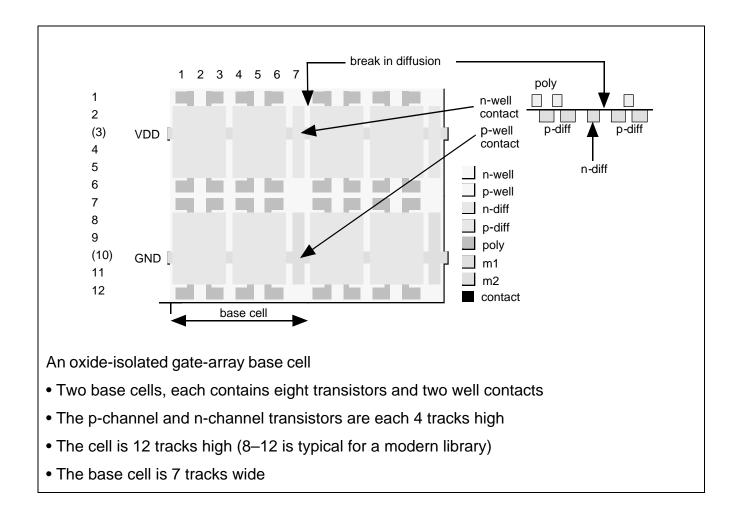

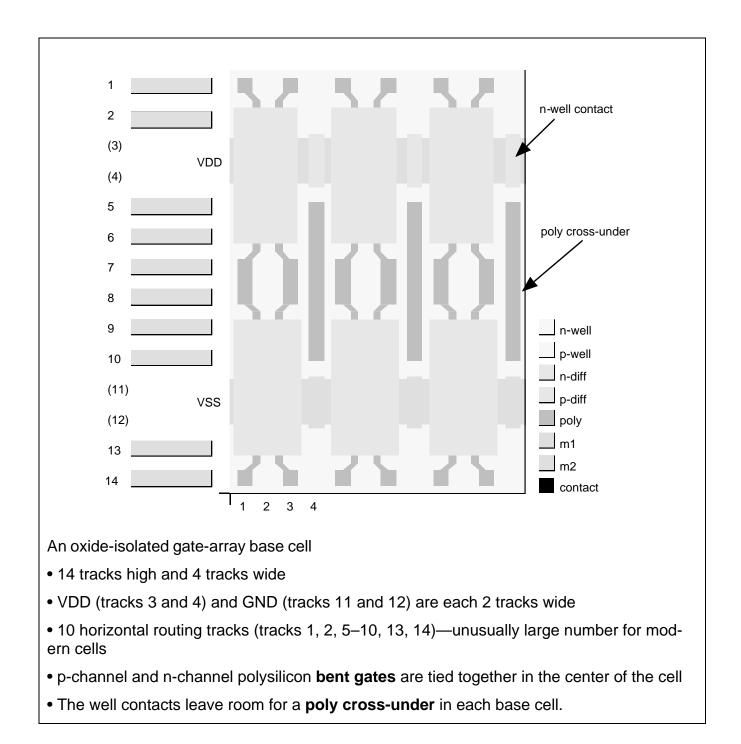

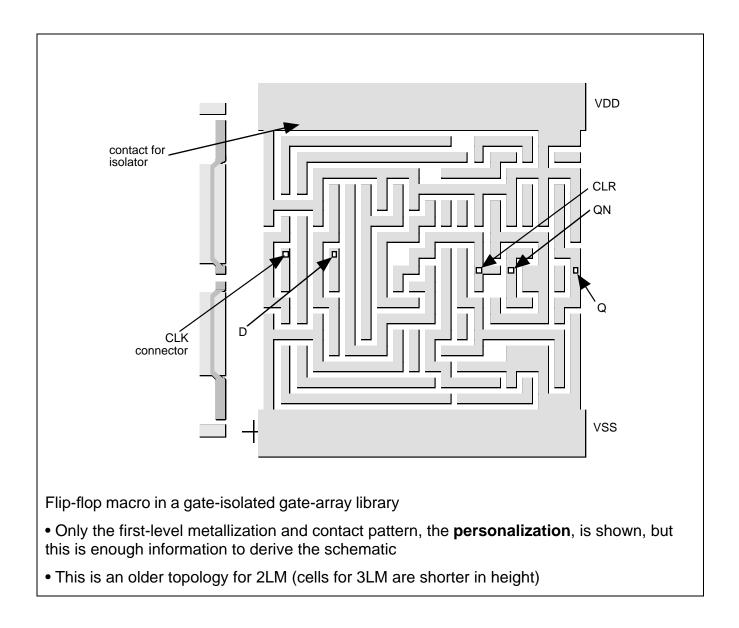

*Key words:* gate-array base cell (or base cell) • gate-array base (or base) • horizontal tracks • vertical track • gate isolation • isolator transistor • oxide isolation • oxide-isolated gate array

(c) The base cell is 21 tracks high (high for a modern cell library)

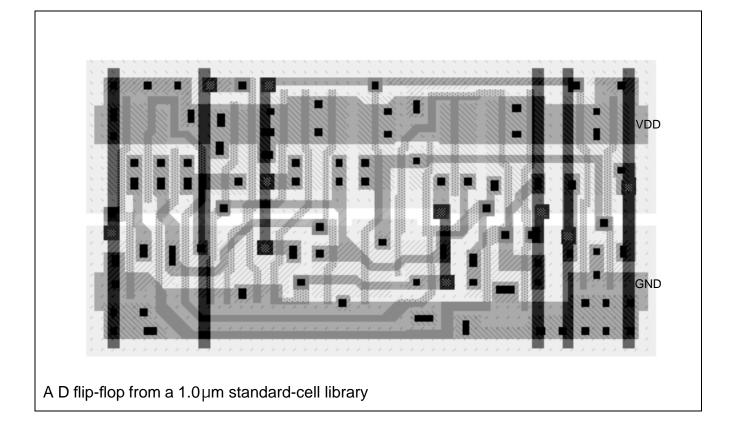

### 3.7 Standard-Cell Design

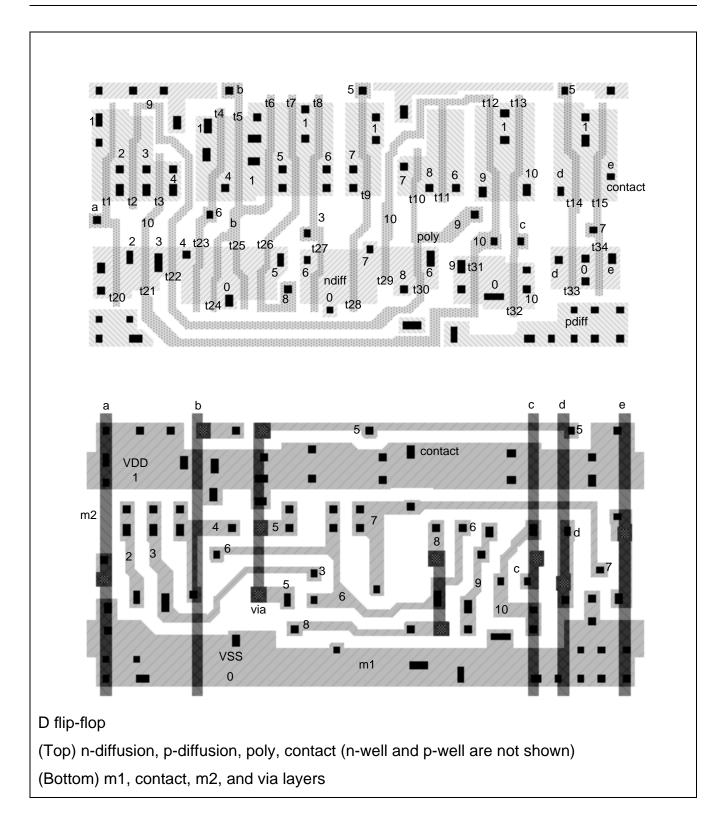

- A D flip-flop standard cell

- Performance-optimized library Area-optimized library

- Wide power buses and transistors for a performance-optimized cell

- Double-entry cell intended for a 2LM process and channel routing

- Five connectors run vertically through the cell on m2

- The extra short vertical metal line is an internal crossover

- bounding box (BB) abutment box (AB) physical connector abut

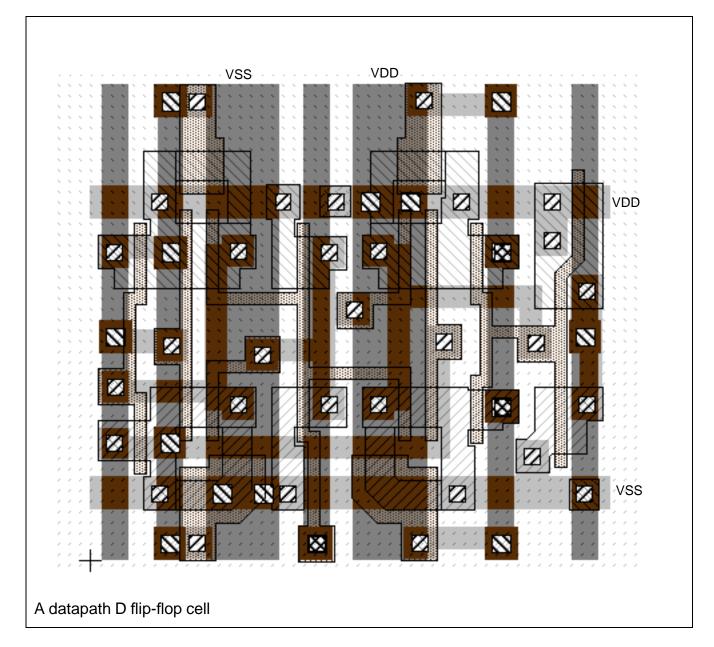

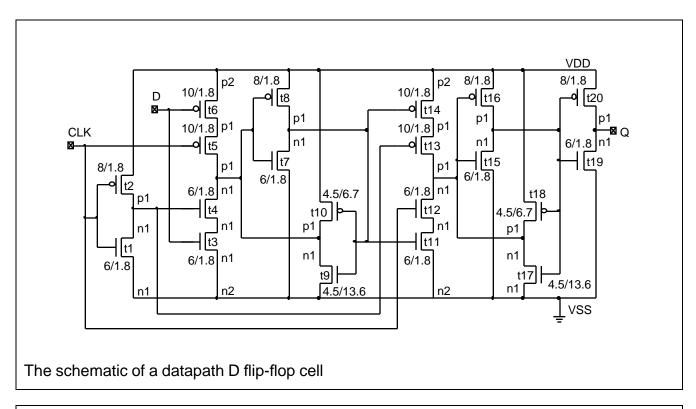

### 3.8 Datapath-Cell Design

(b)

| 1                            |                                          |            | S ALL AND                       | is in the |                                       |                                                                                                                                                                                                                                    | and shares                 | Street als  | the second se |

|------------------------------|------------------------------------------|------------|---------------------------------|-----------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------|-----------------------------------------------------------------------------------------------------------------|

|                              |                                          |            | George 1 (*<br>aussi i conficio |           | galer singeriger<br>Diserte di Jurian |                                                                                                                                                                                                                                    |                            | -           | -11.18                                                                                                          |

| -                            | 1.0                                      | - Speakers |                                 |           | all <sup>e 1</sup> Shaderholes        | ning block                                                                                                                                                                                                                         |                            | (Station)   | 1.Sat                                                                                                           |

|                              |                                          |            |                                 |           |                                       |                                                                                                                                                                                                                                    |                            |             |                                                                                                                 |

| for a r                      | ifter berter frig                        | 111 2 1    | r start                         | n-1 -1    | ije na zipne s                        | - Carlinsian - S                                                                                                                                                                                                                   |                            | P-212-977-1 | 215 12                                                                                                          |

| . Winderstein<br>wiederstein | an a |            | i i stille<br>Startyt (s        |           | in the later<br>Later 94, Auto        | in de la compañía de<br>Compañía de la compañía de la compañí | and There<br>parts ( Joan) |             |                                                                                                                 |

|                              |                                          |            |                                 |           | ann an stàite<br>Ann an stàite        | interation<br>second and an<br>analysis                                                                                                                                                                                            | n da arten<br>Konere (Kone |             |                                                                                                                 |

A narrow datapath

(a) Implemented in a two-level metal process

(b) Implemented in a three-level metal process

## 3.9 Summary

### Key concepts:

- Tau, logical effort, and the prediction of delay

- Sizes of cells, and their drive strengths

- Cell importance

- The difference between gate-array macros, standard cells, and datapath cells