## 51 脚上的窄脉冲

## --Who killed my LM75A ?

产品中用到自动温控功能,选用的 LM75 芯片,控制和数据为 IIC 数据接口,地址设定为 0111B。MCU 为新茂的 51 兼容单片机 SM5964。研发阶段使用的和 LM75 兼容的芯片 DS75。前面程序经过了仿真,时序满足 LM75 要求。板子做回来上板即正常应用,后来换用一个 LM75 兼容的芯片——TCN75,功能也正常。可前些天生产部门说产品没有温度显示,于是拿来生产用的样品进行实验分析。

生产采购的是 LM75A,带来的几片样品测试结果——没有温度输出。经过对 LM75、LM75A、DS75、TCN75的 datasheet 仔细比较,发现 LM75A 电压适用范围更大了些,速度更快了些,温度精度也有所提高。不过,芯片的默认状态是相同的,我们的 SM5964 输出时序也是能满足 LM75A 芯片需求的。经过一天的时序调整和数据手册的对比,确认不是程序的问题,于是怀疑芯片是假货或者存在质量问题。

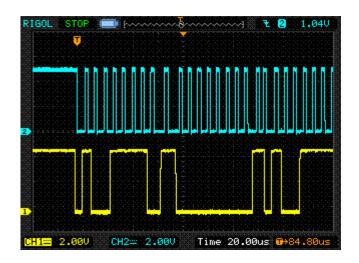

下面是单片机 P3.5 口的 SDA 和 SCL 在没有焊 LM75 芯片时的输出波形。

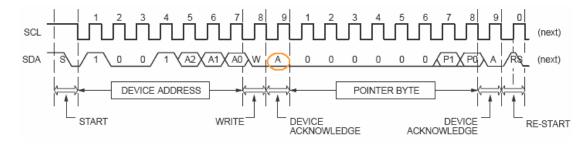

按照 LM75A 的数据手册,在下面的褐色标记的地方 LM75A 会给出一个低电平应答。

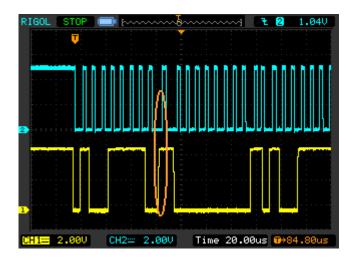

下面是使用 TCN75 时的 SDA 测得波形,从波形可以看到有应答信号(后面也有正常的温度数据输出)。下图中褐色标记的地方与上图中的应答信号对应。

注意下面红色标记的地方,低电平有一个小台阶,这是因为单片机和 TCN75 同时为低电平时会把电平拉的更低,那个向下的台阶对应的点就是 TCN75 应答有效的时间点(在时钟下降沿

输出应答信号和数据)。

而LM75A则没有应答信号,也没有温度数据输出,波形跟没有焊LM75A时完全相同。LM75A没有正确的应答,后面也没有温度输出。于是初步认为LM75A为假或有质量问题。

但也有另一种可能,就是芯片已经损坏。电压超过额定电压烧毁芯片? LM75A 支持2.7-5.5V 电压。静电击穿? LM75A 可以抗 2kV 静电,即使有失效也只能是偶尔有,绝不会是这样大规模的失效。电平冲突? 从课本或其它资料里我们看到单片机的输出是一个 NMOS 加一个弱上拉电阻的结构。而 LM75A 只有数据脚会有输出,不过,数据脚又是 OD 输出。不会出现电平冲突的啊!

为进一步调查原因,我们又从其他厂商处进了三个不同批次的LM75A,经验证有又一个 批次中的两片不能用,另两个批次可以用。这似乎更加迷惑。不过,这次测量有了新的发现:

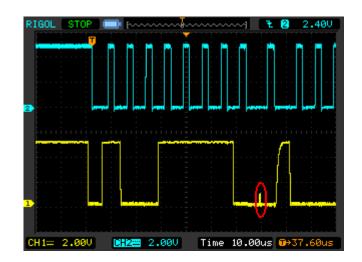

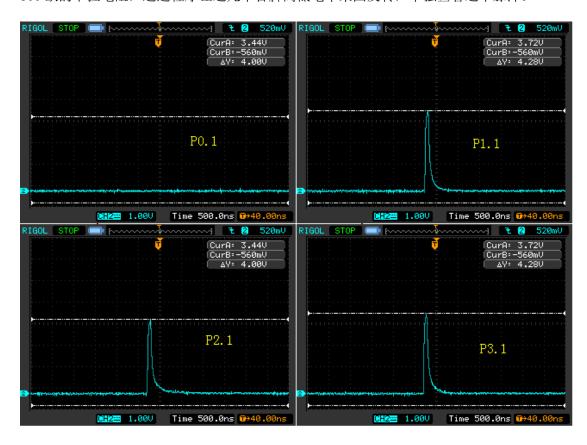

考虑到电平冲突的微小可能性,我在单片机和 LM75A 的数据线之间串了一个 33 欧的电阻,再测量单片机数据输出脚信号,看到了上面红色标记处的半高窄脉冲。这个脉冲所处的位置就是单片机数据线输出由 0 向 1 跳转的时间点,而在此前,LM75A 数据线此前已经输出低电平信号。理论上,这个脉冲应当是没有的。虽然示波器平时总出故障,但经过试验测试,发现这个脉冲不是示波器开玩笑,而是确实存在的。在 P0.1、P1.1、P2.1、P3.1 口上均加300 欧的下拉电阻,通过程序让这几个管脚高低电平来回反转,单独查看这个脉冲。

P0 口即使触发电平调到 520mV 也一直没有触发沿,因为 P0 口作为普通 I0 时没有上拉电阻,从效果看是一个等效的 0D 输出,所以不会有窄脉冲出现。而 P1、P2、P3 口都有一个窄脉冲,从波形上看,脉冲的高度为 3.7V 左右,脉冲宽度为 150ns。因为我们的示波器采样为 400MS/s,带宽也只有 25M,所以我们能看到的这个脉冲是存在严重失真的,估计实际脉冲峰值应能超过 4V,而且实际脉冲宽度要比 150ns 更小。这个脉冲是怎么出来的?这个

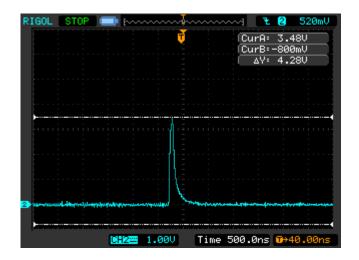

脉冲是SM5964独有的还是51系列单片机都有的?我找了一片ATMEL的AT89C55也测了一遍,同样测量到了几乎相同的脉冲,下面只给出AT89C55的 P3.1 脚测到的对应波形:

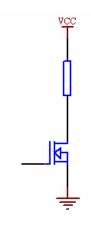

下面是常见资料里单片机管脚的输出结构(上拉电阻+NMOSFET):

如果真是上面的结构,上拉电阻至少要在 50k 以上,绝不会出现那样的正脉冲的。于是推测单片机的输出是一个 CMOS 结构,低电平向高电平的跳转过程是: 1) 将 NMOS 关闭; 2) 开启 PMOS; 3) 再通过控制 PMOS 的栅极电压(可能利用恒流源)来使 PMOS 等效为一个比较大的上拉电阻。从 2 到 3 的过程就是这个脉冲产生的过程。在这个过程中,如果 LM75A 输出有一个低电平(0D 门),那么瞬间会形成一个"图腾柱"结构,有一个很大的电流。这个电流持续时间比较短,TCN75 可以承受,不过,有些批次的 LM75A 就没有办法承受,所以数据脚引线(Core to Pin)熔断或 NMOSFET 失效断路。这点跟失效的 LM75A 数据线等同开路的测试结果很吻合。

这很可能是工艺改良引起的。随着工艺的改良,芯片从核到引脚的引线越来越细,硅片刻蚀精度的提高也使单个门占用的面积越来越小,所以抗瞬态大电流的能力变弱。

至于为什么采用这种结构,可能是受早期电阻集成工艺的影响(早期 MOSFET 实现起来比斯一个电阻要容易的多,用 MOS 管代替电阻是集成工艺中的一种重要方法);也有可能是为补偿上升沿,使上升沿更陡些,不过,这种可能性比较小。至于其真正原因暂时无从考证。因为工作原因,没有对其他 51 系列单片机进行测量,不知道是不是所有的 51 系列单片机都是这样。

因为受示波器限制,所以没有办法测量到这个脉冲的实际峰值高度和宽度,也就没有办法确定那个瞬态电流的大小。要想看到比较真实的脉冲,至少要用带宽在 100M 以上,采样速率在 200MS/s 以上的示波器。从这点可以看到,虽然我们的单片机系统数据 I0 最高频率只有 1MHZ (IIC 数据只有几 kHz),但是看这个 100ns 左右的脉冲要用到 100M 带宽的示波器。这就是传说中的"低速未必低频"。

也许之后你不会再说一个 25M 带宽的示波器能满足单片机开发需求了^ ^

## 注:

为避免该类事故再次发生, 51 系列单片机在应用到 IIC 接口时, 数据线上要注意串一个 100 欧左右的电阻。

## (补记:)

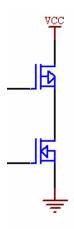

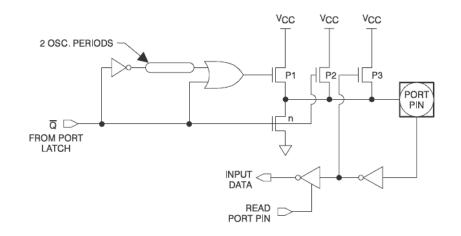

前段时间将该笔记发到网上,有朋友看到,告知了该脉冲发生的原因,并发给我一份51的硬件手册。下面是 P1 口和 P3 口真正的 I0 结构图:

其输出结构确实是类似 CMOS 的结构,当输出为 0 时,NMOSFET 导通,输出低电平;从 0 向 1 跳转过程中,P1 会导通 2 个时钟周期,这是为提高沿的上升速度。P1 的导通电流是 P3 导通电流的 100 倍,应当可以达到 100mA 左右(厂家及工艺不同会有一些差异)。P2 的导通电流只有 P3 的 1/10,使用 P2 是为稳定高电平——因为 I0 脚的低电平毛刺经反相器能关断 P3,此时由 P2 提供微弱电流。通常的高电平输出主要是 P3 导通提供的电流。而从 0 向 1 跳转过程中,短时间内 P1 导通导致器件烧毁。从结构上看,连续的写 1 不会出现该窄脉冲,与实验测试结果吻合。(段中 P1、P2、P3 指上图中的 PMOSFET。)

另外一位朋友看到这篇笔记后做了实验,将观察到的实现结果告诉给我,下面是他的测量设备信息及测量结果:

示波器采样频率 1GS/s, 带宽 100M。

单片机为 AT89C51ED2, 下拉电阻 330 欧姆。

脉冲幅值为 4.40V, 宽度为 100nS。上升时间 20nS, 下降时间 30nS。

这个测量结果比较真实,从实验结果可以推测这位朋友使用的是 24M 晶振,那么真实脉冲宽度比 100ns 还要略小些(考虑下降沿比上升沿慢,实际宽度应为 90ns 左右),而且会有更高一些的峰值(从能量关系可以算出实际峰值要略超过 4.6V)。按 5V 供电,脉冲高度为 4.6V 计算的话,这个 PMOS 的导通电阻只有 330/(4.6/(5-4.6)) = 29 欧。如果 LM75A 的 0D 门 NMOSFET 导通电阻为 21 欧,那么电流会达到 100mA,即使时间只有 80ns,仍足以对芯片造成危协。以前我们也遇到过 IIC 接口 AD 芯片工作不稳定的问题,也是这个原因。

这种 70 年代的 I0 结构,在 30 多年后的今天终于导致新问题的发生,也许这是那些设计 51 芯片的工程师们当时没有预料到的。

文中如有谬误,还望告知◎

邮箱: zjd01@eyou.com