# **SONiX 8-Bit Micro-Controller**

SONIX reserves the right to make change without further notice to any products herein to improve reliability, function or design. SONIX does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. SONIX products are not designed, intended, or authorized for us as components in systems intended, for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SONIX product could create a situation where personal injury or death may occur. Should Buyer purchase or use SONIX products for any such unintended or unauthorized application. Buyer shall indemnify and hold SONIX and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use even if such claim alleges that SONIX was negligent regarding the design or manufacture of the part.

# **AMENDENT HISTORY**

| Version  | Date      | Description                                                                                         |

|----------|-----------|-----------------------------------------------------------------------------------------------------|

| VER 1.90 | Sep. 2002 | V1.90 first issue                                                                                   |

| VER 1.93 | Feb. 2003 | Change the description of ADD M,A instruction from " $M \leftarrow M+A$ " to " $M \leftarrow A+M$ " |

| VER 1.94 | Jul. 2004 | 1. Separate instruction table into two tables.                                                      |

|          |           | 2. Add PUSH/POP instruction description.                                                            |

|          |           | 3. Remove the instruction cycle description in each instruction description.                        |

# **Table of Content**

| 1 OVERVIEW                                                | 5  |

|-----------------------------------------------------------|----|

|                                                           | J  |

| 2                                                         |    |

| INSTRUCTION SET TABLE                                     | 6  |

| TABLE I: FOR SN8P1XXX (FOUR CLOCKS PER INSTRUCTION CYCLE) |    |

| TABLE II: FOR SN8P2XXX (ONE CLOCK PER INSTRUCTION CYCLE)  |    |

| INSTRUCTION DESCRIPTION                                   | 10 |

| DATA TRANSFER INSTRUCTION                                 |    |

| MOV – Memory Read / Write Instruction                     |    |

| BOMOV – BANK 0 Memory Read / Write Instruction            |    |

| XCH – Data Exchange for All Area Memory                   |    |

| B0XCH – Data Exchange for BANK 0 Memory                   |    |

| MOVC – Read Data from ROM                                 |    |

| ARITHMETIC INSTRUCTION                                    |    |

| ADC – Add with Carry                                      |    |

| ADD – Add only                                            |    |

| B0ADD – Add with BANK 0 Memory                            |    |

| SBC – Subtract with Carry                                 |    |

| SUB – Subtract only                                       |    |

| DAA –Decimal-Adjust accumulator                           |    |

| MUL – Multiply Unsigned                                   |    |

| LOGIC INSTRUCTION                                         |    |

| AND – Logical AND                                         |    |

| OR – Logical OR                                           |    |

| XOR – Logical XOR                                         |    |

| PROCESS INSTRUCTION                                       |    |

| SWAP & SWAPM – Memory high/low Nibble Exchange            |    |

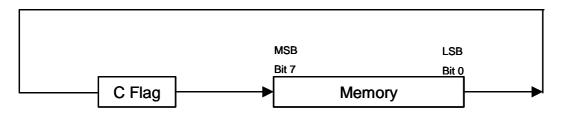

| RLC & RLCM – Memory Left Rotation                         |    |

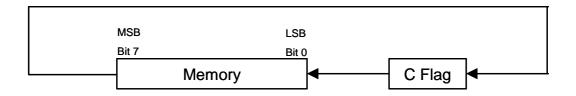

| RRC & RRCM – Memory Right Rotation                        |    |

| CLR – Clear                                               |    |

| BCLR & BOBCLR – Bit Clear                                 |    |

| BSET & BOBSET – Bit Set                                   |    |

| BRANCH INSTRUCTION                                        |    |

| CMPRS – Compare                                                | 31 |

|----------------------------------------------------------------|----|

|                                                                |    |

| INCS & INCMS – Increment and Skip on Zero                      |    |

| DECS & DECMS – Decrement and Skip on Zero                      |    |

| BTSO & BOBTSO – Bit Test 0                                     |    |

| BTS1 & B0BTS1 – Bit Test 1                                     |    |

| JMP – Jump                                                     |    |

| CALL – Call Procedure                                          |    |

| MISCELLANEOUS INSTRUCTION                                      |    |

| RET – Return from Call Procedure                               |    |

| RETI – Return from Interrupt                                   |    |

| NOP – No Operation                                             | 40 |

| PUSH – Save Some System Registers for SN8P1XXX and SN8P270XA   |    |

| PUSH – Save A and PFLAG for SN8P260X                           |    |

| POP – Restore Some System Registers for SN8P1XXX and SN8P270XA |    |

| POP – Restore A and PFLAG for SN8P260X                         | 44 |

# 1 OVERVIEW

This Manual contains detailed information and programming examples for each instruction of SONiX 8-Bit MCU series instruction set. Information is arranged in a consistent format to improve readability and for use as a quick-reference resource for application programmers.

The information elements of the instruction description format are as follows:

- Instruction name (mnemonic)

- Full instruction name

- Operand overview

- Source/destination format of the instruction operand

- Textual description of instructions

- Programming examples to shoe how the instruction is used

# **2** INSTRUCTION SET TABLE

# Table I: For SN8P1XXX (Four clocks per instruction cycle)

| Field | Mnem         | onic | Description                                                                           | С                             | DC | Ζ  | Cycle |

|-------|--------------|------|---------------------------------------------------------------------------------------|-------------------------------|----|----|-------|

|       | MOV          | A,M  | $A \leftarrow M$                                                                      | -                             | -  |    | 1     |

| М     | MOV          | M,A  | $M \leftarrow A$                                                                      | -                             | -  | -  | 1     |

| 0     | B0MOV        | A,M  | $A \leftarrow M (bnak 0)$                                                             | -                             | -  |    | 1     |

| V     | B0MOV        | M,A  | $M (bank 0) \leftarrow A$                                                             | -                             | -  | -  | 1     |

| Е     | MOV          | A,I  | A←I                                                                                   | -                             | -  | -  | 1     |

|       | <b>B0MOV</b> | M,I  | $M \leftarrow I$ , (M = only for Working registers R, Y, Z, RBANK & PFLAG)            | -                             | -  | -  | 1     |

|       | XCH          | A,M  | $A \leftarrow \rightarrow M$                                                          | -                             | -  | -  | 1     |

|       | B0XCH        | A,M  | $A \leftarrow \rightarrow M (bank 0)$                                                 | -                             | -  | -  | 1     |

|       | MOVC         |      | $R, A \leftarrow ROM [Y,Z]$                                                           | -                             | -  | -  | 2     |

|       | ADC          | A,M  | $A \leftarrow A + M + C$ , if occur carry, then C=1, else C=0                         |                               |    |    | 1     |

| А     | ADC          | M,A  | $M \leftarrow A + M + C$ , if occur carry, then C=1, else C=0                         |                               |    |    | 1     |

| R     | ADD          | A,M  | $A \leftarrow A + M$ , if occur carry, then C=1, else C=0                             |                               |    |    | 1     |

| Ι     | ADD          | M,A  | $M \leftarrow A + M$ , if occur carry, then C=1, else C=0                             |                               |    |    | 1     |

| Т     | B0ADD        | M,A  | $M$ (bank 0) $\leftarrow$ A + M (bank 0), if occur carry, then C=1, else C=0          |                               |    |    | 1     |

| Н     | ADD          | A,I  | A $\leftarrow$ A + I, if occur carry, then C=1, else C=0                              |                               |    |    | 1     |

| М     | SBC          | A,M  | $A \leftarrow A - M - /C$ , if occur borrow, then C=0, else C=1                       |                               |    | V  | 1     |

| Е     | SBC          | M,A  | $M \leftarrow A - M - /C$ , if occur borrow, then C=0, else C=1                       |                               |    | √. | 1     |

| Т     | SUB          | A,M  | $A \leftarrow A - M$ , if occur borrow, then C=0, else C=1                            | V                             |    | V  | 1     |

| Ī     | SUB          | M,A  | $M \leftarrow A - M$ , if occur borrow, then C=0, else C=1                            | $\sqrt{\sqrt{\sqrt{\gamma}}}$ |    |    |       |

| C     | SUB          | A,I  | $A \leftarrow A - I$ , if occur borrow, then C=0, else C=1                            |                               |    |    | 1     |

| Ũ     | DAA          | ,.   | To adjust ACC's data format from HEX to DEC.                                          |                               | -  | _  | 1     |

|       |              |      | R, A $\leftarrow$ A * M, The LB of product stored in Acc and HB stored in R register. | ,                             |    | 1  |       |

|       | MUL          | A,M  | ZF affected by Acc.                                                                   | -                             | -  |    | 2     |

|       | AND          | A,M  | $A \leftarrow A \text{ and } M$                                                       | -                             | -  |    | 1     |

| L     | AND          | M,A  | $M \leftarrow A \text{ and } M$                                                       | _                             | -  |    | 1     |

| Ō     | AND          | A,I  | $A \leftarrow A \text{ and } I$                                                       | _                             | _  | V  | 1     |

| G     | OR           | A,M  | $A \leftarrow A \text{ or } M$                                                        | -                             | -  | V  | 1     |

| Ī     | OR           | M,A  | $M \leftarrow A \text{ or } M$                                                        | -                             | -  | √. | 1     |

| C     | OR           | A,I  | $A \leftarrow A \text{ or } I$                                                        | -                             | -  | V  | 1     |

|       | XOR          | A,M  | $A \leftarrow A \text{ xor } M$                                                       | -                             | _  | V  | 1     |

|       | XOR          | M,A  | $M \leftarrow A \text{ xor } M$                                                       | -                             | -  | V  | 1     |

|       | XOR          | A,I  | $A \leftarrow A \text{ xor } I$                                                       | -                             | -  | √. | 1     |

|       | SWAP         | M    | $A (b3 \sim b0, b7 \sim b4) \leftarrow M(b7 \sim b4, b3 \sim b0)$                     | -                             | _  | -  | 1     |

| Р     | SWAPM        |      | $M(b3 \sim b0, b7 \sim b4) \leftarrow M(b7 \sim b4, b3 \sim b0)$                      | -                             | -  | -  | 1     |

| R     | RRC          | M    | $A \leftarrow RRC M$                                                                  |                               | -  | -  | 1     |

| 0     | RRCM         | M    | $M \leftarrow RRC M$                                                                  |                               | -  | -  | 1     |

| C     | RLC          | M    | $A \leftarrow RLC M$                                                                  |                               | -  | -  | 1     |

| E     | RLCM         | M    | $M \leftarrow RLC M$                                                                  |                               | _  | -  | 1     |

| S     | CLR          | M    | $M \leftarrow 0$                                                                      | -                             | -  | -  | 1     |

| S     | BCLR         | M.b  | $M \leftarrow 0$                                                                      | _                             | _  | -  | 1     |

|       | BSET         | M.b  | $M.b \leftarrow 0$                                                                    | -                             | -  | -  | 1     |

|       | 2021         | M.b  | $M.b \leftarrow 1$<br>M(bank 0).b $\leftarrow 0$                                      | -                             | _  | _  | 1     |

|       | B0BCLR       |      |                                                                                       | -                             |    |    | 1     |

|       | BOBSET       | M.b  | $M(bank \ 0).b \leftarrow 1$                                                          | -                             | -  | -  | 1     |

| Field | Mnemor   | nic | Description                                                                            | С | DC    | Ζ | Cycle |

|-------|----------|-----|----------------------------------------------------------------------------------------|---|-------|---|-------|

|       | CMPRS A  | A,I | $ZF,C \leftarrow A - I$ , If $A = I$ , then skip next instruction                      |   | -     |   | 1 + S |

| В     | CMPRS A  | A,M | $ZF,C \leftarrow A - M$ , If $A = M$ , then skip next instruction                      |   | -     |   | 1 + S |

| R     | INCS N   | M   | $A \leftarrow M + 1$ , If $A = 0$ , then skip next instruction                         | - | -     | - | 1 + S |

| Α     | INCMS N  | M   | $M \leftarrow M + 1$ , If $M = 0$ , then skip next instruction                         | - | -     | - | 1 + S |

| Ν     | DECS N   | M   | $A \leftarrow M - 1$ , If $A = 0$ , then skip next instruction                         | - | -     | - | 1 + S |

| С     | DECMS N  | M   | $M \leftarrow M - 1$ , If $M = 0$ , then skip next instruction                         | - | -     | - | 1 + S |

| Н     | BTS0 N   | M.b | If $M.b = 0$ , then skip next instruction                                              | - | 1 + S |   |       |

|       | BTS1 N   | M.b | If $M.b = 1$ , then skip next instruction                                              | - | -     | - | 1 + S |

|       | BOBTSO N | M.b | If $M(bank 0).b = 0$ , then skip next instruction                                      | - | -     | - | 1 + S |

|       | BOBTS1 N | M.b | If $M(bank 0).b = 1$ , then skip next instruction                                      | - | -     | - | 1 + S |

|       | JMP      | d   | PC15/14 $\leftarrow$ RomPages1/0, PC13~PC0 $\leftarrow$ d                              | - | -     | - | 2     |

|       | CALL     | d   | Stack $\leftarrow$ PC15~PC0, PC15/14 $\leftarrow$ RomPages1/0, PC13~PC0 $\leftarrow$ d | - | -     | - | 2     |

|       | RET      |     | $PC \leftarrow Stack$                                                                  | - | -     | - | 2     |

| М     | RETI     |     | $PC \leftarrow Stack$ , and to enable global interrupt                                 | - | -     | - | 2     |

| Ι     | RETLW    |     | $PC \leftarrow Stack$ , and to load a value by $PC+A$                                  | - | -     | - | 2     |

| S     | PUSH     |     | To push working registers (080H~087H) into buffers                                     | - | -     | - | 1     |

| С     | POP      |     | To pop working registers (080H~087H) from buffers                                      |   |       |   | 1     |

|       | NOP      |     | No operation                                                                           | - | -     | - | 1     |

#### <u>Remark</u>

- 1. The "M" is memory including system registers and user defined memory.

- 2. If branch condition is true then "S = 0", otherwise "S = 1".

- 3. Any instruction that writes OSCM register will add an extra cycle.

- 4. One instruction cycle = 1/Fcpu

# Table II: For SN8P2XXX (One clock per instruction cycle)

| Field | Mnem                                                   | onic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Description                                                                | С                                                     | DC | Ζ            | Cycle |

|-------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------|----|--------------|-------|

|       | MOV                                                    | A,M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A \leftarrow M$                                                           | -                                                     | -  |              | 1     |

| М     | MOV                                                    | M,A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $M \leftarrow A$                                                           | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 1  |              |       |

| 0     | <b>B0MOV</b>                                           | A,M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A \leftarrow M (bnak 0)$                                                  | -                                                     | -  |              | 1     |

| V     | <b>B0MOV</b>                                           | M,A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | M (bank 0) $\leftarrow$ A                                                  | -                                                     | -  | -            | 1     |

| Е     | MOV                                                    | A,I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A←I                                                                        | -                                                     | -  | -            | 1     |

|       | <b>B0MOV</b>                                           | M,I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $M \leftarrow I$ , (M = Working registers, RBANK & PFLAG)                  | -                                                     | -  | -            | 1     |

|       | XCH                                                    | A,M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A \leftarrow \rightarrow M$                                               | -                                                     | -  | -            | 1+N   |

|       | B0XCH                                                  | A,M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A \leftarrow \rightarrow M (bank 0)$                                      | I                                                     | -  | I            | 1+N   |

|       | MOVC                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $R, A \leftarrow ROM [Y,Z]$                                                | -                                                     | -  | -            | 2     |

|       | ADC                                                    | A,M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A \leftarrow A + M + C$ , if occur carry, then C=1, else C=0              |                                                       |    |              | 1     |

| А     | ADC                                                    | M,A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $M \leftarrow A + M + C$ , if occur carry, then C=1, else C=0              |                                                       |    |              | 1+N   |

| R     | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                          |                                                       |    |              |       |

| Ι     | ADD                                                    | A,IA $\leftarrow$ IM,IM $\leftarrow$ I, (M = Working registers, RBANK & PFLAG)A,MA $\leftarrow \rightarrow$ MA,MA $\leftarrow \rightarrow$ M (bank 0)R, A $\leftarrow$ ROM [Y,Z]A,MA $\leftarrow A + M + C$ , if occur carry, then C=1, else C=0M,AM $\leftarrow A + M + C$ , if occur carry, then C=1, else C=0A,MA $\leftarrow A + M$ , if occur carry, then C=1, else C=0M,AM $\leftarrow M + A$ , if occur carry, then C=1, else C=0M,AM $\leftarrow M + A$ , if occur carry, then C=1, else C=0A,AM (bank 0) $\leftarrow$ M (bank 0) + A, if occur carry, then C=1, else C=0A,IA $\leftarrow A + H$ , if occur carry, then C=1, else C=0A,IA $\leftarrow A + H$ , if occur borrow, then C=0, else C=1M,AM $\leftarrow A - M - /C$ , if occur borrow, then C=0, else C=1M,AM $\leftarrow A - M$ , if occur borrow, then C=0, else C=1A,MA $\leftarrow A - M$ , if occur borrow, then C=0, else C=1M,AM $\leftarrow A - M$ , if occur borrow, then C=0, else C=1To adjust ACC's data format from HEX to DEC.A,MR, $A \leftarrow A + M$ , The LB of product stored in Acc and HB stored in R regiZF affected by Acc.A,MA $\leftarrow A$ and MA,AM $\leftarrow A$ or MA,AM $\leftarrow A$ or MA,AA $\leftarrow A$ and MA,AA $\leftarrow A$ or MA, |                                                                            |                                                       |    |              | 1+N   |

| Т     | B0ADD                                                  | M,A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | M (bank 0) $\leftarrow$ M (bank 0) + A, if occur carry, then C=1, else C=0 |                                                       |    |              | 1+N   |

| Н     | ADD                                                    | A,I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A \leftarrow A + I$ , if occur carry, then C=1, else C=0                  |                                                       |    |              | 1     |

| М     | SBC                                                    | A,M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A \leftarrow A - M - /C$ , if occur borrow, then C=0, else C=1            |                                                       |    |              | 1     |

| Е     | SBC                                                    | M,A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $M \leftarrow A - M - /C$ , if occur borrow, then C=0, else C=1            |                                                       |    |              | 1+N   |

| Т     | SUB                                                    | A,M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A \leftarrow A - M$ , if occur borrow, then C=0, else C=1                 |                                                       |    |              | 1     |

| Ι     |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                            |                                                       |    |              | 1+N   |

| С     | SUB                                                    | A,I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A \leftarrow A - I$ , if occur borrow, then C=0, else C=1                 |                                                       |    |              | 1     |

|       | DAA                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | To adjust ACC's data format from HEX to DEC.                               |                                                       | -  | -            | 1     |

|       | MUL                                                    | A,M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            | -                                                     | -  | $\checkmark$ | 2     |

|       | AND                                                    | A,M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A \leftarrow A \text{ and } M$                                            | -                                                     | -  |              | 1     |

| L     | AND                                                    | M,A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $M \leftarrow A and M$                                                     | -                                                     | -  |              | 1+N   |

| 0     | AND                                                    | A,I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A \leftarrow A \text{ and } I$                                            | -                                                     | -  |              | 1     |

| G     | OR                                                     | A,M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A \leftarrow A \text{ or } M$                                             | -                                                     | -  |              | 1     |

| Ι     | OR                                                     | M,A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $M \leftarrow A \text{ or } M$                                             | -                                                     | -  |              | 1+N   |

| С     | OR                                                     | A,I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A \leftarrow A \text{ or } I$                                             | -                                                     | -  |              | 1     |

|       | XOR                                                    | A,M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A \leftarrow A \text{ xor } M$                                            | -                                                     | -  |              | 1     |

|       | XOR                                                    | M,A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $M \leftarrow A \operatorname{xor} M$                                      | -                                                     | -  |              | 1+N   |

|       | XOR                                                    | A,I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $A \leftarrow A \text{ xor } I$                                            | -                                                     | -  |              | 1     |

|       | SWAP                                                   | М                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A (b3~b0, b7~b4) $\leftarrow$ M(b7~b4, b3~b0)                              | -                                                     | -  | -            | 1     |

| Р     | SWAPM                                                  | М                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            | -                                                     | -  | -            | 1+N   |

| R     | RRC                                                    | М                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            |                                                       | -  | -            | 1     |

| 0     | RRCM                                                   | М                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $M \leftarrow RRC M$                                                       |                                                       | -  | -            | 1+N   |