## PowerPCB 转 SCH 教程

本文以 PowerPCB 提供的 Pwrdemoa.pcb 为例进行说明。

- 1. 打开 PCB 图 ,选择菜单 File Report , 文件类型选 PowerPCB V3.0 Format Netlist ,将文件另存为 Pwrdemoa.ASC。

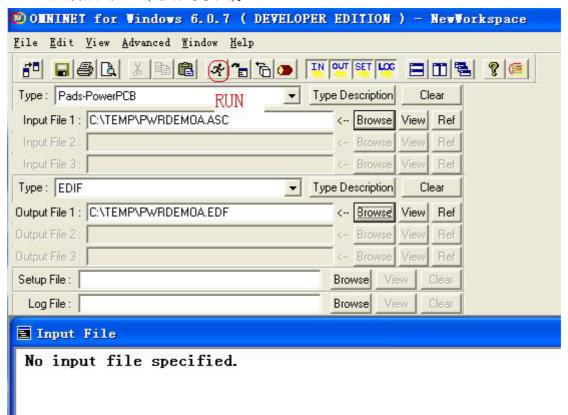

- 2.启动程序 Omninet for Windows ,输入文件类型(Type)选 Pads-PowerPCB , Input File 1 里用 Browse 指定网络表文件的位置。

输出文件类型(Type)选 EDIF。Output File 1 指定输出文件的文件名和路径。 然后点击 Run(跑动的小人)。

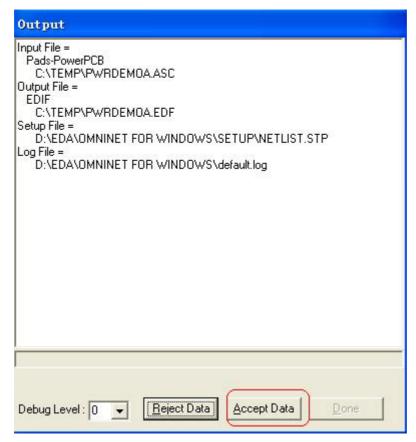

系统弹出一个输出窗口,

点击 Accept Data。完成后点击"确定", 再点击"Done"关闭输出窗口。退出 Omninet for Windows。

3. 修改 EDIF 网表文件,非常麻烦且容易出错的部分。下面是网络表的一部分;

```

C_COLON_BSLTEMP_BSLPWRDEMOA_DOTEDF

(edif

(rename

"C:\TEMP\PWRDEMOA.EDF")

(edifVersion 2 0 0)

(edifLevel 0)

(keywordMap (keywordLevel 0))

(library MAIN_LIB

(edifLevel 0)

(technology

(numberDefinition

(scale 1 (e 1 -6)(unit distance)))

)

(cell &6167 (cellType generic)

(view NetlistView (viewType netlist)

(interface

```

```

(cell &6167 (cellType generic)

(view NetlistView (viewType netlist)

(interface

(port &1)

(port &2)

(port &3)

(port &4)

(port &5)

(port &6)

(port &7)

(port &10)

(port &13)

(port &14)

(port &15)

(port &16)

(port &17)

(port &18)

(port &19)

(port &20)

)

)

(cell &68HC68R2 (cellType generic)

(view NetlistView (viewType netlist)

(interface

(port &1)

(port &2)

(port &3)

(port &4)

(port &5)

(port &6)

(port &7)

(port &8)

)

)

(cell &68HC68R2 (cellType generic)

(view NetlistView (viewType netlist)

(interface

)

```

```

(cell (rename NE555_MINUSSO "NE555-SO") (cellType generic)

(view NetlistView (viewType netlist)

(interface

)

(cell (rename R1_FSL4W "R1/4W") (cellType generic)

(view NetlistView (viewType netlist)

(interface

)

(cell (rename R1_FSL4W "R1/4W") (cellType generic)

(view NetlistView (viewType netlist)

(interface

(port &1)

(port &2)

)

)

检查一下有(cell.....标记的行,特别要注意红色字体部分,其 Interface 部分

为空,在这个 cell 标记的前面或后面又有一个 cell 行,其 Interface 部分包含有

(port &1)

(port & 2)

```

等内容。就是说每种器件出现了两个 cell 定义。

现在要做的就是将无 port 内容的 cell 标记删除(上述 EDIF 文件中红色字体部分)。PCB 板中有多少种 Part Type,就需要删除多少 Cell 标记,还要注意不要把有 port 内容的那些行删掉了。多删了或者少删了都会造成网络不完整,从而丢失信息。

将修改后的 EDIF 文件存盘。

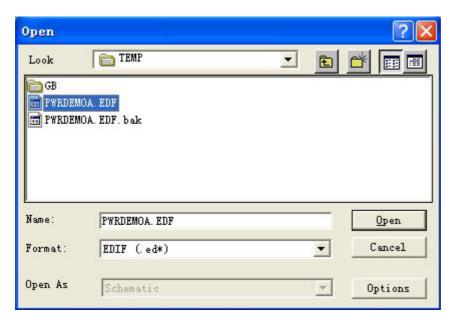

4.启动 E-Studio 软件,打开第3步保存的 EDIF 文件。

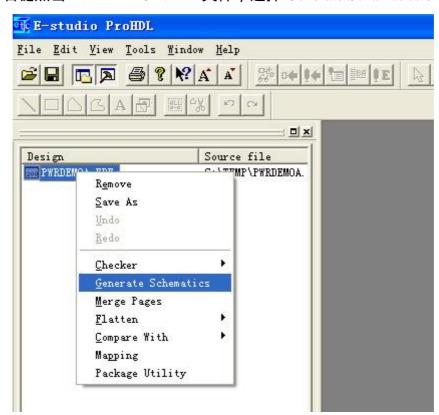

5. 右键点击 PWRDEMOA.EDF 文件,选择 Generate Schamatics:

系统弹出窗口。

## 点击确定。

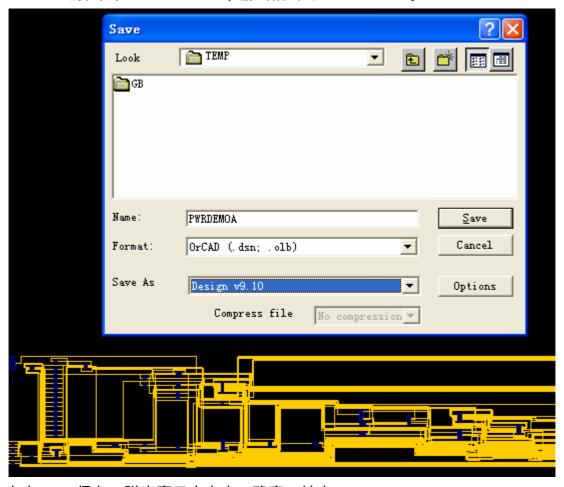

6. 选择菜单 File - Save As,输出格式选 ORCAD 9.10。

点击 Save 保存。弹出窗口中点击"确定"结束。

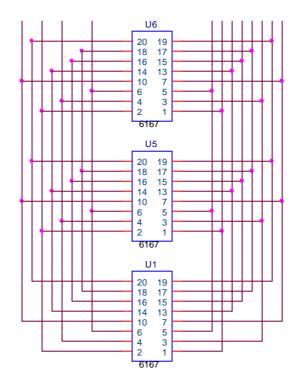

生成的原理图已经可以在 ORCAD 中打开了。图纸显得特别长。如果 PCB 比较复杂,可能会出现原理图太大,以致软件都没法处理的情况。下图只是原理图的一部分。

6.在 ORCAD 中打开生成的原理图,启动 PCBNavigator,打开 ITC 连接 PowerPCB。选择菜单 PCB->Compare Netlist with PCB,生成的报告文件如下:

\*PADS-ECO-V3.0-MILS\*

$*REMARK* \quad old \ file: D:\padspwr\Files\ecogtmp0.asc$

\*REMARK\* new file: C:\TEMP\pwrdemoa.asc

\*REMARK\* created by ECOGEN (Version 6.0g) on 2004-10-8 21:39:40

## PART DIFFERENCES

-----

| OLD DESIGN              | NE      | NEW DESIGN      |  |

|-------------------------|---------|-----------------|--|

| Ref-des Part-type:Decal | Ref-des | Part-type:Decal |  |

| P2 CON\60P\100\ED       | P2      | ED              |  |

| J1 CON\RIB14HL          | J1      | RIB14HL         |  |

| R1 R1/4W                | R1      | 4W              |  |

| R10 R1/4W               | R10     | 4W              |  |

| R11 R1/4W               | R11     | 4W              |  |

| R12 R1/4W               | R12     | 4W              |  |

| R14 R1/4W               | R14     | 4W              |  |

| R16 R1/4W               | R16     | 4W              |  |

| R2 R1/4W                | R2      | 4W              |  |

| R5 R1/4W                | R5      | 4W              |  |

| R6 R1/4W                | R6      | 4W              |  |

| R7 R1/4W                | R7      | 4W              |  |

| R8 R1/4W                | R8      | 4W              |  |

| R9 R1/4W                | R9      | 4W              |  |

|                         |         |                 |  |

| NET DIFFERENCES                  |            |

|----------------------------------|------------|

| OLD DESIGN                       | NEW DESIGN |

| SWAPPED GATE DIFFERENCES         |            |

| OLD DESIGN                       | NEW DESIGN |

| SWAPPED PIN DIFFERENCES          |            |

| OLD DESIGN                       | NEW DESIGN |

| UNMATCHED NET PINS IN OLD DESIGN |            |

| UNMATCHED NET PINS IN NEW DESIGN |            |

| ATTRIBUTE DIFFERENCES            |            |

可以看出,除了器件类型中包含有斜杠(不论正反)被改名外,网络表没有任何差

Old Value

New Value

[ OLD DESIGN Parent -> NEW DESIGN Parent ]

异。 如果要求完美,可以对照 PCB 图将原理图中的器件型号再改回去,这样就

如果没有 PCBNavigator,可以用 ORCAD 生成 PADSPCB 格式的网络表,在 PowerPCB 的 Tools 菜单的 Compare/ECO Tools 中进行比较,第一个文件选当前设计文件,第二个文件选 ORCAD 生成的 ASCII 网表文件,其比较结果是一样

到此, PowerPCB 转 ORCAD 原理图结束。

Attribute Level

的。

Attribute Name

能实现原理图与 PCB 的完全对应。

需要说明的是,这样的转换对于 PCB 上元件较少的情况可能好用,但如果 PCB 上元件很多,则转换出来的原理图非常庞大,网络连接极其复杂,它没有层次、总线概念,也不会分成多张子图,所有网络是全部连接的,要能看懂可能还是比较困难。

另外, PCB 中没有连接的管脚在转换出来的原理图上不再存在,可能会出现有些器件管脚数不对的情况。若要修改原理图,必须修改生成的器件符号。

还有一点不完善的地方是器件的封装信息没有了,必须重新填写。不过用 ORCAD 做原理图有个优势,就是不写封装,生成网络表时会以器件的 Value 作为封装,不影响网络表生成。