INCH-POUND

MIL-PRF-28750E 28 October 2008 SUPERSEDING MIL-PRF-28750D 1 February 1999

#### PERFORMANCE SPECIFICATION

## RELAYS, SOLID STATE, GENERAL SPECIFICATION FOR

This specification is approved for use by all Departments and Agencies of the Department of Defense.

## 1. SCOPE

1.1 <u>Scope</u>. This specification covers the general requirements for hermetically sealed or encapsulated solid-state relays (SSR's) (see .1), incorporating semiconductor, microelectronic, and passive circuit devices.

## 1.2 SSR classification.

- a. <u>Class I (discrete) construction</u>: SSR utilizing this type of technology, employs only discrete type components, which can be nonhermetically sealed. The completed SSR is hermetically sealed.

- b. <u>Class II (hybrid) construction</u>: SSR utilizing this type of technology, employs chip (die) and wire bond technology. The completed SSR is hermetically sealed.

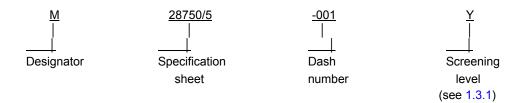

- 1.3 Part or Identifying Number (PIN). The PIN will consist of the designator, the basic number of the specification sheet, an assigned dash number (see .1), and a screening level that indicates the level of quality and reliability (see 1.3.1).

1.3.1 <u>Screening level</u>. The screening level is identified by a single letter, Y or W. Use screening level Y for high reliability applications (see .8); and screening level W for general purpose applications (see .4.4.5e and .6.1.2b).

Comments, suggestions or questions on this document should be addressed to Defense Supply Center Columbus, ATTN: VAT, Post Office Box 3990, Columbus, OH 43218-3990, or emailed to (relay@dla.mil). Since contact information can change, you may want to verify the currency of this address information using the ASSIST Online database at http://assist.daps.dla.mil.

### 2. APPLICABLE DOCUMENTS

2.1 <u>General</u>. The documents listed in this section are specified in sections 3 and of this specification. This section does not include documents cited in other sections of this specification or recommended for additional information or as examples. While every effort has been made to ensure the completeness of this list, document users are cautioned that they must meet all specified requirements of documents cited in sections and of this specification, whether or not they are listed.

### 2.2 Government documents.

2.2.1 <u>Specifications, standards, and handbooks</u>. The following specifications, standards, and handbooks form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

### FEDERAL STANDARD

FED-STD-H28 - Screw-Thread Standards for Federal Services.

#### DEPARTMENT OF DEFENSE SPECIFICATIONS

| MIL-DTL-17    | - | Cable, Radio Frequency, Flexible and Semirigid, General Specification for. |

|---------------|---|----------------------------------------------------------------------------|

| MIL-PRF-19500 | - | Semiconductor Devices, General Specification For.                          |

| MIL-PRF-38534 | - | Hybrid Microcircuits, General Specification For.                           |

# **DEPARTMENT OF DEFENSE STANDARDS**

| MIL-STD-202  | - | Test Method Standard, Electronic and Electrical Component Parts.                      |

|--------------|---|---------------------------------------------------------------------------------------|

| MIL-STD-750  | - | Test Methods for Semiconductor Devices.                                               |

| MIL-STD-790  | - | Standard Practice for Established Reliability and High Reliability Qualified Products |

|              |   | List (QPL) Systems for Electrical, Electronic, and Fiber Optic Parts Specifications.  |

| MIL-STD-883  | - | Test Method Standard Microelectronics.                                                |

| MIL-STD-1285 | - | Marking of Electrical and Electronic Parts.                                           |

(Copies of these documents are available online at <a href="http://assist.daps.dla.mil/quicksearch/">http://assist.daps.dla.mil/quicksearch/</a> or <a href="http://assist.daps.dla.mil/">http://assist.daps.dla.mil/</a> or from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.3 <u>Non-Government publications</u>. The following documents form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

## ELECTRONIC INDUSTRIES ASSOCIATION (EIA)

EIA-557 - Statistical Process Control Systems.

(Applications for copies are available online at <a href="http://www.eia.org/">http://www.eia.org/</a> or should be addressed to the ECA/EIA Standards and Technology, 2500 Wilson Boulevard, Arlington, VA 22201-3834).

## INSTITUTE OF ELECTRICAL AND ELECTRONIC ENGINEERS (IEEE)

IEEE-315A - Graphic Symbols for Electrical and Electronics Diagrams.

(Applications for copies are available online at <a href="http://www.ieee.org/">http://www.ieee.org/</a> or should be addressed to the Institute of Electrical and Electronic Engineers, 445 Hoes Lane, P. O. Box 1331, Piscataway, NJ 08854-1331.)

2.4 Order of precedence. In the event of a conflict between the text of this document and the references cited herein (except for related specification sheets), the text of this document takes precedence, unless otherwise noted. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

## 3. REQUIREMENTS

- 3.1 <u>Specification sheets</u>. The individual item requirements shall be as specified herein and in accordance with the applicable specification sheet. In the event of conflict between requirements of this specification and the specification sheet, the latter shall govern.

- 3.2 <u>Qualification</u>. SSR's furnished under this specification shall be products which are authorized by the qualifying activity for listing on the applicable Qualified Products List (QPL) at the time of award of contract (see .4 and .3).

- 3.3 <u>Quality system.</u> The manufacturer shall establish and maintain a QPL system for parts covered by this specification. Requirements for this system are specified in MIL-STD-790. For class II SSR's, the manufacturer's QPL system shall also address the requirements of appendix A and the qualifying activity for this specification may use pre-existing certification of the manufacturing facility in accordance with MIL-PRF-38534 as an alternative. The manufacture shall also establish a component evaluations system as part of the MIL-STD-790 overall system in accordance with appendix B.

- 3.3.1 <u>Statistical process control (SPC)</u>. As part of the overall MIL-STD-790 QPL system, the manufacturer shall establish an SPC system that meets the requirements of EIA-557.

- 3.3.2 <u>Electrostatic discharge (ESD) control program</u>. As part of the overall MIL-STD-790 QPL system, the manufacturer shall establish and maintain an ESD control system. As a minimum, this plan must address the identification of ESD sensitive (ESDS) sub-components and end items, facilities, training, design protection, handling procedures, marking, cleaning, preservation, packaging, and verification.

- 3.4 <u>Materials</u>. Materials shall be as specified herein. However, when a definite material is not specified, a material shall be used which will enable the SSR's to meet the performance requirements of this specification. Materials used shall be self-extinguishing; and shall not support combustion, give off noxious gases in harmful quantities, give off

gases in quantities sufficient to cause explosion of sealed enclosures, cause contamination to any part of the SSR, or form current carrying tracks when subjected to any of the tests specified herein. The selection of materials shall be such as to provide maximum shelf life. After qualification, any change of parts or material shall be submitted to the Government qualifying activity for approval. Acceptance or approval of any constituent material shall not be construed as a guaranty of the acceptance of the finished product.

- 3.4.1 <u>Metals and plating</u>. Metals shall be of a corrosion-resistant type or shall be plated or treated to resist corrosion. Use of pure tin, plating or otherwise, is prohibited internally and externally (see .7.2b). Use of tin-lead finishes are acceptable provided that the minimum lead content is 3 percent.

- 3.5 <u>Circuit element requirements for class II SSR's</u>. The requirements for circuit elements shall be in accordance with appendix B.

- 3.6 Interface and physical dimensions. SSR's shall meet the interface and physical dimensions specified (see 3.1).

- 3.6.1 <u>Threaded parts</u>. All threaded parts shall be in accordance with FED-STD-H28. Where practical, all threads shall be in conformity with the coarse-thread series. The fine-thread series may be used only for applications that show a definite advantage through their use. Where a special diameter-pitch combination is required, the thread shall be of American National Form and of any pitch between 16 and 36, which is used in the fine-thread series. Terminal threads shall be class 2A and class 2B for external and internal threads, respectively.

- 3.6.2 <u>Envelope (case, cover, or enclosure)</u>. SSR's with metal cases shall be provided with means to permit assured contact to ground. The enclosure shall not be electrically connected to any terminal, except one provided specifically for grounding or as specified (see 3.1).

- 3.6.3 <u>Sealing process</u>. Sealed SSR's shall be dried, degassed, and backfilled (see 6.8) with an atmosphere and sealed by welding such that the requirements of this specification are met (see .9). Adjunct sealant, if used, shall comply with the following:

- Sealant shall not extend beyond 20 percent of the length of the exposed terminals above the glass meniscus.

- b. Trace color is permitted if it is a natural result of the sealant process.

- c. After curing, sealant shall form a permanent nonconductive, noncracking seal under all relay environments.

- 3.6.4 Mounting means. Mounting means shall be as specified (see 3.1).

- 3.6.4.1 <u>Socket</u>. Plug-in SSR's shall be so designed that the weight of the SSR will be supported, and the stability of the mounting will be provided by means other than the terminals.

- 3.6.5 Terminals (see .1). Terminals shall be as specified herein.

- 3.6.5.1 <u>Solder-lug terminals</u>. Solder-lug terminals shall be designed to accommodate two conductors, each rated to carry the maximum rated current of the contact or coil terminated.

- 3.6.5.2 Wire leads. Wire leads shall be as specified (see 3.1).

- 3.6.5.3 <u>Plug-in termination</u>. Plug-in terminations shall conform to the arrangements or dimensions and interfaces necessary for proper mating with the associated connectors or sockets as specified (see .1). The mounting arrangement of the SSR and its corresponding socket shall be so designed that the entire weight of the SSR will be suspended and the stability of its mounting will be provided by an auxiliary mounting means other than the electrical terminals of the socket (see .1). During qualification, SSR's, with plug-in terminals shall have electrical tests of section 4 and environmental tests of section 4 performed with the appropriate or specified socket or connector assembled to the SSR. For further guidance on lead finishes, see 6.7.2.

- 3.6.5.4 <u>Screw</u>. Screw terminals shall be supplied with one nut, capable of engaging the screw by at least three full threads, two flat washers and one lock washer. The size of screw thread and length shall be as specified (see 3.1). At least three full threads of the screw shall visibly protrude with all hardware tightened in place.

- 3.6.6 <u>Circuit diagram</u>. The circuit diagram as specified (see 3.1), shall be a terminal view. Circuit symbols shall be

- in accordance with IEEE-315A. For SSR's without an orientation tab, the circuit diagram as specified (see 3.1), shall be orientated so that when the SSR is held with the circuit diagram right side up as shown in the appropriate specification sheet (see .1), and rotated away from the viewer about a horizontal axis through the diagram until the header terminals face the viewer, then each terminal shall be in the location shown on the circuit diagram.

- 3.6.7 <u>Temperature</u>. Unless otherwise specified (see 3.1), the SSR shall operate satisfactorily throughout the temperature range of -55°C to +125°C, and shall not be damaged when stored at a temperature in the range of -55°C to +125°C.

- 3.6.8 <u>Package</u>. The outline dimensions of the package shall be as specified (see 3.1). In addition, the relay shall meet the following requirements.

- 3.6.8.1 <u>Class I.</u> Discrete technology SSR's supplied to this specification shall be sealed in glass, metal, or ceramic (or combination of these) packages. Adhesive or polymeric material shall not be used for package cover/lid attachment, seal, or repair. Use of any other package material shall require prior approval from the qualifying authority.

- 3.6.8.2 <u>Class II</u>. Hybrid technology SSR's supplied to this specification shall be hermetically sealed in glass, metal, or ceramic (or combinations of these) packages. No adhesive or polymeric materials shall be used for package lid attach (or seal) or repair. Flux shall not be used in the final sealing process. The minimum distance between the glass to metal seals and the package sealing surface for seam welded packages after final seal shall be .040 inch (1.02 mm) minimum.

- 3.6.8.3 <u>Internal water vapor content</u>. The internal water vapor content shall not exceed 5,000 parts per million at +100°C. Polymer impregnation or secondary seal (backfill, coating, or other uses of organic polymeric materials to effect, improve, or repair the seal) of the SSR package shall not be permitted.

- NOTE: Packages containing beryllia shall not be ground, sandblasted, machined, or have other operations performed on them which will produce beryllia or beryllium dust. Furthermore, beryllium oxide packages shall not be placed in acids that will produce fumes containing beryllium.

- 3.6.9 <u>Metals</u>. Metal surfaces shall be corrosion resistant or shall be plated or treated to resist corrosion and shall meet the requirements specified in .6.11.

- 3.6.10 Other materials. External parts, elements, or coatings including markings shall be non-nutrient to fungus and shall not blister, crack, outgas, soften, flow, or exhibit defects that adversely affect storage, operation, or environmental capabilities of SSR's delivered to this specification under the specified test conditions.

- 3.6.11 Package and lead materials and finishes.

- 3.6.11.1 <u>Lead or terminal material</u>. A lead or terminal material that enables the relay to meet all of the performance requirements of this specification shall be used. For further guidance on lead and terminal materials that meet the performance requirements of this specification, see .7.1.

3.6.11.2 <u>Lead finish</u>. The finish system on all external leads or terminals shall conform to one of the following:

```

a. Hot solder

```

dip. b. Tin-lead

plate. c. Gold

plate.

Pure tin finish shall not be used on any internal or external package surface or as a lead finish. (NOTE: For further guidance on lead finishes, see 6.7.2.

3.6.11.3 <u>Solder dip (retinning) leads</u>. Only the manufacturer, at their option, may solder dip/retin the leads of the product supplied to this specification provided the solder dip/retin process (see appendix A, A.3.6.3) has been approved by the qualifying activity.

3.6.11.4 <u>Package body finish</u>. External metallic package elements other than leads or terminals (such as lids, covers, bases, or seal rings) shall meet the applicable corrosion resistance and environmental requirements or shall be finished so that they meet those requirements using finishes conforming to one or more of the following as applicable (pure tin finish shall not be used on any internal or external package surface or as a lead finish. In addition, tin plating shall not be used as an undercoat:

- a. Solder.

- b. Tin-lead

plate. c. Gold

plate.

d. Nickel plate.

(NOTE: For further guidance on these package body finishes, see 6.6.3).

- 3.7 <u>Pure tin.</u> The use of pure tin, as an underplate or final finish, is prohibited both internally and externally. Tin content of (product) and solder shall not exceed 97 percent, by mass. Tin shall be alloyed with a minimum of 3 percent lead, by mass (see 6.5).

- 3.8 <u>Screening</u>. When SSR's (screening level Y only) are screened as specified in 4.7.2.2, they shall meet the requirements as specified in .8.1 through .8.7.

- 3.8.1 <u>Preseal burn-in (optional)</u>. When SSR's are tested as specified in 4.7.2.1, they shall show no evidence of physical or mechanical damage. In addition, SSR's shall be tested in accordance with the electrical characteristics (see 3.13) at 25°C. Manufacturer may also perform electrical tests at temperature extremes.

- 3.8.2 Internal visual. When SSR's are tested as specified in 4.7.2.2, they shall meet the requirements as specified.

- 3.8.3 <u>Temperature cycling</u>. When SSR's are tested as specified in 4.7.2.3, they shall show no evidence of physical or mechanical damage.

- 3.8.4 <u>Mechanical shock or constant acceleration</u>. When SSR's are tested as specified in 4.7.2.4, they shall show no signs of physical or mechanical damage.

- 3.8.5 <u>Load conditioning</u>. When SSR's are tested as specified in 4.7.2.5, they shall show no signs of physical or mechanical damage.

- 3.8.6 <u>Interim (pre-burn-in) electrical requirements (optional)</u>. When SSR's are tested as specified in 4.7.2.6, they shall meet the electrical requirements as applicable.

- 3.8.7 <u>Burn-in test</u>. When SSR's are tested as specified in 4.7.2.7, they shall show no signs of physical or mechanical damage.

- 3.9 Solderability (applicable to solder terminals). When SSR's are tested as specified in 4.7.3, the dipped surface of solid wire-lead and pin terminals shall be at least 95 percent covered with a continuous new solder coating. The remaining 5 percent may contain only small pinholes or rough spots; these shall not be concentrated in one area. Bare base metal where the solder dip failed to cover the original coating is an indication of poor solderability, and shall be cause for failure. For solder-lug terminals, 95 percent of the total length of fillet, which is between the standard wrap wire and the terminal, shall be tangent to the surface of the terminal being tested, and shall be free of pinholes and voids. A ragged or interrupted line at the point of tangency between the fillet and the terminal under test shall be a failure.

- 3.10 <u>Seal</u>. When tested as specified in 4.7.4, there shall be no leakage in excess of 1 x  $10^{-8}$  atmospheric cubic centimeters per second of air (atm cm<sup>3</sup>/s), or as specified (see .1).

- 3.11 <u>Insulation resistance</u>. When SSR's are tested as specified in 4.7.5, the resistance shall be 100 megohms minimum. When specified (see .1), the insulation resistance between load circuits and input shall be 50 megohms minimum.

- 3.12 <u>Dielectric withstanding voltage (DWV)</u>. When tested as specified in 4.7.6, SSR's shall withstand the voltage specified without damage, and there shall be no leakage current in excess of 1.2 milliampere (mA); and there shall be no evidence of damage due to arcing (air discharge), flashover (surface discharge), or insulation breakdown (puncture discharge).

- 3.13 <u>Electrical characteristics</u>. Unless otherwise specified, 100 percent of the electrical characteristics shall be tested at -55°C, +25°C, and +125°C. Manufacturer has the option for sequence of test temperature (+25°C, -55°C, +125°C), and the sequence in which the electrical characteristics tests are performed.

- 3.13.1 Reverse polarity (dc operated SSR's) (when specified, see 3.1). When tested as specified in 4.7.7.1, the SSR shall not operate or be damaged. Following the test, the turn-on voltage, input current, and turn-off voltage shall be as specified (see .1).

- 3.13.2 <u>Input current (when specified, see .1)</u>. When SSR's are tested as specified in 4.7.7.2.1, the input current shall be as specified (see 3.1).

- 3.13.3 <u>Input turn-on voltage (when specified, see .1)</u>. When SSR's are tested as specified in 4.7.7.2.2, the SSR shall operate as specified (see 3.1).

- 3.13.4 <u>Input turn-off voltage (when specified, see .1)</u>. When SSR's are tested as specified in 4.7.7.2.3, the SSR shall operate as specified (see 3.1).

- 3.13.5 <u>Bias current (when specified, see .1).</u> When SSR's are tested as specified in 4.7.7.2.4, the bias current shall not exceed the specified value (see 3.1).

- 3.13.6 <u>Control current (when specified, see .1)</u>. When SSR's are tested as specified in 4.7.7.2.5, the control current shall not exceed the specified value (see 3.1).

- 3.13.7 <u>Control turn-on voltage (when specified, see .1)</u>. When SSR's are tested as specified in 4.7.7.2.6, the SSR shall operate as specified (see .1).

- 3.13.8 Control turn-off voltage (when specified, see .1). When SSR's are tested as specified in 4.7.7.2.7, the SSR shall operate as specified (see .1).

- 3.13.9 Overload: Will not trip current (short circuit protected SSR's) (when specified, see .1). When SSR's are tested as specified in .7.7.3, the SSR shall remain ON for the specified time (see 3.1).

- 3.13.10 Overload: Must trip current (short circuit protected SSR's) (when specified, see .1). When SSR's are tested as specified in .7.7.4, the SSR shall shut OFF within the specified time (see 3.1).

- 3.13.11 <u>Turn-on into a shorted load (when specified, see .1)</u>. When SSR's are tested as specified in 4.7.7.5, the SSR shall shut OFF.

- 3.13.12 Shorted load with SSR ON (when specified, see 3.1). When SSR's are tested as specified in 4.7.7.6, the SSR shall shut OFF.

- 3.13.13 <u>Status turn-on time (when specified, see .1).</u> When SSR's are tested as specified in 4.7.7.7, the status turn-on time shall not exceed the specified value (see 3.1).

- 3.13.14 <u>Status "ON" voltage (when specified, see .1).</u> When SSR's are tested as specified in 4.7.7.8, the status "ON" voltage shall be as specified (see .1).

- 3.13.15 <u>Status turn-off time (when specified, see .1)</u>. When SSR's are tested as specified in 4.7.7.9, the status turn-off time shall not exceed the specified value.

- 3.13.16 <u>Status "OFF" voltage (when specified, see .1).</u> When SSR's are tested as specified in 4.7.7.10, the status "OFF" voltage shall be as specified (see 3.1).

- 3.13.17 <u>Status blocking voltage (when specified, see .1)</u>. When SSR's are tested as specified in 4.7.7.11, the status (off) current shall not exceed the specified value.

- 3.13.18 <u>Status leakage current (when specified, see .1)</u>. When SSR's are tested as specified in 4.7.7.12, the status leakage current shall not exceed the specified value.

- 3.13.19 <u>Turn-on time</u>. When SSR's are tested as specified in 4.7.7.13, the turn-on time shall not exceed the specified value (see 3.1).

- 3.13.20 <u>Turn-off time</u>. When SSR's are tested as specified in 4.7.7.14, the turn-off time shall not exceed the specified value (see 3.1).

- 3.13.21 <u>Output voltage drop</u>. When SSR's are tested as specified in 4.7.7.15, the output voltage drop shall not exceed the value specified (see 3.1).

- 3.13.22 <u>Output leakage current</u>. When SSR's are tested as specified in 4.7.7.16, the leakage current in the output circuit shall not exceed the specified value (see 3.1).

- 3.13.23 <u>Transient voltage (when specified, see .1)</u>. When SSR's are tested as specified in 4.7.7.17, the output shall not turn on (see .1).

- 3.13.24 <u>DC offset voltage (ac SSR's only) (when specified, see 3.1)</u>. When SSR's are tested as specified in 4.7.7.18, the dc offset voltage shall not exceed the specified value (see 3.1).

- 3.13.25 <u>Waveform distortion (ac SSR's only) (when specified, see 3.1)</u>. When SSR's are tested as specified in 4.7.7.19, the waveform distortion (commutation spikes) shall not exceed the specified value (see 3.1).

- 3.13.26 <u>Minimum load current rating (ac SSR's only) (when specified, see 3.1)</u>. When SSR's are tested as specified in 4.7.7.20, the SSR shall remain ON.

- 3.13.27 <u>Exponential rate of voltage rise (when specified, see 3.1)</u>. When SSR's are tested as specified in 4.7.7.21, they shall withstand the specified rate of voltage rise (see .1).

- 3.13.28 Zero crossover (ac SSR's only) (when specified, see 3.1). When SSR's are tested as specified in 4.7.7.22, the SSR turn-on shall occur within the specified (see .1) zero voltage crossover, and SSR turn-off shall occur within the specified (see 3.1) zero current crossover.

- 3.13.29 <u>Electrical system spike (when specified, see .1)</u>. When SSR's are tested as specified in 4.7.7.23, they shall withstand the voltage specified without damage.

- 3.13.30 Overload (non-short circuit protected SSR's only) (when specified, see 3.1). When SSR's are tested as specified in 4.7.7.24, they shall withstand the specified overload without damage.

- 3.13.31 Power dissipation (when specified, see .1). When SSR's are tested as specified in 4.7.7.25 the power dissipation shall not exceed the specified value (see 3.1).

- 3.14 Resistance to solvents. When SSR's are tested as specified in 4.7.8, the marking shall remain legible.

- 3.15 <u>Shock (specified pulse)</u>. When SSR's are tested as specified in 4.7.9, there shall be no evidence of physical or mechanical damage.

- 3.16 <u>Vibration</u>. When SSR's are tested as specified in 4.7.10, there shall be no evidence of physical or mechanical damage.

- 3.17 <u>Terminal strength</u>. When SSR's are tested as specified in 4.7.11, there shall be no evidence of loosening or breaking of the terminals; and there shall be no deformation to the threads of screw terminals; no damage to the insulating base of plug-in SSR's; nor shall there be any other damage which would adversely affect the normal operation of the SSR. Bending of solder terminals shall not be construed as damage; bending of plug-in terminals shall not be construed as damage, provided they can be reformed in a manner to permit proper mating with the applicable sockets.

- 3.18 <u>Moisture resistance (applicable to nonhermetically sealed SSR's only)</u>. When SSR's are tested as specified in .7.12, there shall be no evidence of breaking, cracking, chipping or flaking of the finish, or loosening of the terminals. After the 24-hour drying period, SSR's shall meet the following requirements:

- a. Insulation resistance: As specified in

- 3.11. b. DWV: As specified in 3.12.

- c. Input turn-off voltage: As specified in 3.13.4.

- d. Input turn-on voltage: As specified in

- 3.13.3. e. Output voltage drop: As specified

in 3.13.21.

- f. Output leakage current: As specified in 3.13.22.

- 3.19 <u>Crosstalk (when specified, see 3.1)</u>. When SSR's are tested as specified in 4.7.13, the attenuation shall be a minimum of 20 decibels.

- 3.20 <u>Isolation (when specified, see .1)</u>. When SSR's are tested as specified in 4.7.14, the capacitance shall not exceed the value specified.

- 3.21 Resistance to soldering heat (when specified, see 3.1). When SSR's are tested as specified in 4.7.15, there shall be no damage which would adversely affect normal operation of the SSR's.

- 3.22 <u>Salt atmosphere (corrosion)</u>. When SSR's are tested as specified in 4.7.16, there shall be no evidence of breaking, cracking, chipping or flaking of the finish, nor exposure of base metal due to corrosion which would adversely affect the application or performance characteristics of the SSR's.

- 3.23 <u>Life</u>. When SSR's are tested as specified in 4.7.17, there shall be no damage which would adversely affect normal operation of the SSR's.

- 3.24 <u>Marking</u>. All applicable marking shall appear on a surface visible when the SSR is mounted in its normal position.

- 3.24.1 <u>JAN and J marking</u>. The United States Government has adopted and is exercising legitimate control over the certification marks "JAN" and "J", respectively, to indicate that items so marked or identified are manufactured to, and meet all the requirements of specifications. Accordingly, items acquired to, and meeting all of the criteria

specified herein and in applicable specifications shall bear the certification mark "JAN" except that items too small to bear the certification mark "JAN" shall bear the letter "J". The "JAN" and "J" shall be placed immediately before the PIN except that if such location would place a hardship on the manufacturer in connection with such marking, the "JAN" or "J" may be located on the first line above or below the PIN. Items furnished under contracts or orders which either permit or require deviation from the conditions or requirements specified herein on in applicable specifications shall not bear "JAN" or "J". In the event an item fails to meet the requirements of this specification and the applicable specification sheets, the manufacturer shall remove completely the military PIN and the "JAN" or the "J" from the

sample tested and also from all items represented by the sample. The "JAN" or "J" certification mark shall not be used on products acquired to contractor drawings or specifications. The United States Government has obtained Certificate of Registration Number 504,860 for the certification mark "JAN" and Registration Number 1,586,261 for the certification mark "J".

- 3.24.2 <u>Identification marking (full)</u>. SSR's shall be marked in accordance with MIL-STD-1285, with the following information as a minimum:

- a. Military PIN, including a 'Y' or "W" to indicate screening level (see 1.3 and .1). The 'JAN' or 'J' shall not be marked in front of the PIN.

- b. "JAN" or "J" brand. The "JAN" or "J" shall appear directly above or below the "M" of the PIN.

```

Examples: JAN or M28750/5-001Y M28750/5-001Y J

```

- c. Rated input voltage.

- d. Rated output voltage (or

current). e. Circuit diagram.

- f. Terminal marking (see .6.5).

- g. Date code (at the option of the manufacturer the "J" with the date code may be used instead of b).

- h. Manufacturers name or Commercial and Government Entity CAGE code.

- Lot symbol.

- j. ESD sensitivity identifier, (see .24.4).

- 3.24.3 Minimum marking (when specified, see .1). When space does not permit the marking specified in 3.24.2, the marking shall include, as a minimum, the PIN including a "Y" to indicate screening level, "J" with date code (example 'J9232'), circuit diagram, manufacturers name or CAGE code, and ESD identifier. The circuit diagram may also be eliminated provided that it appears in the SSR specification.

- 3.24.4 <u>ESD sensitivity identifier</u>. The SSR shall be marked with a sensitive electronic device symbol as specified in MIL-STD-1285, or if room does not permit, the outline of an equilateral triangle ( $\otimes$ ) shall be used and may also be used as a pin 1 identifier. The equilateral triangle will designate these SSR's as ESDS in the range of 0 volts 1,999 volts and the parts shall be handled as such same as previous revision.

- 3.24.5. <u>Beryllium oxide package identifier</u>. If a SSR package contains beryllium oxide, the SSR shall be marked with the designation "BeO".

- 3.25 <u>Recycled, recovered, or environmentally preferable materials</u>. Recycled, recovered, or environmentally preferable materials should be used to the maximum extent possible provided that the material meets or exceeds the operational and maintenance requirements and promotes economically advantageous life cycle costs.

- 3.26 <u>Workmanship</u>. SSR's shall be manufactured and processed in such a manner as to be uniform in quality and shall be free from any defects that will affect life, serviceability, or appearance.

#### 4. VERIFICATION

- 4.1 Classification of inspections. The inspections specified herein are classified as follows:

- a. Qualification inspection (see 4.4).

- b. Conformance inspection (see

4.6).

- c. Periodic inspection (group B and group C inspection, see 4.6.2).

- 4.2 <u>QPL system</u>. The manufacturer shall establish and maintain a QPL system as described in 3.3. Evidence of such compliance shall be verified by the qualifying activity for this specification as prerequisite for qualification and retention of qualification.

- 4.3 <u>Inspection conditions</u>. Unless otherwise specified herein, all inspections shall be performed in accordance with the test conditions specified in the "GENERAL REQUIREMENTS" of MIL-STD-883 and MIL-STD-202.

- 4.3.1 <u>Power supply</u>. Unless otherwise specified herein, the power supply shall have no more than 5 percent regulation at 110 percent of the specified test current. A dc power supply shall have no more than 5 percent ripple voltage. An ac power supply shall be within 1 percent of the specified frequency and shall be sinusoidal with a form factor between 0.95 and 1.25.

- 4.3.1.1 <u>Grounding</u>. Unless otherwise specified (see 3.1), the negative side of the dc power supply shall be grounded; one side of single-phase ac power supply shall be grounded; or the neutral of 3-phase ac power supply shall be grounded, as applicable.

- 4.3.2 <u>Load conditions during tests</u>. The input of the SSR being tested shall be connected to the grounded side of its power supply; each load of the SSR being tested shall be connected to the grounded side of its power supply; and each output shall be connected to an individual load. Separate power supplies shall be used for the input to the SSR and the individual load being tested.

- 4.4 <u>Qualification inspection</u>. Qualification inspection shall be performed at a laboratory acceptable to the Government (see .3) on sample SSR's produced with equipment and procedures normally used in production. Qualifications of the "W" screening level PIN is predicated upon qualification of the "Y" screening level PIN. Upon request of the manufacturer, qualification to the "W" screening level PIN's will be granted for the envelope of products successfully qualified to the "Y" screening level PIN's. The products involved shall be of the same design, manufactured using the same facilities, processes, and materials as the product originally submitted for and qualified under the "Y" screening level.

- 4.4.1 <u>Sample size</u>. The number of SSR's to be subjected to qualification inspection shall be 12. In addition, submit one unsealed sample to the qualifying activity as part of the qualification procedure. The sample SSR's shall be taken at random from a production run and shall be produced with equipment and procedures normally used in production, and which have been subjected to and passed the requirements of group A inspection (see 4.6.1.2). Qualification shall not be granted if group A inspection requirements are not complied with.

- 4.4.2 <u>Inspection routine</u>. Qualification samples shall be subjected to the tests as specified in table I, in the order shown, as applicable for each SSR. All sample units shall be subjected to group Q1. The sample units shall then be divided into three groups of four and shall then be subjected to group Q2, group Q3, and group Q4.

TABLE I. Qualification inspection.

| Inspection                       | Requirement          | Test method | Samples   |

|----------------------------------|----------------------|-------------|-----------|

| ·                                | paragraph            | paragraph   | per group |

| Group Q1                         |                      |             |           |

| <u></u>                          |                      |             |           |

| Electrical system spike          | 3.13.29              | 4.7.7.23    |           |

| Overload                         | 3.13.30              | 4.7.7.24    | 12        |

| Power dissipation                | 3.13.31              | 4.7.7.25    |           |

| Visual and mechanical inspection | 3.1, 3.4, 3.6, 3.24, | 4.7.1       |           |

|                                  | and .25              |             |           |

| Group Q2                         |                      |             |           |

| •                                |                      |             |           |

| Resistance to solvents           | 3.14                 | 4.7.8       |           |

| Shock (specified pulse)          | 3.15                 | 4.7.9       |           |

| Vibration                        | 3.16                 | 4.7.10      |           |

| Terminal strength                | 3.17                 | 4.7.11      |           |

| Temperature cycling              | 3.8.3                | 4.7.2.3     | 4         |

| Seal                             | 3.9                  | 4.7.3       |           |

| Moisture resistance              | 3.18                 | 4.7.12      |           |

| Insulation resistance            | 3.11                 | 4.7.5       |           |

| DWV                              | 3.12                 | 4.7.6       |           |

| Electrical characteristics       | 3.13                 | 4.7.7       |           |

| Visual and mechanical inspection | 3.1, 3.4, 3.6, 3.24, | 4.7.1       |           |

|                                  | and .25              |             |           |

| Group Q3                         |                      |             |           |

| Crosstalk                        | 3.19                 | 4.7.13      |           |

| Isolation                        | 3.20                 | 4.7.14      |           |

| Resistance to soldering heat     | 3.21                 | 4.7.15      |           |

| Salt atmosphere (corrosion)      | 3.22                 | 4.7.16      |           |

| Insulation resistance            | 3.11                 | 4.7.5       | 4         |

| DWV                              | 3.12                 | 4.7.6       |           |

| Electrical characteristics       | 3.13                 | 4.7.7       |           |

| Seal                             | 3.10                 | 4.7.4       |           |

| Visual and mechanical inspection | 3.1, 3.4. 3.6, 3.24, | 4.7.1       |           |

|                                  | and .25              |             |           |

| Group Q4                         |                      |             |           |

| Life                             | 3.23                 | 4.7.17      |           |

| Insulation resistance            | 3.11                 | 4.7.5       |           |

| DWV                              | 3.12                 | 4.7.6       | 4         |

| Electrical characteristics       | 3.13                 | 4.7.7       | -         |

| Seal                             | 3.10                 | 4.7.4       |           |

| Visual and mechanical inspection | 3.1, 3.4, 3.6, 3.24, | 4.7.1       |           |

| ·                                | and .25              |             |           |

- 4.4.3 <u>Failures</u>. No failures shall be allowed for group Q1, and only one failure shall be allowed for group Q2, group Q3, and group Q4 combined. Failures in excess of those allowed shall be cause for refusal to grant qualification approval.

- 4.5 <u>Retention of qualification</u>. To retain qualification, every 24 months, the contractor shall provide verification of the following requirements:

- a. MIL-STD-790 program.

- b. Design of the SSR has not bee modified.

- c. Screening tests, conformance tests, and periodic tests have been performed as specified herein.

- d. The contractor retains the capability to manufacture and test SSR's to this specification.

- e. Continued qualification to screening level W shall be based on continued maintenance of qualification for screening level Y.

In the event that no production occurred during this period, the contractor shall still verify to the qualifying activity the capability to manufacture and test the QPL SSR still exists and the contractor wants to remain on the QPL.

- 4.6 Conformance inspection.

- 4.6.1 <u>Inspection of product for delivery</u>. Inspection shall consist of group A inspection.

- 4.6.1.1 Production and inspection lot.

- 4.6.1.1.1 <u>Production lot</u>. A production lot shall consist of all SSR's covered by a single specification sheet and single PIN. All SSR's in the lot shall have been started, processed, assembled, and tested as a group. Lot identity shall be maintained throughout the manufacturing cycle.

- 4.6.1.1.2 <u>Inspection lot</u>. An inspection lot shall consist of all SSR's covered by a single specification sheet, produced and sealed under essentially the same conditions, and offered for inspection at one time within a period not to exceed 1 month.

- 4.6.1.2 Group A inspection.

- a. Screening level Y: Group A inspection shall consist of the inspections specified in table II, in the order shown.

- b. Screening level W: The manufacturer shall establish and maintain an inspection system to verify that these

- SSR's meet the electrical, visual, mechanical, and solderability requirements. In-line or process control may be part of such a system. The inspection system shall also include criteria for lot rejection and corrective actions. The inspection system shall be verified under the overall QPL system (see 3.3). NOTE: Since screening level W is the same design as screening level Y without the mandatory conformance inspection, screening level W product shall meet the environmental qualification type requirements (such as moisture resistance, shock, and vibration).

| TADLE II | O A | inspection. |

|----------|-----|-------------|

|          |     |             |

|          |     |             |

| Inspection                                              | Requirement paragraph                  | Test<br>method<br>paragraph | Sampling procedure |

|---------------------------------------------------------|----------------------------------------|-----------------------------|--------------------|

| Group A1                                                | paragrapii                             | paragrap                    | p. cocaa.c         |

| Screening                                               | 3.8                                    | 4.7.2.2                     | 4.6.1.2.1          |

| Group A2 1/ 2/                                          |                                        |                             |                    |

| Insulation resistance DWV Electrical characteristics 3/ | 3.11<br>3.12<br>3.13                   | 4.7.5<br>4.7.6<br>4.7.7     | 4.6.1.2.1          |

| Group A3 4/ 5/                                          |                                        |                             |                    |

| Seal<br>Visual and mechanical inspection                | 3.10<br>3.1, 3.4, 3.6,<br>3.24 and .25 | 4.7.4<br>4.7.1              | 4.6.1.2.1          |

| Group A4                                                |                                        |                             |                    |

| Solderability <u>6</u> /                                | 3.9                                    | 4.7.3                       | 4.6.1.2.2          |

- 1/ Testing sequence optional for insulation resistance and DWV.

- <u>2</u>/ Transient voltage and exponential rate of voltage rise (dv/dt) shall be performed at +25°C ambient.

- 3/ Electrical characteristic testing shall not include the following: Electrical system spike, overload, and power dissipation.

- 4/ Physical dimensions and weight shall be measured on two sample units per lot.

- 5/ Minor defects, such as marking, may be reworked.

- 6/ This solderability test can be eliminated if the manufacturer has demonstrated process control under the SPC program (see .3.1), or other method that has been approved by the qualifying activity. If the design, material, technology, or processing of the part is changed or, if there are any quality problems, or failures, the qualifying activity may require resumption of the specified testing. Deletion of testing does not relieve the manufacturer from meeting the test requirement in case of dispute.

- 4.6.1.2.1 <u>Sampling plan (group A1, group A2, and group A3)</u>. The tests performed in group A1, group A2, and group A3 shall require 100 percent inspection, except only two units per production lot shall be tested for dc offset voltage, waveform distortion, and minimum current ratings. Defective SSR's shall be removed from the production lot. If, during the 100 percent inspection of group A2 over 5 percent of the SSR's are discarded, the production lot shall be rejected. The rejected production lot may be resubmitted for group A2 rescreening provided the SSR's meet the following criteria:

- a. The observed percentage defective allowed (PDA) does not exceed twice the specified PDA.

- b. The cause of failure has been evaluated and determined.

- c. The failure was due to random causes or, for pattern failures, appropriate and effective corrective action has been completed to reject all SSR's affected by the failure cause.

- d. Appropriate preventive action has been initiated.

- e. The failure shall not have the potential to cause any latent field failure on the remaining SSR's.

- f. The preceding conditions shall not apply in those cases (instances) where the failures can be directly attributed to random equipment failure or operator error, with qualifying activity concurrence.

- 4.6.1.2.2 <u>Sampling plan (group A4)</u>. Two samples shall be selected randomly from each inspection lot and subjected to the group A4 solderability test. The manufacturer may use electrical rejects from the group A2 screening tests for all or part of the samples to be used for solderability testing. If there is one or more defects, the lot shall have failed.

- 4.6.1.2.2.1 Rejected lots (group A4). In the event of one or more defects, the inspection lot is rejected. The manufacturer may use one of the following options to rework the lot:

- a. Each production lot that was used to form the failed inspection lot shall be individually submitted to the solderability test as required in .6.1.2.2. Production lots that pass the solderability test are available for shipment. Production lots failing the solderability test can be reworked only if submitted to the solder dip procedure in (b).

- b. The manufacturer submits the failed lot to a 100 percent solder dip using an approved solder dip process in accordance with 3.6.11.3. Following the solder dip process, the A2, A3, and A4 group A inspections shall be repeated on the lot. If the lot fails the group A2 PDA requirement or fails the group A4 solderability test, the lot shall be rejected and shall not be furnished against the requirements of this specification.

- 4.6.1.2.3 <u>Disposition of samples</u>. The solderability test is considered a destructive test and samples submitted to the solderability test shall not be supplied on the contract.

- 4.6.2 <u>Periodic inspections</u>. Periodic inspections shall consist of group B and group C. Except where the results of these inspections show noncompliance with the applicable requirements (see 4.6.2.2.4), delivery of products which have passed group A shall not be delayed pending the results of these periodic inspections.

- 4.6.2.1 <u>Group B inspection</u>. Group B inspection shall consist of the tests specified in table III and shall be made on sample units which have been subjected to and have passed the group A inspection.

TABLE III. Group B inspection.

| Inspection                                                                                            | Requirement paragraph                        | Test<br>method<br>paragraph                           | Number<br>of<br>sample<br>units | Number<br>of<br>failures<br>allowed |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------|---------------------------------|-------------------------------------|

| Vibration Terminal strength Moisture resistance Insulation resistance Electrical characteristics Seal | 3.16<br>3.17<br>3.18<br>3.11<br>3.13<br>3.10 | 4.7.10<br>4.7.11<br>4.7.12<br>4.7.5<br>4.7.7<br>4.7.4 | 4                               | 0                                   |

| Visual and mechanical inspection                                                                      | 3.1, 3.4, 3.6,<br>3.24 and .25               | 4.7.1                                                 |                                 |                                     |

- 4.6.2.1.1 <u>Sampling plan</u>. Four sample units from each specification sheet shall be selected every six months from sample SSR's which have passed group A inspection. No failures shall be allowed. If the manufacturer can demonstrate this test has been performed for five consecutive times with zero failures, the frequency of this test, with the approval of the qualifying activity, can be performed on an annual basis. If the design, technology, or processing of the part is changed, or if there are any quality problems or failures, the qualifying activity may require resumption of the original test frequency.

- 4.6.2.1.2 <u>Disposition of sample units</u>. Sample units which have been subjected to group B inspection shall not be delivered on the contract or purchase order.

- 4.6.2.2 <u>Group C inspection</u>. Group C inspection shall consist of the tests specified in table I, in the order shown. Group C inspection shall be made on sample units selected from inspection lots which have passed the group A inspection.

- 4.6.2.2.1 <u>Sampling plan</u>. Twelve sample SSR's of the same PIN as originally qualified shall be selected 24 months after the date of every notification of qualification, and after each subsequent 24-month period.

- 4.6.2.2.2 Failures. Failures in excess of those allowed in table I shall be cause for removal of qualification.

- 4.6.2.2.3 <u>Disposition of sample units</u>. Sample units which have been subjected to group C inspection shall not be delivered on the contract or purchase order.

- 4.6.2.2.4 Noncompliance. If a sample fails the group B or group C inspection, the manufacturer shall notify the qualifying activity and the cognizant inspection activity of such failure and take corrective action on the materials or processes, or both, as warranted. This corrective action shall be performed on all units of product which can be corrected; which were manufactured under essentially the same materials and processes; and which are subject to the same failure. Acceptance and shipment of the product shall be discontinued until corrective action, acceptable to the qualifying activity, has been taken. After the corrective action has been taken, group C inspection shall be repeated on additional sample units (all inspections, or the inspection which the original sample failed, at the option of the qualifying activity). Group A and group B inspections may be reinstituted; however, final acceptance and shipment shall be withheld until the group C inspection has shown that the corrective action was successful. In the event of failure after reinspection, information concerning the failure shall be furnished to the cognizant inspection activity and the qualifying activity.

- 4.7 Methods of inspection.

- 4.7.1 <u>Visual and mechanical inspection</u>. SSR's shall be examined to verify that the interface, external design and technology, physical dimensions, marking, and workmanship are in accordance with the applicable requirements (see 3.1, 3.4, 3.6, 3.24 and .25).

- 4.7.2 Screening (Y level only) (see .8). SSR's shall be screened in accordance with 4.7.2.1 through .7.2.7.

- 4.7.2.1 <u>Preseal burn-in (optional) (see .8.1)</u>. SSR's shall be tested in accordance with method 1030 of MIL-STD-883.

- 4.7.2.2 Internal visual (see 3.8.2). SSR's shall be tested in accordance with method 2017 of MIL-STD-883.

- 4.7.2.3 <u>Temperature cycling (see 3.8.3)</u>. SSR's shall be tested in accordance with method 1010 of MIL-STD-883. Unless otherwise specified, test condition B shall apply: 100 cycles for qualification inspection and 10 cycles for conformance inspection.

- 4.7.2.4 Mechanical shock or constant acceleration (see .8.4).

- a. Mechanical shock: SSR's shall be tested in accordance with MIL-STD-883, method 2002, test condition B. Y1 direction only.

- b. Constant acceleration: SSR's shall be tested in accordance with MIL-STD-883, method 2001, test condition

- A. Y1 direction only.

- 4.7.2.5 <u>Load conditioning (see 3.8.5)</u>. SSR's shall be cycled by applying a step function voltage to the input; the input shall be energized at zero or rated input voltage. The on-state load shall be maximum rated current, without auxiliary heat sink. Each output circuit shall be loaded with the maximum rated resistive current at the highest rated voltage, for 3 hours, at a rate no less than 1 operation per second nor more than 30 operations per second. When applicable (see 3.1), the bias shall be applied at the rated value. The SSR shall be turned off 10 percent of the time

- and turned on 90 percent of the time. For single-pole double-throw and double-pole double-throw SSR's, cycling shall be 50 percent turned on and 50 percent turned off; or for 1.5 hours of test, 10 percent on and 90 percent off, and 90 percent on and 10 percent off for 1.5 hours of test.

- 4.7.2.6 <u>Interim (pre-burn-in) electrical requirements (see .8.6)</u>. The interim (pre-burn-in) electrical requirements may be performed at the option of the manufacturer. Electrical parameters tested shall be those specified in 3.13, as applicable.

- 4.7.2.7 Burn-in test (see .8.7). Unless otherwise specified (see 3.1), SSR's shall be subjected to 160 +8 hours/ 0 hours of operation at the maximum operating temperature. At the option of the manufacturer, the burn-in time-temperature regression table of MIL-STD-883, method 1015, may be used. Lower temperatures at higher load currents, in accordance with the specified derating curve, may be used with qualifying activity approval. Input and bias (where applicable) shall be at the rated ON state conditions. The output(s) shall be loaded with the maximum specified current derated for the test temperature. Output condition shall be monitored with latching failure circuitry and appropriate indicators. If scanning type condition monitoring is employed, each SSR shall be monitored at least once per second throughout the entire burn-in period.

4.7.2.7 <u>Burn-in test (see .8.7) (continued)</u>. Test conditions shall be measured on one randomly selected socket prior to start of the test. The values, the test temperature, and start time shall be recorded on a burn-in log. At the completion of the test prior to removal of bias, the test conditions shall be measured on one randomly selected socket. The values, the temperature, and the finish time shall be recorded on the burn-in log.

Any SSR's that fail during the burn-in shall be removed from the lot at the completion of burn-in. If the test conditions are interrupted for more than 10 minutes during the test (for example, due to equipment malfunction or power outages), the test duration shall be extended to ensure that actual exposure time is 160 +8 hours/-0 hours. Any such interruptions in the final eight hours of test shall require an extension of the test duration for eight hours following the last interruption.

- 4.7.3 <u>Solderability (applicable to solder terminals) (see 3.9</u>). SSR's shall be tested in accordance with method 208 of MIL-STD-202. All terminations of each SSR shall be tested.

- 4.7.4 <u>Seal (see .10)</u>. SSR's shall be tested in accordance with 4.7.4.1 or .7.4.2 as applicable. In case of dispute, MIL-STD-883, method 1014, test condition A shall govern.

- 4.7.4.1 <u>SSR's sealed with a tracer gas</u>. SSR's sealed with a tracer gas shall be tested in accordance with <u>MIL-STD-202</u>, method 112 (see 4.7.4.1a) or <u>MIL-STD-883</u>, method 1014 (see .7.4.1b). The following details shall apply:

- a. Method 112 of MIL-STD-202:

- (1) Test condition C, procedure IV. SSR's shall be back filled with a helium tracer gas (90 percent dry gas and 10 percent helium). For gross leak, silicone oil shall not be used.

- (2) Leakage rate sensitivity: 1 x 10<sup>-8</sup> atm cm<sup>3</sup>/s.

- (3) Measurements after test: Not applicable.

- b. Method 1014 of MIL-STD-883, test condition A or test condition B.

- 4.7.4.2 <u>SSR's sealed without a tracer gas</u>. SSR's sealed without a tracer gas shall be tested in accordance with MIL-STD-883, method 1014. At the option of the manufacturer, either .7.4.2a or .7.4.2b may be used. The following details shall apply.

- a. Method 1014 of MIL-STD-

- 883: (1) Test condition

A1 or A2.

- (2) Measurements after test: Perform a gross leak test in accordance with MIL-STD-202, method 112, test condition A, B, or D. Silicone oil shall not be used. At the option of the manufacturer, the gross leak test of MIL-STD-883, method 1014, test condition C, may be used.

- b. Method 1014 of MIL-STD-883, test condition B.

- 4.7.4.3 <u>Radioisotope dry gross leak test (optional)</u>. This test shall be used only to test SSR's that internally contain some krypton-85 absorbing medium, such as electrical insulation, organic sieve material, or molecular sieve material. This test shall be permitted only if the following requirements are met:

- a. A 5 to 10 mil diameter hole shall be made in a representative unit of the SSR to be tested. (This is a one time test that remains in effect until a design change is made in the SSR internal technology.)

- b. The SSR shall be subjected to this test condition. If the SSR exhibits a hard failure, this test condition may

be used for those SSR's represented by the test unit. If the SSR does not fail, this test shall not be used and instead a +125°C fluorocarbon gross leak shall be performed in accordance with MIL-STD-202, method 112, test condition D, except the specimen shall be observed from the instant of immersion for 1 minute minimum to 3 minutes maximum.

- 4.7.4.3.1 Apparatus. The following apparatus shall be required for this test:

- a. Radioactive tracer gas activation console containing krypton-85/dry nitrogen gas mixture.

- b. Counting station with sufficient sensitivity to determine the radiation level of krypton-85 tracer gas inside the SSR.

- c. Tracer gas mixture: Krypton-85/dry nitrogen with a minimum allowable specific activity of 100 microcuries per atmosphere cubic centimeter. The specific activity of the krypton-85/dry nitrogen mixture shall be a known value and determined on a once-a-month basis as a minimum.

- 4.7.4.3.2 Procedure. The SSR's shall be placed in a radioactive tracer gas activation tank and the tank shall be evacuated to a pressure not to exceed 0.5 torr. The SSR's shall then be subjected to a minimum of 10 pounds per square inch gauge of krypton-85/dry nitrogen gas mixture for 30 seconds. The gas mixture shall then be evacuated in storage until a pressure of 2.0 torr maximum exists in the activation tank. The evacuation shall be completed in 5 minutes maximum. The evacuation tank shall then be backfilled with air (air wash). The SSR's shall then be removed from the activation tank and leak tested within 2 hours after gas exposure with a scintillation-crystal-equipped counting station. SSR's indicating 1,000 counts per minute or greater above the ambient background of the counting station shall be considered a gross leak failure.

- 4.7.5 <u>Insulation resistance (see 3.11)</u>. SSR's shall be tested in accordance with MIL-STD-883, method 1003. The following details and exceptions shall apply:

- a. Test condition: E

- b. Points of measurement:

- (1) A common connection of each input circuit and every other isolated input circuit, if applicable.

- (2) When specified (see 3.1), a common connection of all input terminals, and a common connection of all output terminals. Unless otherwise specified (see .1), the voltage shall be 500 volts, and the input shall be positive with respect to the output.

- (3) A common connection of the terminals of each output pole, and a common connection of all other isolated output terminals.

- c. Electrification time: 2 iminutes, or until a stable reading is obtained.

- 4.7.6 <u>DWV (see .12)</u>. SSR's shall be tested as specified in 4.7.6.1, and when specified (see 3.1), in accordance with .7.6.2.

- NOTE: To avoid unnecessary failures, test voltages shall not be applied indiscriminately. Before beginning test, short-circuit connections shall be made between any set of non isolated input or output terminals in which there is a possibility that the SSR will be damaged if the test voltage is applied between them.

- 4.7.6.1 <u>At atmospheric pressure</u>. Solid state SSR's shall be tested in accordance with MIL-STD-202, method 301. The following details shall apply:

- a. Magnitude of test voltage: As specified (see

- 3.1). b. Nature of potential: As specified (see 3.1).

- c. Points of application: Chassis ground, if applicable, and a common connection of all other terminals.

- d. Maximum leakage current: 1.0 mA.

- e. Test time shall be 60 seconds for qualification testing and for all other testing at the specified DWV (see .1). If the test voltage is increased to 5 percent above the specified (see .1) voltage, the test time shall be 15 seconds.

- f. Following these tests, SSR's shall be examined for evidence of arcing, flashover, insulation breakdown, and damage.

- 4.7.6.2 <u>At reduced barometric pressure</u>. SSR's specified (see 3.1) for operation above 10,000 feet shall be tested in accordance with MIL-STD-202, method 105. The following details shall apply:

- a. Method of mounting: Normal mounting means.

- b. Test condition: C (unless otherwise specified) (see .1).

- c. Tests during subjection to reduced pressure: As specified in 4.7.6.1, except test voltage shall be 1/3 of specified magnitude.

- d. Same as .7.6.1 e.

- 4.7.7 <u>Electrical characteristics</u>.

- 4.7.7.1 Reverse polarity (dc operated SSR's) (see 3.13.1).

- a. Input configuration

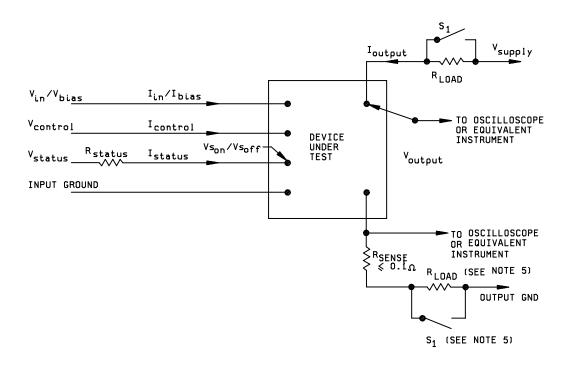

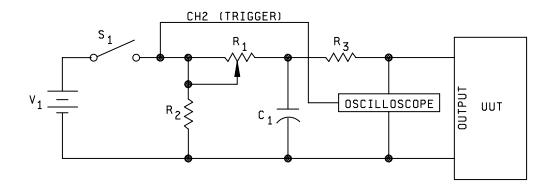

- 1) Test setup in accordance with figure 1.

- 2) Apply specified (see 3.1) load, voltage, and frequency (if applicable).

- 3) Remove input voltage, and status voltage (if applicable), and reapply the specified (see 3.1) voltage in reverse polarity between input and input ground.

- 4) Verify that the reverse input current (I(in)) is below the specified (see .1) value.

- 5) Observe the output for any sign of turn-on by measuring V(output).

# 4.7.7.2 Input characteristics.

## 4.7.7.2.1 <u>Input current (see .13.2)</u>.

- a. Test setup in accordance with figure

- 1. b. Apply maximum input voltage

(V(in)).

c. Verify that input current (I(in)) is as specified (see 3.1).

## 4.7.7.2.2 Input turn-on voltage (see 3.13.3).

- a. Test setup in accordance with figure 1.

- b. Apply the specified (see 3.1) load, voltage, and frequency (if applicable).

- c. Apply specified (see 3.1) input turn-on voltage (V(in)).

- d. Verify that the SSR is ON by measuring the output current (I(output)), or by measuring output voltage drop (V(output)).

# 4.7.7.2.3 Input turn-off voltage (see 3.13.4).

- a. Test setup in accordance with figure 1.

- b. Apply specified (see 3.1) load, voltage and frequency (if applicable).

- c. Apply specified (see 3.1) input turn-on voltage (V(in)) to turn the SSR ON. Then apply specified (see 3.1) input turn-off voltage (V(in)).

- d. Verify that the SSR is OFF by measuring the output current (I(output)) to be within leakage current specification (see 3.1), or by measuring the output voltage (V(output)).

### NOTES:

- R<sub>SENSE</sub> may be replaced by an isolated current probe (current transformers, hall effect devices, or equivalent).

- 2. Status terminals as applicable.

- 3.  $V_{STATUS}$  and  $R_{STATUS}$  as applicable.

- 4. Unless otherwise specified, resistive loads are used for testing methods.

- 5. Option load may be connected as shown.

FIGURE 1. General test setup.

### 4.7.7.2.4 Bias current (see 3.13.5).

- a. Test setup in accordance with figure 1.

- b. Apply maximum bias voltage, V(bias), then the specified (see .1) control voltage, V(control), to energize the bias current.

- c. Verify that bias current (I(bias)) is as specified (see 3.1).

# 4.7.7.2.5 Control current (see .13.6).

- a. Test setup in accordance with figure 1.

- b. Apply specified (see 3.1) bias voltage V(bias), and apply specified (see 3.1) control voltage V(control).

- c. Verify that control current, I(control), is as specified (see 3.1).

## 4.7.7.2.6 Control turn-on voltage (see 3.13.7).

- a. Test setup in accordance with figure 1.

- b. Apply the specified (see 3.1) load, voltage, and frequency (if applicable).

- c. Apply the specified (see 3.1) bias voltage, V(bias), and the specified (see .1) control turn-on voltage, V(control) to turn the SSR on.

- d. Verify that the SSR is ON by measuring the output current I(output), or by measuring output voltage drop V(output).

# 4.7.7.2.7 Control turn-off voltage (see 3.13.8).

- a. Test setup in accordance with figure 1.

- b. Apply the specified (see 3.1) load, voltage, and frequency (if applicable).

- c. Apply the specified (see 3.1) bias voltage, V(bias), and control turn-on voltage to turn the SSR on. Then apply specified (see 3.1) control turn-off voltage to turn the SSR OFF.

- d. Verify that the SSR is OFF by measuring the output current I(output) to be within leakage current specification (see 3.1), or by measuring the output voltage V(output).

# 4.7.7.3 Overload: Will-not-trip current (see .13.9).

- a. Test setup in accordance with figure 1.

- b. Apply the specified (see 3.1) will-not-trip current, and frequency (if applicable).

- c. Apply specified (see 3.1) input conditions for the specified (see .1) will-not-trip time.

- Verify that the SSR remains ON for the specified (see .1) time by observing the output current I (output), or the output voltage V(output).

- e. Verify that the SSR meets the trip characteristics at the various current levels specified (see .1).

### 4.7.7.4 Overload: Must-trip current (see

3.13.10). a. Test setup in accordance with

### figure 1.

- b. Apply the specified (see 3.1) must-trip current, and frequency (if applicable).

- c. Apply specified (see 3.1) input conditions for a time equal to or greater than the specified (see 3.1) must-trip time.

- d. Verify that the SSR shuts OFF within the specified (see .1) time by measuring the output current I(output), or the output voltage V(output).

- e. Verify that the SSR meets the trip characteristics at the various current levels specified (see .1).

### 4.7.7.5 Turn-on into a shorted load (see .13.11).

- a. Test setup in accordance with figure 1.

- b. Apply specified (see 3.1) voltage, and frequency (if applicable).

- c. Close switch S1.

- d. Apply specified (see 3.1) input conditions to turn the SSR on.

- e. Verify that the SSR shuts OFF by measuring the output current I(output).

- f. Reset SSR, then repeat twice the steps outlined in 4.7.7.5a through .7.7.5e. Repeating this turn-on into a shorted load test twice can be eliminated if the manufacturer has demonstrated process control under the SPC program (see 3.3.1), or other method that has been approved by the qualifying activity. If the design, material, technology, or processing of the part is changed or, if there are any quality problems or failures,

- the qualifying activity may require resumption of the specified testing. Deletion of testing does not relieve the manufacturer from meeting the test requirement in case of dispute.

# 4.7.7.6 Shorted load with SSR ON (see .13.12).

- a. Test setup in accordance with figure 1.

- b. Apply the specified (see 3.1) load, voltage, and frequency (if applicable).

- c. Apply specified (see 3.1) input conditions to turn the SSR on.

- d. Close switch S1.

- e. Verify the SSR shuts OFF by measuring the output current I(output).

- f. Reset SSR, then repeat twice the steps outlined in 4.7.7.6a through .7.7.6e. Repeating this shorted load test twice can be eliminated if the manufacturer has demonstrated process control under the SPC program (see 3.3.1), or other method that has been approved by the qualifying activity. If the design, material, technology, or processing of the part is changed or, if there are any quality problems or failures, the qualifying activity may require resumption of the specified testing. Deletion of testing does not relieve the manufacturer from meeting the test requirement in case of dispute.

## 4.7.7.7 Status turn-on time (see .13.13).

- a. Test setup in accordance with figure 1.

- b. Apply specified (see 3.1) load, voltage, and frequency (if applicable).

- c. Apply specified (see 3.1) input conditions, and activate the necessary status conditions to turn the status output ON.

- d. Verify that the status turn-on time is as specified (see .1).

## 4.7.7.8 Status "ON" voltage (see .13.14).

- a. Test setup in accordance with figure 1.

- b. Apply specified (see 3.1) load, voltage, and frequency (if applicable).

- Apply specified (see 3.1) input conditions, and activate the necessary status conditions to turn the status output ON.

- d. Verify that the status current I(status) is as specified (see .1) and that the status "ON" voltage  $V_s(on)$  is as specified (see 3.1).

# 4.7.7.9 Status turn-off time (see 3.13.15).

- a. Test setup in accordance with figure 1.

- b. Apply specified (see 3.1) load, voltage, and frequency (if applicable).

- c. Apply specified (see 3.1) input conditions, and activate the necessary status conditions to turn the status output OFF.

- d. Verify that the status turn-off time is as specified (see 3.1).

## 4.7.7.10 Status "OFF" voltage (see .13.16). a.

Test setup in accordance with figure 1.

b. Apply specified (see 3.1) load, voltage, and frequency (if applicable).

- c. Apply specified (see 3.1) input conditions, and activate the necessary status conditions to turn the status output OFF.

- d. Verify that the status current I(status) is as specified (see .1) and that the status "OFF" voltage  $V_s(off)$  is as specified (see 3.1).

# 4.7.7.11 Status blocking voltage (see 3.13.17).

- a. Test setup in accordance with figure 1.

- b. Apply specified (see 3.1) load, voltage, and frequency (if applicable).

- c. Apply specified (see 3.1) input conditions and necessary status turn off conditions.

- d. Apply the specified (see 3.1) status blocking voltage, V(status).

- e. Verify that the status current I(status) is as specified (see .1).

# 4.7.7.12 Status leakage current (see .13.18).

- a. Test setup in accordance with figure 1.

- b. Apply specified (see 3.1) load, voltage, and frequency (if applicable).

- c. Apply specified (see 3.1) input conditions and necessary status turn off conditions.

- d. Apply the maximum specified (see 3.1) status voltage V(status),

- e. Verify that the status leakage current I(status) is as specified (see .1).

# 4.7.7.13 Turn-on time (see .13.19).

- a. Test setup in accordance with figure 1.

- b. Apply the specified (see 3.1) load, voltage, and frequency (if applicable).

- c. Apply specified (see 3.1) input turn-on conditions.

- d. Verify that the SSR turns ON in the specified (see 3.1) time by measuring the output voltage V(output).

# 4.7.7.14 <u>Turn-off time (see 3.13.20)</u>.

- a. Test setup in accordance with figure 1.

- b. Apply the specified (see 3.1) load, voltage, and frequency (if applicable).

- Apply specified (see 3.1) input turn-on conditions, then apply the specified (see 3.1) input turn-off conditions.

- d. Verify that the SSR turns OFF in the specified (see .1) time by measuring the output voltage V(output).

# 4.7.7.15 Output voltage drop (see .13.21).

- a. Test setup in accordance with figure 1.

- b. Apply the specified (see 3.1) load, voltage, and frequency (if applicable).

- c. Apply specified (see 3.1) input turn-on conditions.

- d. Verify that the voltage drop is as specified (see .1) by measuring V(output).

## 4.7.7.16 Output leakage current (see .13.22).

- Test setup in accordance with figure 1.

- b. Apply the specified (see 3.1) load, voltage, and frequency (if applicable).

- c. Apply the necessary input conditions to turn the output off.

- d. Verify leakage current is as specified (see 3.1) by measuring I(output).

# 4.7.7.17 <u>Transient voltage (see .13.23)</u>.

- a. Test setup in accordance with figure 1.

- b. Apply the necessary input conditions to turn the output off.

- c. Apply the specified (see 3.1) voltage, and frequency (if applicable), and test load.

- d. For the specified (see 3.1) time apply the specified (see 3.1) transient voltage to the output of the SSR. For the purpose of test, a low current supply may be used.

- e. Monitor the output to verify that the SSR does not turn on.

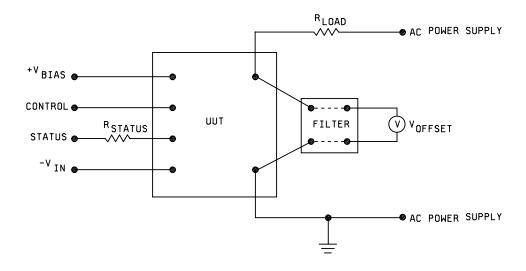

# 4.7.7.18 DC offset voltage (ac SSR's only) (see 3.13.24).

- a. Test setup in accordance with figure 2.

- b. Apply the specified (see 3.1) load, voltage, and frequency.

- c. Apply specified (see 3.1) input turn-on conditions.

- d. Verify the offset voltage is as specified (see 3.1) by measuring V (offset).

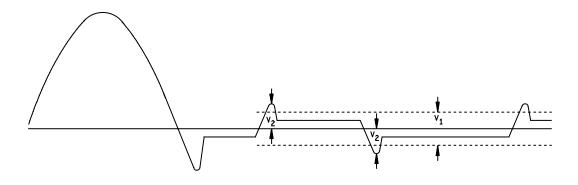

### 4.7.7.19 Waveform distortion (ac SSR's only) (see 3.13.25).

- a. Test setup in accordance with figure 1.

- b. Apply specified (see 3.1) load, voltage and frequency.

- c. Apply specified (see 3.1) input turn-on conditions.

- d. With SSR turned ON, verify that output voltage, V(output), is as specified (see .1) (see figure 3).

# 4.7.7.20 Minimum load current rating (ac SSR's only) (see 3.13.26).

- a. Test setup in accordance with figure 1.

- b. Apply specified (see 3.1) voltage and frequency, and minimum specified (see 3.1) load current.

- c. Apply specified (see 3.1) input turn-on conditions.

- d. Verify that the SSR turns ON and remains ON by measuring the output voltage, V(output).

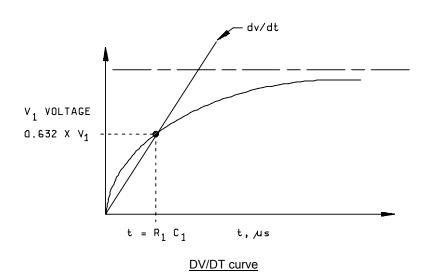

### 4.7.7.21 Exponential rate of voltage rise (dv/dt) (see .13.27).

- Test setup in accordance with figure 4, or equivalent as approved by the qualifying activity.

- b. Apply zero bias voltage (if applicable) and zero control voltage.

- c. Connect the output terminals of the SSR under test to the circuit of figure 4.

- d. Close and open S1 for a minimum of 10 times. After 5 cycles, reverse the polarity to the SSR (ac SSR's only). Verify that the SSR achieves the specified (see 3.1) output voltage within the specified (see .1) time by measuring V(output).

# 4.7.7.22 Zero crossing (ac SSR's only) (see 3.13.28).

- a. Test setup in accordance with figure 1.

- b. Apply specified (see 3.1) load, voltage and frequency.

- c. Apply specified (see 3.1) input turn-on conditions.

- d. Apply the input turn-on condition at 90°(±10°) and 270° (±10°) of the load supply voltage and monitor the output voltage waveform, V(output) for the moment of turn on. The maximum value of "zero" voltage turn-on shall be as specified (see 3.1).

- e. Apply the input turn-off condition at 90°(±10°) and 270° (±10°) of the load supply voltage and monitor the output current waveform, I(output), for the moment of turn off. The SSR shall not turn off with the removal of input conditions until the ac load current is below the specified (see .1) value.

FIGURE 2. DC offset voltage setup.

V<sub>1</sub> = WAVEFORM DISTORTION VOLTAGE (RMS)

V<sub>2</sub> = WAVEFORM DISTORTION VOLTAGE (PEAK)

FIGURE 3. Waveform distortion.

$V_1$  = Maximum rated output voltage (ac devices use  $V_1$  =  $V_{RATED}$  (RMS) x 1.414).

$R_1$  = See equation below.

$R_2$  = 1.0 megohm (±5 percent), 1/2 watt.

$R_3 = 50$  ohm (±5 percent).

$C_1 = 0.01 \, \mu F \, (\pm 5 \, percent).$

$S_1 = 10$  amp Hg wetted switch (or equivalent).

# DV/DT test setup

FIGURE 4. DV/DT.

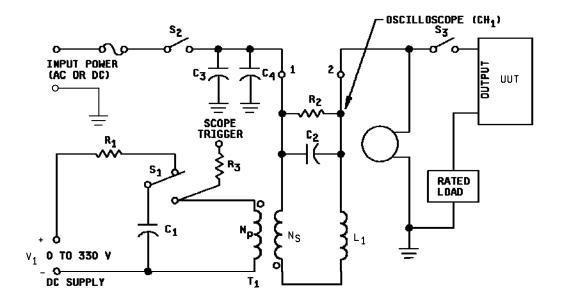

### 4.7.7.23 Electrical system spike, 25°C only. (see .13.29) (for qualification and periodic inspections only).

- a. Test setup in accordance with figure 5.

- b. With switch S3 open and S2 closed, cycle switch S1 and observe oscilloscope CH1 (or other equivalent instrument). Adjust V1 to obtain a minimum spike amplitude of 600 volts.

- c. Close switch S3 and cycle switch S1 at 10 pulses ± 1 pulse per second for the specified (see .1) time.

- d. Reverse the polarity of V1 and repeat 4.7.7.23b and .7.7.23c.

- e. After completion, the SSR shall be tested for output leakage current (see .7.7.16), turn on time (see 4.7.7.13), and turn off time (see 4.7.7.14).

# 4.7.7.24 Overload, 25°C only. (see .13.30) (for qualification and periodic inspections only).

- a. Test setup in accordance with figure 1.