# Integrated 10/100BASE-T/TX 9-Port Switch

#### GENERAL DESCRIPTION

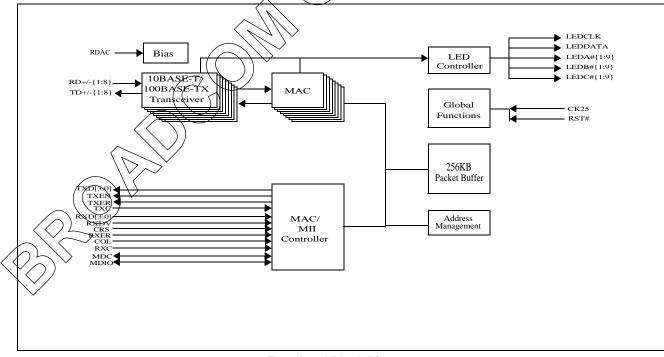

The AC508 is a nine-port, 10/100BASE-T/TX integrated switch targeted at cost-sensitive Fast Ethernet unmanaged switch systems. The device contains eight full-duplex 10BASE-T/ 100BASE-TX Fast Ethernet transceivers, each of which performs all of the physical layer interface functions for 10BASE-T Ethernet on CAT 3, 4 or 5 unshielded twisted pair (UTP) cable and 100BASE-TX Fast Ethernet on CAT 5 UTP cable.

The AC508 device provides a very highly integrated solution. It combines all of the functions of a high speed switch system, including packet buffer, transceivers, media access controllers, address management and a non-blocking switch controller, into a single monolithic 0.18 $\mu$ m CMOS device. It complies with the IEEE 802.3, 802.3u, and 802.3x specifications, including the MAC control PAUSE frame and Auto-Negotiation subsections, providing compatibility with all industry-standard Ethernet and Fast Ethernet devices.

The AC508 supports very low cost management utilizing the proprietary MIB Autocast<sup>TM</sup> function. This function requires only a small low cost microcontroller to initialize and configure the device.

#### FEATURES

- Nine-port 10/100 Mbps integrated switch controller,

- 256-KB on-chip Packet Buffer

- Eight integrated 10/100BASE-T/TX (EEE 802/30 Compliant Transceivers

- Integrated Full-Duplex Capable 802.3 Compliant Media Access Controllers

- Integrated Address Management

Supports up to 4K unicast addresses

- Ninth MII port provided for an additional TX/FX uplink

- Low-power 3.3 / 1.8 1.0 18mm CMOS Technology

- 208-pin PQFP package

#### Functional Block Diagram

AC508-DS00-R

# PRELIMINARY DATA SHEET AC508

### **REVISION HISTORY**

| AC508-DS00-R 08   | 3/14/01                 | Initial Release                                                                                                 |  |

|-------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------|--|

|                   |                         |                                                                                                                 |  |

|                   |                         |                                                                                                                 |  |

|                   |                         |                                                                                                                 |  |

|                   |                         |                                                                                                                 |  |

|                   |                         |                                                                                                                 |  |

|                   |                         |                                                                                                                 |  |

|                   |                         |                                                                                                                 |  |

|                   |                         |                                                                                                                 |  |

|                   |                         |                                                                                                                 |  |

|                   |                         |                                                                                                                 |  |

|                   |                         |                                                                                                                 |  |

|                   |                         |                                                                                                                 |  |

|                   |                         |                                                                                                                 |  |

|                   |                         |                                                                                                                 |  |

|                   |                         |                                                                                                                 |  |

| /.                |                         | $)\rangle$                                                                                                      |  |

| 1                 |                         |                                                                                                                 |  |

|                   | $\mathbf{n} \mathbf{n}$ |                                                                                                                 |  |

|                   | $\searrow$              |                                                                                                                 |  |

|                   | $\rightarrow$           |                                                                                                                 |  |

| $(\bigcirc)$      |                         |                                                                                                                 |  |

|                   |                         |                                                                                                                 |  |

| 225               |                         |                                                                                                                 |  |

| $\langle \rangle$ |                         | Broadcom Corporation<br>P.O. Box 57013                                                                          |  |

| $\checkmark$      |                         | P.O. Box 57013<br>16215 Alton Parkway                                                                           |  |

|                   |                         | 16215 Alton Parkway<br>Irvine, CA 92619-7013<br>© Copyright 2001 by Broadcom Corporation<br>All rights reserved |  |

All rights reserved Printed in the U.S.A.

Broadcom<sup>®</sup> and the pulse logo<sup>®</sup> are registered trademarks of Broadcom Corporation and/or its subsidiaries in the United States and certain other countries. All other trademarks are the property of their respective owners.

### TABLE OF CONTENTS

| Overview                         | ······································ |

|----------------------------------|----------------------------------------|

| Global Functions                 |                                        |

| Clocks                           |                                        |

| Reset                            |                                        |

| Physical Layer Transceivers      |                                        |

| Encoder/Decoder                  |                                        |

| Link Monitor                     |                                        |

| Collision Detection              |                                        |

| Auto-Negotiation                 | /                                      |

| Digital Adaptive Equalizer       |                                        |

| ADC                              |                                        |

| Digital Clock Recovery/Generator |                                        |

| Baseline Wander Correction       |                                        |

| Digital to Analog Converter      |                                        |

| Stream Cipher                    |                                        |

| MII Management                   |                                        |

| Media Access Controllers         |                                        |

| Receive Function                 |                                        |

| Transmit Function                |                                        |

| Flow Control                     |                                        |

| Address Management               |                                        |

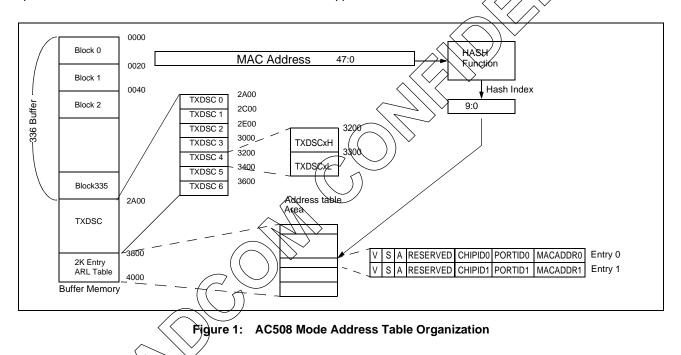

| Address Table Organization       |                                        |

| Reserved Addresses               |                                        |

| Learning                         | 8                                      |

| Resolution                       | 8                                      |

| Aging                            | 8                                      |

| Hash Function                    |                                        |

| Switch Controller                |                                        |

| Buffer Management                |                                        |

| Memory Arbitration               |                                        |

| Transmit Output Port Queues      |                                        |

| 9 Clocking                             |        |

|----------------------------------------|--------|

| Clocking                               |        |

|                                        |        |

| MII/7-Wire Port                        |        |

| MII MAC Port10                         |        |

| LED Interfaces11                       |        |

| Parallel LED Interface                 | $\geq$ |

| Serial LED Interface                   |        |

| Load Meter LED                         |        |

| Configuration                          |        |

| Section 2: Hardware Signal Definitions |        |

| Section 3: Pin Assignments             |        |

| Section 4: Timing Characteristics      |        |

| Section 5: Electrical Characteristics  |        |

| Section 6: Mechanical Information      |        |

| Section 7: Ordering Information        |        |

|                                        |        |

### LIST OF TABLES

| Table 1:  | Flow Control Modes                        | 5             |

|-----------|-------------------------------------------|---------------|

| Table 2:  | Behavior for Reserved Multicast Addresses | 7             |

| Table 3:  | LED Status Types                          | . 14          |

| Table 4:  | LED Mode Matrix (Cont.)                   | <b>&gt;14</b> |

| Table 5:  | Load Meter LED Decode                     | . 15          |

| Table 6:  | Signal Descriptions                       | . 17          |

| Table 7:  | Pin Assignment by Pin Number              | . 21          |

| Table 8:  | Pin Assignment by Signal Name             | . 23          |

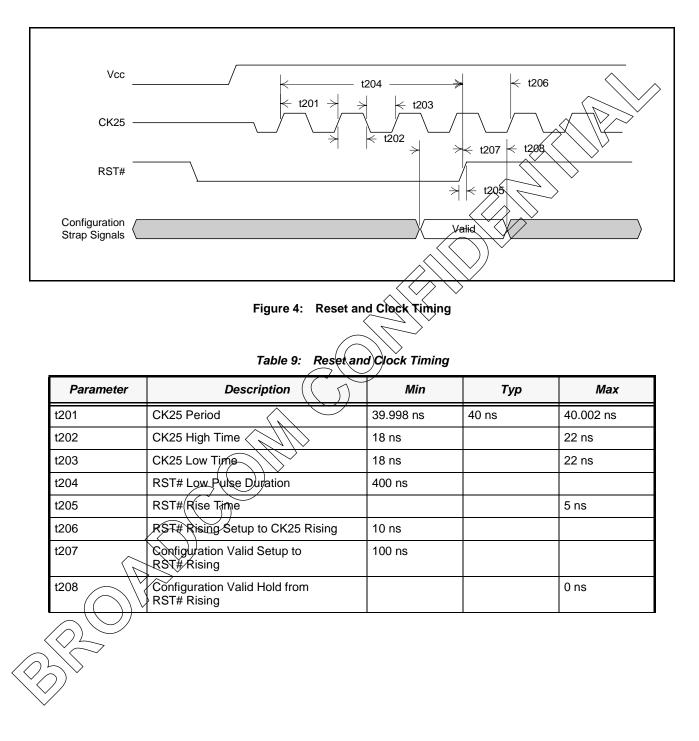

| Table 9:  | Reset and Clock Timing                    | . 25          |

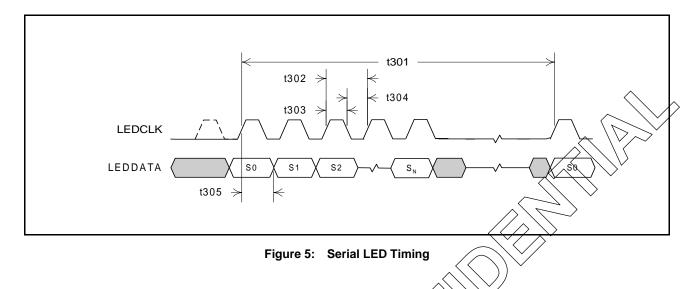

| Table 10: | Serial LED Timing                         | . 26          |

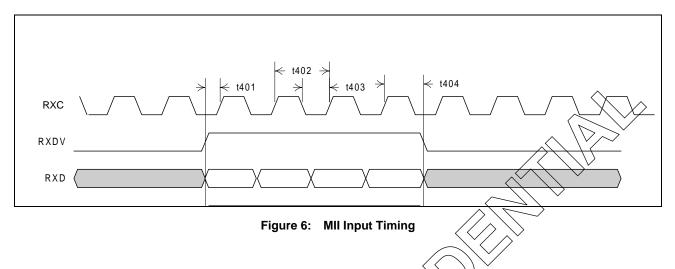

| Table 11: | MII Input Timing                          | . 27          |

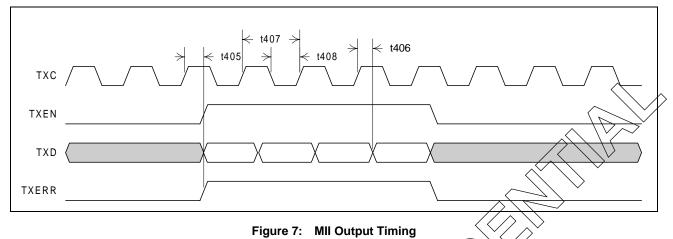

| Table 12: | MII Output Timing                         | . 28          |

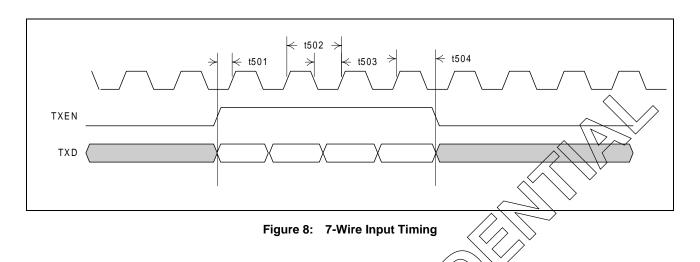

| Table 13: | 7-Wire Input Timing                       | . 29          |

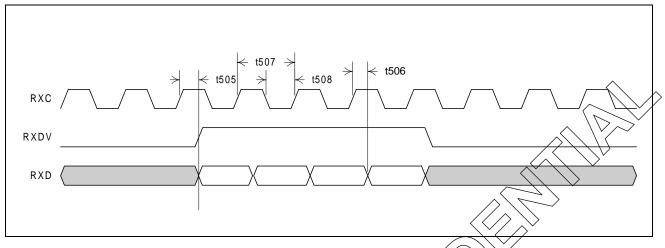

| Table 14: | 7-Wire Output Timing                      | . 30          |

| Table 15: | Absolute Maximum Ratings                  | . 31          |

| Table 16: | Recommended Operating Condition           | . 31          |

| Table 17: | Electrical Characteristics                | . 32          |

|           |                                           |               |

## LIST OF FIGURES

| Figure 1:  | AC508 Mode Address Table Organization |  |

|------------|---------------------------------------|--|

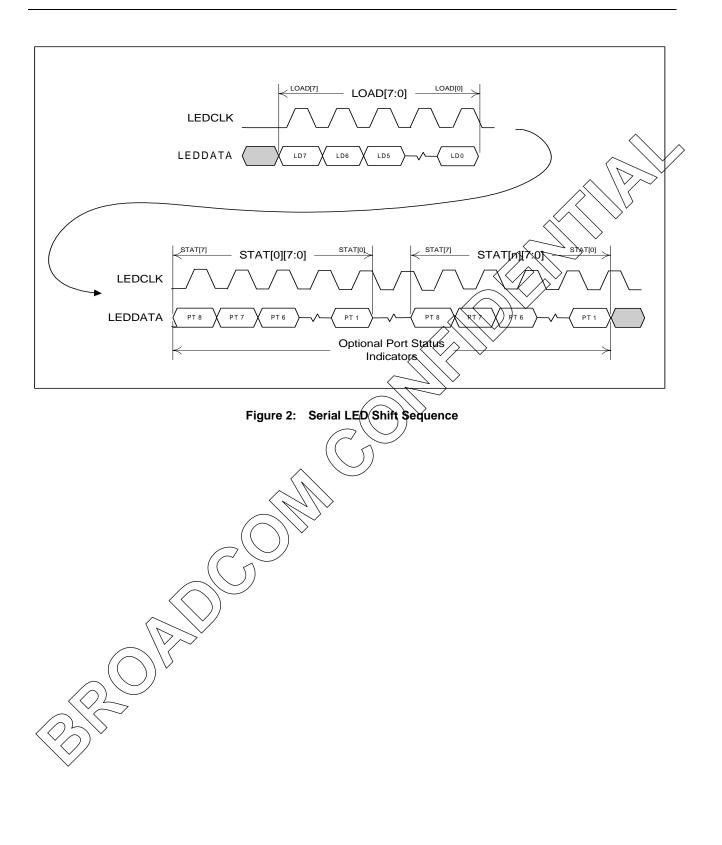

| Figure 2:  | Serial LED Shift Sequence             |  |

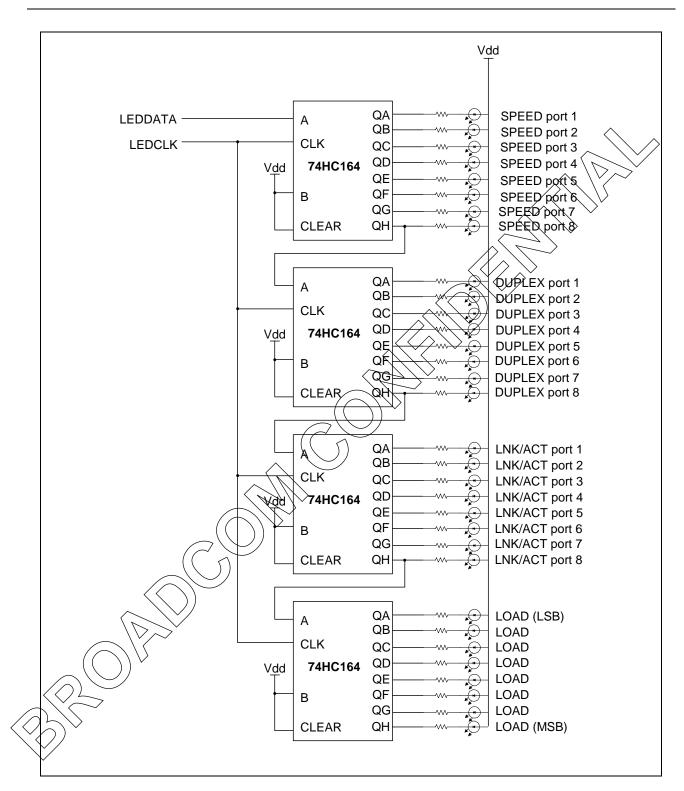

| Figure 3:  | External Circuit for Serial LED Mode  |  |

| Figure 4:  | Reset and Clock Timing                |  |

| Figure 5:  | Serial LED Timing                     |  |

| Figure 6:  | MII Input Timing                      |  |

| Figure 7:  | MII Output Timing                     |  |

| Figure 8:  | 7-Wire Input Timing                   |  |

| Figure 9:  | 7-Wire Output Timing                  |  |

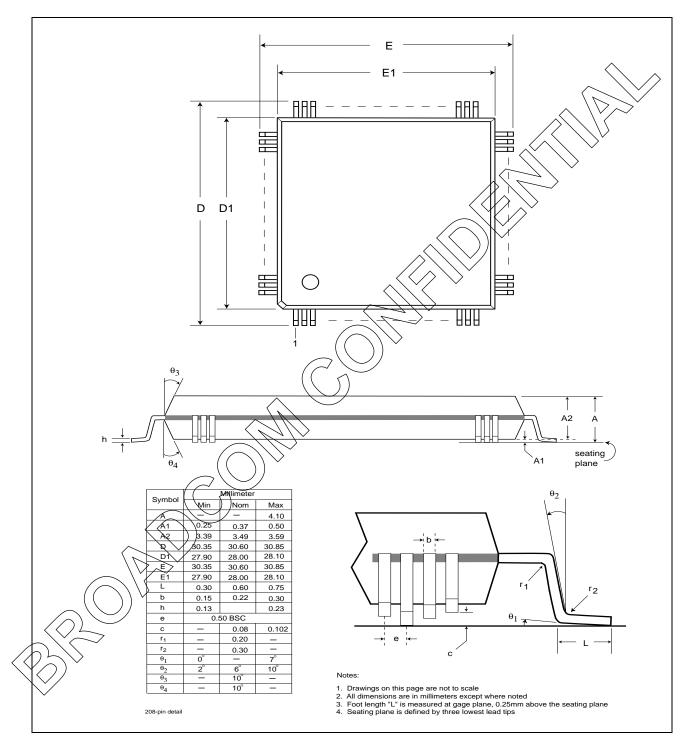

| Figure 10: | 208-MQFP Package Outline Drawing      |  |

|            |                                       |  |

### Section 1: Functional Description

#### **OVERVIEW**

The AC508 is a single-chip, nine-port 10/100BASE-TX switch device. This device integrates eight 10/100BASE-TX transceivers, one general use (10/100BASE-TX/FX) MII, nine full-duplex capable Media Access Controllers (MACs), a Serial Management Port, high-performance integrated packet buffer memory, an address resolution engine, a non-blocking switch controller.

The integrated 10/100BASE-TX transceivers perform all the physical layer interface functions for 100BASE-TX full-duplex or half-duplex Ethernet on CAT 5 twisted pair cable and 10BASE-T full- or half-duplex Ethernet on CAT 3, 4, or 5 cable.

The transceiver performs 4B5B, MLT3, NRZI, and Manchester encoding and decoding, clock and data recovery, stream cipher scrambling/descrambling, digital adaptive equalization, line transmission, carrier sense and link integrity monitor, auto-negotiation and MII management functions. Each of the eight integrated transceiver ports of the AC508 connects directly to the network media through isolation transformers. The integrated transceiver is tulk compliant with the IEEE 802.3 and 802.3u standards.

The device provides nine internal media access controllers. Each MAC is dual-speed and both half- and full-duplex capable. Flow control is provided in the half-duplex mode with backpressure. In full-duplex mode, 802.3x frame-based flow control is provided. The MAC is 802.3 compliant and supports a maximum frame size of 1536 bytes.

An integrated address management engine provides address leaving and recognition functions at maximum frame rates. The address table provides capacity for up to 4K unicast addresses. Addresses are added to the table after receiving an error-free packet. Broadcast and multicast frames are forwarded to all ports except the port where it was received.

#### **GLOBAL FUNCTIONS**

#### CLOCKS

The device requires a single 25-MHz clock signal at the CK25 input pin. The other clock option is using a 25-Mhz crystal at XTALI/CK25 and XTALO pins. An internal PLL derives all the clock frequencies needed by the device from the single clock input. The device generates all internal clocks to the packet buffer memory. When using a ninth MII port, an additional 25-MHz receive and transmit clock must be supplied by the external transceiver.

#### RESET

A power-on, or hard reset, is initiated by an active low reset pulse on the RST# signal pin. An internal circuit guarantees a sufficiently long reset pulse is applied to all internal circuits. The initialization process loads all pin configurable modes, resets all internal processes and returns them to an idle state, and initializes the memory structure. At the completion of the reset sequence, all ports are enabled for frame reception and transmission.

Byring initialization, the CK25 input signal must be active and the power supply to the device stable.

### PHYSICAL LAYER TRANSCEIVERS

#### ENCODER/DECODER

In 100BASE-TX mode, the transceiver transmits and receives a continuous data stream on twisted pair. During transmission, nibble wide (4-bit) data from the MAC is encoded into 5-bit code groups and inserted into the transmit data stream. The transmit packet is encapsulated by replacing the first 2 nibbles of preamble with a start of stream delimiter (J/K codes) and appending an end of stream delimiter (T/R codes) to the end of the packet. When the MII transmit error input is asserted during a packet, the transmit error code group (H) is sent in place of the corresponding data code group. The transmitter repeatedly sends the idle code group in between packets.

In TX mode, the encoded data stream is scrambled by a stream cipher block and then serialized and encoded into MLT3 signal levels. A multimode transmit DAC is used to drive the MLT3 data onto the twisted pair cable.

Following baseline wander correction, adaptive equalization and clock recovery in TX mode, the receive data stream is converted from MLT3 to serial NRZ data. The NRZ data is descrambled by the stream either block and then deserialized and aligned into 5-bit code groups.

The 5-bit code groups are decoded into 4-bit data nibbles and provided as the input data stream to the MAC. The start of stream delimiter is replaced with preamble nibbles and the end of stream delimiter and idle codes are replaced with all zeros. When an invalid code group is detected in the data stream, the transceiver asserts a receiver error indication to the MAC.

In 10BASE-T mode, Manchester encoding and decoding is performed on the data stream. The multimode transmit DAC performs pre-equalization for 100 meters of CAT 3 cable.

#### LINK MONITOR

In 100BASE-TX mode, receive signal energy is detected by monitoring the receive pair for transitions in the signal level. Signal levels are qualified using squelch detect circuits. When no signal or certain invalid signals are detected on the receive pair, the link monitor enters and remains in the Link Fail state where only idle codes will be transmitted. When a valid signal is detected on the receive pair for a minimum period of time, the link monitor enters the Link Pass state and the transmit and receive functions are enabled.

In 10BASE-T mode, a link-pulse detection circuit constantly monitors the RD+/- pins for the presence of valid link pulses.

#### **COLLISION DETECTION**

In half-duplex mode, collisions are detected whenever the transceiver is simultaneously transmitting and receiving activity.

#### AUTO-NEGOTIATION

Each internal transceiver contains the ability to negotiate its mode of operation over the twisted pair link using the autonegotiation mechanism defined in the IEEE 802.3u specification. During auto-negotiation, each port automatically chooses its mode of operation by advertising its abilities and comparing them with those received from its link partner. The AC508 is configured to advertise 802.3x flow-control capability, and can also advertise that it is Next Page capable. The transceiver negotiates with its link partner and chooses the highest level of operation available for its own link. In FDX mode, flow control is also negotiated. In HDX mode, flow control is enabled/disabled based on pin strappings. The auto-negotiation algorithm supports the Parallel Detection function for legacy 10BASE-T devices and 100BASE-TX-only devices that do not support auto-negotiation.

#### DIGITAL ADAPTIVE EQUALIZER

The digital adaptive equalizer removes inter-symbol interference created by the transmission channel media. The equalizer accepts sampled unequalized data from the ADC on each channel and produces equalized data. The AC508 achieves an optimum signal-to-noise ratio by using a combination of feed-forward equalization and decision-feedback equalization. This

Broadcom Corporation

### Preliminary Data Sheet

08/14/01

powerful technique achieves a 100BASE-TX BER of less than  $1 \times 10^{-12}$  for transmission up to 100 meters on CAT 5 twistedpair cable, even in harsh noise environments. The digital adaptive equalizers in the AC508 achieve performance close to theoretical limits. The all-digital nature of the design makes the performance very tolerant to on-chip noise. The filter coefficients are self-adapting to any quality of cable or cable length. Due to transmit pre-equalization in 10BASE-T mode and complete lack of ISI in 100BASE-FX mode, the adaptive equalizer is bypassed in these two modes.

### ADC

The receive channel has a 6-bit, 125-MHz analog-to-digital converter (ADC). The ADC samples the incoming data on the receive channel and produces a 6-bit output. The output of the ADC is fed to the digital adaptive equalizer. Advanced analog circuit techniques achieve low-offset, high-power supply noise rejection, fast settling time, and low bit error rate.

#### DIGITAL CLOCK RECOVERY/GENERATOR

The all-digital clock recovery and generator block creates all internal transmit and receive clocks. The transmit clock is locked to the 25-MHz clock input while the receive clock is locked to the incoming data stream. Clock recovery circuits optimized to MLT3, NRZI, and Manchester encoding schemes are included for use with each of the three different operating modes. The input data stream is sampled by the recovered clock and fed synchronously to the digital adaptive equalizer.

#### **BASELINE WANDER CORRECTION**

A 100BASE-TX data stream is not always DC balanced. Because the receive signal must pass through a transformer, the DC offset of the differential receive input can wander. This effect, known as baseline wander, can greatly reduce the noise immunity of the receiver. The transceiver automatically compensates for baseline wander by removing the DC offset from the input signal, and thereby significantly reduces the chance of a receive symbol error.

#### DIGITAL TO ANALOG CONVERTER

The multimode transmit digital-to-analog converter (DAG) transmits MLT3-coded symbols in 100BASE-TX mode and Manchester-coded symbols in 10BASE-T mode. It performs programmable edge-rate control in TX mode, which decreases unwanted high frequency signal components, thus reducing EMI. High-frequency pre-emphasis is performed in 10BASE-T mode. The transmit DAC utilizes a current drive output that is well balanced and produces very low noise transmit signals.

#### STREAM CIPHER

In 100BASE-TX mode, the transmit data stream is scrambled to reduce radiated emissions on the twisted-pair cable. The data is scrambled by exclusive Oring the NRZ signal with the output of an 11-bit-wide linear feedback shift register (LFSR), which produces a 2047-bit, non-repeating sequence. The scrambler reduces peak emissions by randomly spreading the signal energy over the transmit frequency range and eliminating peaks at certain frequencies.

The receiver descrambles the incoming data stream by exclusive Oring it with the same sequence generated at the transmitter. The descrambler detects the state of the transmit LFSR by looking for a sequence representing consecutive idle codes. The descrambler locks to the scrambler state after detecting a sufficient number of consecutive idle code groups. The receiver does not attempt to decode the data stream unless the descrambler is locked. When locked, the descrambler continuously monitors the data stream to make sure that it has not lost synchronization. The receive data stream is expected to contain inter-packet idle periods. If the descrambler does not detect enough idle codes within 724 µs, it becomes unlocked, and the receive decoder is disabled. The descrambler is always forced into the unlocked state when a link failure condition is dejected.

Stream cipher scrambling/descrambling is not used in 10BASE-T modes.

#### **MII MANAGEMENT**

Each transceiver within the AC508 contains a complete set of MII management registers. The 5-bit transceiver address is assigned by concatenation of the 2-bit 00 and the internal 3-bit port ID. All MII Management registers can be accessed through the shared MII Management Port using the MDC and MDIO signals, or through the Serial Management Port.

### **MEDIA ACCESS CONTROLLERS**

The AC508 contains nine internal dual-speed MACs. The MACs automatically select 10- or 100-Mbit mode, CSMA/CD or full-duplex, based on the result of auto-negotiation. In FDX mode, 802.3x PAUSE-frame-based flow control is also determined through auto-negotiation. The MACs are compliant with IEEE 802.3, 802.3u, and 802.3x specifications.

#### **RECEIVE FUNCTION**

The MAC initiates frame reception following the assertion of receive data valid indication from the physical layer. The MAC monitors the frame for the following error conditions:

- Receive error indication from the PHY

- Runt frame error if frame is fewer than 64 bytes

- CRC error

- Long frame error if frame is greater than 1536 bytes

If no errors are detected the frame is processed by the switch controller. Frames with errors are discarded.

#### **TRANSMIT FUNCTION**

Frame transmission begins with the switch controller quering a frame to the MAC transmitter. The frame data is transmitted as received from the switch controller. The transmit controller is responsible for preamble insertion, carrier deferral, collision backoff, and inter-packet gap enforcement.

In half-duplex mode, when a frame is queued for transmission, the transmit controller behaves as specified by the 802.3 requirements for frame deferral. Following deterral, the transmitter adds 8 bytes of preamble and SFD to the frame data received from the switch controller. If, during frame transmission, a collision is observed and the collision window timer has not expired, the transmit controller asserts jam and then executes the backoff algorithm. The frame is retransmitted when appropriate. On the sixteenth consecutive collision the backoff algorithm starts over at the initial state, the collision counter is reset and attempts to transmit the current frame continue. Following a late collision, the frame is aborted and the switch controller is allowed to queue the next frame for transmission.

While in full-duplex mode, the transmit controller ignores carrier activity and collision indication. Transmission begins after the switch controller queues the frame and the 96 bit times of IPG have been observed.

### FLOW CONTROL

The AC508 implements an intelligent flow control algorithm to minimize the system impact resulting from flow control measures. Buffer memory allocation is adaptive to the status of each port's speed and duplex mode, providing an optimal balance between flow management and per-port memory depth. The AC508 initiates flow control in response to buffer memory conditions on a per-port basis.

The MACs are capable of flow control in both full-and half-duplex modes. In half-duplex mode, the MAC backpressures a receiving port by transmitting a 96-bit time-jam packet to the port. A single jam packet is asserted for each received packet for the duration of the time the port is in the flow control state.

#### Broadcom Corporation

Flow control in full-duplex mode functions as specified by the IEEE 802.3x requirements. In the receiver, MAC flow control frames are recognized and, when properly received, set the flow control pause time for the transmit controller. The pause time is assigned from the 2-byte pause time field following the pause opcode. MAC control PAUSE frames are not forwarded from the receiver to the switch controller.

When the switch controller requests flow control from a port, the transmit controller transmits a MAC control PAUSE frame with the pause time set to the PAUSE\_QUANTA register value (default is set to maximum). When the condition that caused the flow control state is no longer present, a MAC control PAUSE frame is sent with the pause time field set to Q.

The flow control capabilities of the AC508 are enabled based on the results of auto-negotiation and the state of the ENFDXFLOW and ENHDXFLOW control signals loaded during reset. Flow control in half-duplex mode is independent of the state of the link partner's flow control capability. See Table 1 for more detailed information.

|         |           |           | FLOW CONTROL |             |  |

|---------|-----------|-----------|--------------|-------------|--|

| LPFCCAP | ENFDXFlow | ENHDXFLOW | Full Duplex  | Half Duplex |  |

| Х       | Х         | 0         |              | Disabled    |  |

| Х       | Х         | 1         |              | Enabled     |  |

| 0       | 0         | Х         | Disabled     | -           |  |

| 0       | 1         | Х         | Disabled     | -           |  |

| 1       | 0         | Х         | Disabled     | -           |  |

| 1       | 1         | X         | Enabled      | -           |  |

Table 1: Flow Control Modes

Note: LPFCCAP: Link Partner Flow Control Capability-Obtained from Result of auto-negotiation.

#### **ADDRESS MANAGEMENT**

The AC508 Address Resolution Logic contains the following features:

- The 'two-bin per bucket" address table configuration

- Hashing of the DA MAC address to generate the address table pointer

The address management unit of the AC508 provides packet rate learning and recognition functions. The address table supports 2K unicast addresses in the 256 KB on-chip memory. Although the address table shares the packet buffer memory, adequate memory bandwidth is provided for both functions to operate at maximum packet rate.

#### Address Table Organization

The address table is in the bottom of the internal SRAM, occupying the address range from 3800 to 3FKP. Each bucket contains two entries (or bins). The address table is organized into 1K buckets with two entries in each bucket. This allows up to two MAC addresses with the same index bits to be mapped into the address table.

The index into the address table is computed from the MAC address using a hash algorithm. The hash algorithm uses the CRC-CCITT polynomial. The 48-bit MAC address is reduced to a 16 bit CRC hash value. Bits 9:0 of the CRC are used index the 2k address(table.)

The CRC-CCI) T polynomial is:  $x^{16} + x^{12} + x^{5} + 1$

Hashing can be disabled by setting HASH\_DISABLE = 1 in the ARL Configuration register, in which case the AC508 device will revent to the direct addressing method.

#### **RESERVED ADDRESSES**

The AC508 treats certain of the 802.1 administered "reserved multicast" destination addresses in specific ways, dependent on the mode of operation. Table 2 defines the response to these reserved multicast addresses.

#### Broadcom Corporation

| MAC Address                    | Function                                    | 802.1 Specified<br>Action | Action                                                                    |  |

|--------------------------------|---------------------------------------------|---------------------------|---------------------------------------------------------------------------|--|

| 01-80-C2-00-00-00              | Bridge Group Address                        | Drop Frame                | Forward Frame                                                             |  |

| 01-80-C2-00-00-01              | IEEE Std 802.3x MAC Control<br>Frame        | Drop Frame                | Receive MAC<br>Determines if Valid<br>PAUSE Frame and Acts<br>Accordingly |  |

| 01-80-C2-00-00-02              | RESERVED                                    | Drop Frame                | Drop Frame                                                                |  |

| 01-80-C2-00-00-03              | RESERVED                                    | Drop Frame                | Drop Frame                                                                |  |

| 01-80-C2-00-00-04              | RESERVED                                    | Drop Frame                | Drop Frame                                                                |  |

| 01-80-C2-00-00-05              | RESERVED                                    | Drop Frame                | Drop Frame                                                                |  |

| 01-80-C2-00-00-06              | RESERVED                                    | Drop Frame                | Drop Frame                                                                |  |

| 01-80-C2-00-00-07              | RESERVED                                    | Drop Frame                | Ørop Frame                                                                |  |

| 01-80-C2-00-00-08              | RESERVED                                    | Drop Frame                | Drop Frame                                                                |  |

| 01-80-C2-00-00-09              | RESERVED                                    | Drop Frame                | Drop Frame                                                                |  |

| 01-80-C2-00-00-0A              | RESERVED                                    | Drop Frame                | Drop Frame                                                                |  |

| 01-80-C2-00-00-0B              | RESERVED                                    | Drop Frame                | Drop Frame                                                                |  |

| 01-80-C2-00-00-0C              | RESERVED                                    | Drop Frame                | Drop Frame                                                                |  |

| 01-80-C2-00-00-0D              | RESERVED                                    | Drop Frame                | Drop Frame                                                                |  |

| 01-80-C2-00-00-0E              | RESERVED                                    | Drop Frame                | Drop Frame                                                                |  |

| 01-80-C2-00-00-0F              | RESERVED                                    | Drop Frame                | Drop Frame                                                                |  |

| 01-80-C2-00-00-10              | All LANs Bridge Management<br>Group Address | Forward Frame             | Forward Frame                                                             |  |

| 01-80-C2-00-00-20              | GMRP address                                | Forward Frame             | Forward Frame                                                             |  |

| 01-80-C2-00-00-21              | GVRP address                                | Forward Frame             | Forward Frame                                                             |  |

| 01-80-C2-00-00-22              | RESERVED                                    | Forward Frame             | Forward Frame                                                             |  |

| 01-80-C2-00-00-23              | RESERVED                                    | Forward Frame             | Forward Frame                                                             |  |

| 01-80-C2-00 <sub>7</sub> 00-24 | RESERVED                                    | Forward Frame             | Forward Frame                                                             |  |

| 01-80-C2-00-00-25              | RESERVED                                    | Forward Frame             | Forward Frame                                                             |  |

| 01-80-C2-00-00-26              | RESERVED                                    | Forward Frame             | Forward Frame                                                             |  |

| 01-80-62-00-00-27              | RESERVED                                    | Forward Frame             | Forward Frame                                                             |  |

| 01-80-02-00-00-28              | RESERVED                                    | Forward Frame             | Forward Frame                                                             |  |

| 01-80-C2-00-00-29              | RESERVED                                    | Forward Frame             | Forward Frame                                                             |  |

| §1-80-C2-00-00-2A              | RESERVED                                    | Forward Frame             | Forward Frame                                                             |  |

| 01-80-C2-00-00-2B              | RESERVED                                    | Forward Frame             | Forward Frame                                                             |  |

| 01-80-C2-00-00-2C              | RESERVED                                    | Forward Frame             | Forward Frame                                                             |  |

| 01-80-C2-00-00-2D              | RESERVED                                    | Forward Frame             | Forward Frame                                                             |  |

| 01-80-C2-00-00-2E              | RESERVED                                    | Forward Frame             | Forward Frame                                                             |  |

| 01-80-C2-00-00-2F              | RESERVED                                    | Forward Frame             | Forward Frame                                                             |  |

| Table 2: Behavior for Reserved Multicast Address | əs |

|--------------------------------------------------|----|

|--------------------------------------------------|----|

#### LEARNING

During the receive process the source address (SA) of the packet is saved until completion of the packet. The address is stored in the address table memory if the following conditions are met:

- The packet is not from the Management port.

- The packet has been received without error.

- The packet is of legal length.

- The packet has a unicast address.

- There is a free space available in one of the two entries in the bucket that the hashed address indexes to. If there is no free space available in the bucket, the address is not learned.

When learning, the MAC address and the source port ID is stored into the address table. The VALID bit is set, the AGE bit is set.

#### RESOLUTION

The destination address (DA) of the received packet is used by the address resolution function to search the address table and assign a destination port for the packet. The destination port is assigned by locating a matching address in the address table and selecting the source port identifier field as the destination port. The search for a matching address occurs only for unicast packets. The address resolution function for unicast packets proceeds as follows:

- The lower 11 bits of the DA are used as a pointer into the address table memory and both entries in the bucket are retrieved. The address resolution logic processes the two entries in parallel.

- If the valid indicator is set and the address stored at one of the locations matches the DA of the packet received, the port identifier is assigned to be the destination port of the packet.

- If the destination port matches the source port, the packet is not forwarded.

- If the valid indicator is not set or the address stored does not match the DA address of the packet, the packet is forwarded as a broadcast packet and will be transmitted to all other ports.

- If the DA matches the globally assigned multicast address of the 802.3x MAC Control PAUSE frame of 01-80-C2-00-00-01, the packet is not forwarded.

- If the DA matches the Bridge Group Address, the packet is forwarded to all ports except the source port.

- If the DA matches one of the other globally assigned reserved address (between 01-80-C2-00-00-02 and 01-80-C2-00-00-05), the packet is not forwarded

- All other multicast and broadcast packets are forwarded to all ports except the source port and the Management Port.

#### AGING

The Aging process periodically removes dynamically learned addresses. The AGE\_TIME is a timer with a value of 300 s. For each entry in the Address Table, the Aging process performs the following:

- If the VALID bit is not set, do nothing.

- If the VALD bit is set, and the AGE bit is set, reset the AGE bit. This keeps the entry in the table.

- If the VALID bit is set, and the AGE bit is reset, reset the VALID bit. This effectively deletes the entry from the Address

#### **HASH FUNCTION**

The address resolution logic incorporates a hash function to randomize storage location for the MAC address. The hash function can be disabled using the HASH\_DISABLE bit in the Switch Mode register.

#### **SWITCH CONTROLLER**

The core of the AC508 device is a cost effective and high performance switch controller. The controller manages packet forwarding between the MAC receive and transmit ports through the frame buffer memory with a stole and forward architecture. The switch controller encompasses the functions of buffer management, memory arbitration and transmit descriptor queueing.

#### **BUFFER MANAGEMENT**

The frame buffer memory is divided into 256 bytes per page. Each packet received may affected more than one page, of which, six pages are required for store maximum 1536B frame data. Frame data is stored to the memory block as the packet is received. After reception, the frame is queued to the egress port(s) transmit queue. For unicast frames, following transmission of a packet from the frame buffer memory, the block of memory to the frame is released to the free buffer pool. If the frame is destined to multiple ports, the memory block is not released until all ports complete transmission of the frame.

#### **MEMORY ARBITRATION**

Processes requesting access to the internal memory include the receive and transmit frame data handlers, address resolution, learning and aging functions, and output port queue managers. These processes are arbitrated to provide fair access to the memory and minimize latency of critical processes to provide a fully non blocking solution.

### TRANSMIT OUTPUT PORT QUEUES

When the Quality of Service (QoS) function is turned off, the switch controller maintains an output port queue for each port. The queues are located in the internal memory and the maximum depth of the queue is 336 (i.e., 336 transmit descriptors). The queue depth becomes 256 for each output port when the QoS function is on. Transmit descriptors are updated after the packet has been received and the destination port resolved. One or two transmit descriptors are assigned to each destination port queue linking the destination with the frame data. For packets which have frame sizes larger than 1024 bytes, two transmit descriptors are required. In the case of multicast and broadcast packets, a transmit descriptor for the packet is assigned to the transmit descriptor queues of multiple ports.

For each port, frames are initiated for transmission with minimum IPG until the transmit descriptor queue of the port is empty.

### INTEGRATED HIGH-PERFORMANCE MEMORY

The AC508 includes 256 KB of integrated, high-performance RAM which stores all packet buffer and address table information; and eliminates the need for external memory. This allows for the implementation of extremely low-cost systems.

The internal RAM controller efficiently executes memory transfers and achieves non-blocking performance.

#### CLOCKING

The AC508 provides simple clock selection. From a single 25-MHz clock input, the device's internal clocks operate up to 83 MHz; this affects the operation of the system logic and internal RAM.

#### **MII/7-WIRE PORT**

The AC508 provides a fully 802.3u compatible MII as well as 7 Wire interface as a ninth network port. The port can be configured to operate differently dependent on the programming of the internal registers.

#### **MII MAC PORT**

In its default mode after power-up, the MII operates as a normal MAC-based MII port, capable of interfacing directly to an external TX or FX transceiver. The port incorporates a ninth internal MAC, and functions identically to the eight integrated 10/100 ports. By using the strap pin, the ninth network port can be configured to use a 7-Wire interface. The 7-Wire interface enables glueless connection to legacy processors for management functions.

Broadcom Corporation

#### LED INTERFACES

The AC508 provides visibility per port of link status, port speed, duplex mode, combined transmit and receive activity, and collision. Both a parallel and serial interface are supplied to drive the status to the LEDs. The parallel interface provides the lowest cost solution for implementing LEDs. However, as the port density of the system increases, the number of signals required for the parallel implementation may become prohibitively large. In these cases, the serial mode will be more appropriate. The serial interface provides up to 5 status indications per port; whereas, the parallel interface indicates only up to three. Combinations of serial and parallel status can also be effective in lowering the system cost.

During power-on and reset, the parallel LED signals are driven low and the serial interface shifts a continuous low value for 1.34s.

#### PARALLEL LED INTERFACE

Three pins per port, including the MII port, are provided for directly driving LED status: LEDA#, LEDB#, LEDC#. The LED mode configuration signals control the LED status type driven by each pin. Table 3 on page 14 describes the selectable status types and Table 4 on page 14 gives a complete LED mode matrix for parallel interface.

#### SERIAL LED INTERFACE

A two pin serial interface, LEDDATA and LEDCLK, provides data and clock to enable external shift registers to capture the LED status indications from the AC508 for each internal port. The status encapsulated within the shift sequence is configured by the LED mode configuration signals. The configuration signals select both the number of status bits per port and the status type of each bit. The serial interface also provides an 8-bit value indicating the percentage of total bandwidth used by the switch.

The LEDCLK is generated by dividing the 25 MHz input clock by 16, providing a 640 ns clock period. The LEDDATA outputs are generated on the falling edge of the LEDCLK, and have adequate setup and hold time to be clock externally on the rising edge of LEDCLK. The shift sequence is a consecutive stream of 8-bit status words. The first word of the sequence is the LOAD status, followed by optional port status words. Each 8-bit port status word contains one bit for each port of the designated LED status type. The words are shifted MSB first. For a port status word, the MSB corresponds to port 7. The shift sequence is repeated every 42 ms.

Refer to Figure 2 on page 12 for an illustration of the serial LED shift sequence, Table 3 for LED status Type, and Table 4 for LED mode matrix.

Figure 3: External Circuit for Serial LED Mode

| Table 3:  | LED Status | Types |

|-----------|------------|-------|

| 1 abic 0. |            | 19000 |

| Name        | Description                                                                                                                                                                                                 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOAD        | Bandwidth utilization meter. 8-bit value indicating the percentage of total bandwidth of the switch utilized over a 42 ms interval for packet data.                                                         |

| LNK/ACT     | Link and Activity status indicator. Low when link is established. Blinking at 12 Hz when link is up and port is transmitting and receiving.                                                                 |

| LNK/ACT/SPD | Link, Activity and Speed indicator. Active when link is up. Blinking at 3 Hz when port is transmitting or receiving in 10 MB mode. Blinking at 12 Hz when port is transmitting or receiving in 100 MB mode. |

| LNK         | Link status indicator. Low when link is established.High when link is off.                                                                                                                                  |

| DUPLEX      | Duplex mode indicator. High for half-duplex or no link, and low for full-duplex and link.                                                                                                                   |

| SPEED       | Speed indicator. High for 10 Mbps or no link, and low for 100 Mbps and link                                                                                                                                 |

| ACT         | Activity. Low for 42 ms when transmit or receive activity is detected during previous 42 ms interval. High during no activity or no link                                                                    |

| COLSN       | Collision. Low for 42 ms when collision is detected during the previous 42 ms interval. High in the absence of collisions or no link.                                                                       |

| LEDERR#     | Error indication. Internal memory fails self test during power-on reset. Low if failure occurs.                                                                                                             |

Table 4: LED Mode Matrix (Cont.)

| LED Mode [2] | LED Mode [1] | LED Mode [0] | LEDA#       | LEDB#  | LEDC# | Shift Sequence                                                                                                                |

|--------------|--------------|--------------|-------------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------|

| 0            | 0            |              |             | DUPLEX | SPEED | RESVD (1 bit)<br>LEDERR# (1 bit)<br>LOAD# (8 bits)<br>LNK/ACT (8 bits)<br>DUPLEX (8 bits)<br>SPEED (8 bits)                   |

| 0            | o            | )) 1         | LNK/ACT/SPD | DUPLEX | -     | RESVD (1 bit)<br>LEDERR# (1 bit)<br>LOAD# (8 bits)<br>LNK/ACT/SPD (8 bits)<br>DUPLEX (8 bits)                                 |

|              | 7 1          | 0            | LNK         | ACT    | SPEED | RESVD (1 bit)<br>LEDERR# (1 bit)<br>LOAD# (8 bits)<br>LINK (8 bits)<br>ACTIVITY (8 bits)<br>SPEED (8 bits)<br>DUPLEX (8 bits) |

| Table 4: | LED Mode Matrix (Cont.) |  |

|----------|-------------------------|--|

|          |                         |  |

| LED Mode [2] | LED Mode [1] | LED Mode [0] | LEDA#       | LEDB#                             | LEDC#                                | Shift Sequence       |

|--------------|--------------|--------------|-------------|-----------------------------------|--------------------------------------|----------------------|

| 1            | 0            | 0            | LNK/ACT     | DUPLEX                            | SPEED                                | RESVD (1 bit)        |

|              |              |              |             |                                   |                                      | LEDERR# (1 bit)      |

|              |              |              |             |                                   |                                      | LOAD# (8 bits)       |

|              |              |              |             |                                   |                                      | LNK/ACT (& bits)     |

|              |              |              |             |                                   |                                      | DUPLEX (8 bits)      |

|              |              |              |             |                                   |                                      | SPEED (8 bits)       |

|              |              |              |             |                                   |                                      | CQLSN (8 bits)       |

| 1            | 0            | 1            | LNK/ACT/SPD | DUPLEX                            | COLSN                                | RESVD (1 bit)        |

|              |              |              |             |                                   | $\sim$                               | LEQERR# (1 bit)      |

|              |              |              |             |                                   | $\sim$                               | LOAD# (8 bits)       |

|              |              |              |             |                                   |                                      | LNK/ACT/SPD (8 bits) |

|              |              |              |             |                                   | $\langle \checkmark \rangle \rangle$ | DUPLEX (8 bits)      |

|              |              |              |             |                                   |                                      | COLSN (8 bits)       |

| 1            | 1            | 0            | LNK         | ACT                               | S₽∉EĎ                                | RESVD (1 bit)        |

|              |              |              |             |                                   | $\searrow$                           | LEDERR# (1 bit)      |

|              |              |              |             | $\langle \langle \rangle \rangle$ |                                      | LOAD# (8 bits)       |

|              |              |              | ~           |                                   |                                      | DUPLEX (8 bits)      |

|              |              |              |             | $\rightarrow$                     |                                      | COLLISION (8 bits)   |

### LOAD METER LED

The load meter LEDs provide a bar-graph indication of the percentage of total available bandwidth of the switch utilized by packet data over a periodic interval of 42 ms. The bar-graph scale is shown in Table 5 on page 15. The load meter is valid in both single and expanded systems.

Table 5: Load Meter LED Decode

| Load Value Load[7:0]# | Bandwidth (%)       |

|-----------------------|---------------------|

| THUTT                 | <0.4 (all LEDs off) |

| 11)1110               | less than 0.8       |

| 1/111100              | less than 1.6       |

| 11111000              | less than 3.2       |

|                       | less than 6.4       |

| 11100000              | less than 12.8      |

| 11000000              | less than 25        |

| 1000000               | less than 50        |

| 0000000               | >50 (all LED's on)  |

#### CONFIGURATION

Configuration of the AC508 takes place during reset by loading internal control values from pins on the device. All of the pins used for initialization are also used as functional pins during normal operation. These pins are configured to default settings with internal pullup or pulldown resistors and must be configured with external pullup or pulldown resistors to change the default value. The value at the pin is loaded when the reset sequence completes and the pin transitions to normal operation.

# Section 2: Hardware Signal Definitions

| Signal Name                                    | Туре                                                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEDIA CONNECTIO                                | NS                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RD[1:8]±                                       | I                                                                          | Receive Pair. Differential data from the media is received on the RD+ signal pair.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TD[1:8]±                                       | 0                                                                          | <b>Transmit Pair.</b> Differential data is transmitted to the media on the $TD\pm$ signal pair.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CLOCK/RESET                                    |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XTALI/CK25<br>XTALO                            | I<br>0                                                                     | 25 MHz Crystal/Clock Input.<br>For a single-ended clock signal input, connect a 25,000 (+/- 50 ppm) MHz reference<br>clock to the CK25 pin. This pin must be driven with a continuous clock. Leave XTALO<br>unconnected for this mode of operation<br>Alternatively, a 25.000 MHz parallel resonant crystal can be connected between the<br>XTALI/XTALO pins, with a 27 pF capacitor from each pin to GND. Note that this mode<br>should only be used in a non-expanded system, as all clocks in a multi-chip system<br>require the same source clock. |

| RST#                                           | 1                                                                          | Reset. Active Low. Resets the AC508.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MII/7-WIRE PORT                                |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| тхс                                            | I/O <sub>PD</sub>                                                          | <b>Transmit Clock.</b> For MI mode, 25 MHz input in 100BASE-X mode and 2.5 MHz in 10BASE-T mode. This clock must be a continuously driven input, generated from the PHY. This signal becomes the TXC output for 7-wire.                                                                                                                                                                                                                                                                                                                                |

| TXD[3:0]                                       | I/O <sub>PD</sub>                                                          | <b>Transmit Data Output.</b> Nibble-wide transmit data is output on these pins synchronously to TXC. TXD[3] is the most significant bit. TXD[0] is referenced as TXD during 7 wire mode.                                                                                                                                                                                                                                                                                                                                                               |

| TXEN                                           | I/Opp                                                                      | <b>Transmit Enable.</b> Indicates that the data nibble is valid on TXD[3:0]. TXEN for 7-wire.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TXER                                           | HOPO                                                                       | <b>Transmit Error.</b> Asserted while TXEN is active to force a bad code into the transmit data stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RXC                                            | DOPD                                                                       | <b>Receive Clock.</b> 25 MHz input in 100BASE-X mode and 2.5 MHz input in 10BASE-T mode. RXC is expected to be continuously running. RXC may have an irregular period when RXDV= 0 at the beginning of a packet. RXC for 7-wire.                                                                                                                                                                                                                                                                                                                       |

| RXD[3]<br>RXD[2]<br>RXD[1]<br>RXD[1]<br>RXD[0] | I <sub>PD</sub><br>I <sub>PD</sub><br>I <sub>PD</sub><br>I/O <sub>PD</sub> | <b>Receive Data Inputs.</b> Nibble-wide receive data. RXD[3] is the most significant bit. RXD[0] is referenced as RXD during 7-wire mode.                                                                                                                                                                                                                                                                                                                                                                                                              |

| RXDV                                           | I/O <sub>PD</sub>                                                          | <b>Receive Data Valid.</b> Active high. Indicates that a receive frame is in progress, and that the data stream present on the RXD input pins is valid. RXDV for 7-wire.                                                                                                                                                                                                                                                                                                                                                                               |

|                                                |                                                                            | input; O = output; I/O = bidirectional; I <sub>PU</sub> = input w/ internal pull-up; O <sub>OD</sub> = open-drain<br>output; B = Bias; PWR = power supply; GND = ground                                                                                                                                                                                                                                                                                                                                                                                |

#### Table 6: Signal Descriptions

| Table 6: | Signal | Descriptions | (Cont.) |

|----------|--------|--------------|---------|

|----------|--------|--------------|---------|

| Signal Name                            | Туре              | Description                                                                                                                                                                                                                                                             |  |  |  |

|----------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RXER                                   | I <sub>PD</sub>   | <b>Receive Error Detected.</b> Active high. Indicates that there has been an error during a receive frame.                                                                                                                                                              |  |  |  |

| CRS                                    | I <sub>PD</sub>   | Carrier Sense. Active high. Indicates traffic on link.                                                                                                                                                                                                                  |  |  |  |

| COL                                    | I/O <sub>PD</sub> | <b>Collision Detect.</b> In half-duplex mode, active high input indicates that a collision has occurred. In full-duplex mode, COL remains low. COL is an asynchronous input signal. In 7-wire mode, acts as output signal COL.                                          |  |  |  |

| MDIO                                   | I/O <sub>PD</sub> | <b>Management Data I/O.</b> This serial input/output bit is used to read from and write to the MII registers of the internal transceivers. The data value on the MDIO pin is valid and latched on the rising edge of MDC.                                               |  |  |  |

| MDC                                    | I/O <sub>PD</sub> | Management Data Clock. MDC must be provided to the AC508 as an input to allow MII management functions. Clock frequencies up to 12.5 MHz are supported. If the AC508 detects SCK activity on the SMP, the AC508 will source a 2.5 MHz clock to the external PHY device. |  |  |  |

| LINK#                                  | I <sub>PU</sub>   | Link Status Indicator. Active low indication of the link status of the transceiver connected at the MII port. When low, the fink pass condition is indicated.                                                                                                           |  |  |  |

| BIAS                                   |                   |                                                                                                                                                                                                                                                                         |  |  |  |

| RDAC                                   | В                 | <b>DAC Bias Resistor.</b> Adjusts the drive level of the transmit DAC. A 1% precision resistor must be connected between the RDAC pin and GND. See Table 16 on page 31 for the required value.                                                                          |  |  |  |

| LEDS                                   |                   |                                                                                                                                                                                                                                                                         |  |  |  |

| LED[1:9]A#<br>LED[1:9]B#<br>LED[1:9]C# | 0                 | <b>Per Port LED Indicators.</b> Refer to Table 3 on page 14 and Table 4 on page 14 for a functional description of these signals.                                                                                                                                       |  |  |  |

| LEDCLK                                 | 0                 | LED Shift Clock. Periodically active to enable the shift of LEDDATA into external registers.<br>Shared with LEDMODE0.                                                                                                                                                   |  |  |  |

| LEDDATA                                |                   | LED Data Output. Serial LED data is shifted out when LEDCLK is active. Refer to Table 3 on page 14 and Table 4 on page 14 for a functional description of these signals. Shared with LEDMODE1.                                                                          |  |  |  |

|                                        | $\supset$         |                                                                                                                                                                                                                                                                         |  |  |  |

| CONFIGURATION                          |                   |                                                                                                                                                                                                                                                                         |  |  |  |

| ENFDXFLOW                              | I <sub>PU</sub>   | <b>Enable Automatic Full Duplex Flow Control.</b> In combination with the results of Auto-<br>Negotiation, sets the flow control mode. Refer to Table 1 on page 5 for more information.                                                                                 |  |  |  |

| $\langle \rangle \rangle$              |                   | Enable Automatic Backpressure.                                                                                                                                                                                                                                          |  |  |  |

| ENHOXFLOW                              | I <sub>PU</sub>   | ENHDXFLOW =0: Half-duplex flow control is disabled.<br>ENHDXFLOW =1: Half-duplex flow control is enabled.                                                                                                                                                               |  |  |  |

|                                        |                   | Refer to Table 1 on page 5 for more information.                                                                                                                                                                                                                        |  |  |  |

|                                        |                   | input; $O = output$ ; $I/O = bidirectional$ ; $I_{PU} = input w/internal pull-up$ ; $O_{OD} = open-drain output$ ; $B = Bias$ ; $PWR = power supply$ ; $GND = ground$                                                                                                   |  |  |  |

| Table 6: | Signal Descriptions | (Cont.) |

|----------|---------------------|---------|

|----------|---------------------|---------|

| Signal Name                              | Туре                                                    | Description                                                                                                                                                                                                                                                             |

|------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LEDMODE[2],<br>LEDMODE[1],<br>LEDMODE[0] | I <sub>PU,</sub><br>I <sub>PD,</sub><br>I <sub>PD</sub> | LED Mode.<br>LEDMODE0 shared with LEDCLK. LEDMODE1 shared with LEDDATA. LEDMODE2<br>shared with ERDYO.<br>See Table 5 on page 15 for details.                                                                                                                           |

| MDIX_DIS                                 | I <sub>PD</sub>                                         | HP Auto-MDIX Disable.<br>MDIX_DIS = 0: Automatic TX cable swap detection enabled.<br>MDIX_DIS = 1: Automatic TX cable swap detection disabled.                                                                                                                          |

| MII_FDX#                                 | I <sub>PD</sub>                                         | MII Duplex operation.         Sets the duplex setting of the MII port. Can be overridden by software through the MII Port State Override Register.         MII_FDX# = 1: MII port operates in half-duplex.         MII_FDX# = 0: MII port operates in full-duplex.      |

| MII_SPD100#                              | I <sub>PD</sub>                                         | MII default Speed operation.         Sets the speed setting of the MII port. Can be overridden by software through the MII Port State Override Register.         MII_SPD100# = 0: MII port operates at 100 Mb/s.         MII_SPD100# = 1: MII port operates at 10 Mb/s. |

| MII_FLOWCTRL                             | I <sub>PD</sub>                                         | MII Link Partner Flow Control capability.         MII_FLOWCTRL = 0: MII port partner does not support 802.3x flow control in full duplex mode.         MII_FLOWCTRL € 1: MII port partner supports 802.3x flow control in full duplex mode.                             |

| MII_7WIRE_SEL                            | I <sub>PU</sub>                                         | MII or 7WIRE Interface Selection.<br>MII_7WIRE SEL = 0: Configures MII pins to connect to 7 Wire CPU.<br>MII_7WIRE SEL = 1: Configures MII pins to support connection to an external MII<br>device.<br>Shared with TXD2.                                                |

| POWER                                    | ((                                                      |                                                                                                                                                                                                                                                                         |

| VDDC                                     | PWR                                                     | 1,8V Digital Core VDD.                                                                                                                                                                                                                                                  |

| GNDC                                     | GND                                                     | Digital Core GND.                                                                                                                                                                                                                                                       |

|                                          |                                                         | input; $O = output$ ; $I/O = bidirectional$ ; $I_{PU} = input w/internal pull-up$ ; $O_{OD} = open-drain output$ ; $B = Bias$ ; $PWR = power supply$ ; $GND = ground$                                                                                                   |

| Signal Name | Туре | Description                                 |

|-------------|------|---------------------------------------------|