# TMC332 – DATA SHEET

Micro step sequencer with integrated PWM units for 2-phase and 3-phase motors with closed loop current regulator

TRINAMIC<sup>®</sup> Motion Control GmbH & Co. KG Sternstraße 67 D – 20357 Hamburg GERMANY

## 1 Features

The TMC332 is a high resolution micro step sequencer with integrated sine wave look-up table and integrated PWM units. The TMC332 can control both, 2-phase stepper motors and 3-phase stepper motors. The TMC332 has two alternative step direction interfaces - a classical two wire step/direction interface and a SPI step direction interface for the TMC428 driver chain. An Internal micro step counter with programmable step width makes the handling of physical units comfortable. Parameterizing the TMC428 and the TMC332 takes place over a common SPI micro controller interface.

- micro step sequencer for smooth motion applications

- 2-phase stepper motor control

- 3-phase stepper motor control

- 9 bit PWM units

- 9 bit sine wave look-up table

- 8 bit PWM scaler

- 4 bit PWM sub-modulation for scaling quantization compensation

- · programmable break-before-make timing

- classical two wire step direction interface

- driver chain step direction interface for TMC428

- common SPI interface for parameterizing of TMC332 and TMC428

- Integrated Current Measurement ADC (just two TLC374, one LM324 and some RC required)

- Integrated Current Regulation

- · Manual or automatic micro-/full step switching for higher speeds

- 16 MHz clock frequency

- operation with 3.3V compatible IOs / 1.5V core voltage

- available in FBGA144 package

## Life support policy

TRINAMIC Motion Control GmbH & Co. KG does not authorize or warrant any of its products for use in life support systems, without the specific written consent of TRINAMIC Motion Control GmbH & Co. KG.

Life support systems are equipment intended to support or sustain life, and whose failure to perform, when properly used in accordance with instructions provided, can be reasonably expected to result in personal injury or death.

## © TRINAMIC Motion Control GmbH & Co. KG 2009

Information given in this data sheet is believed to be accurate and reliable. However no responsibility is assumed for the consequences of its use nor for any infringement of patents or other rights of third parties which may result from its use.

Specifications subject to change without notice.

# 2 Table of Contents

| 1 | FEATURES                                                             |    |  |  |  |  |

|---|----------------------------------------------------------------------|----|--|--|--|--|

| 2 | TABLE OF CONTENTS                                                    | 3  |  |  |  |  |

| 3 | TABLE OF FIGURES                                                     | 4  |  |  |  |  |

| 4 | TABLE OF TABLES                                                      | 4  |  |  |  |  |

| 5 |                                                                      |    |  |  |  |  |

| • | 5.1 PACKAGE OUTLINES AND DIMENSIONS                                  | _  |  |  |  |  |

|   | 5.1.1 TMC332-BC - Fine Pitch BGA Package with 144 Balls (FBGA144)    | 7  |  |  |  |  |

| 6 | GENERAL DESCRIPTION                                                  | 8  |  |  |  |  |

|   | 6.1 CHIPSET CONFIGURATION OUTLINES                                   | 9  |  |  |  |  |

| 7 | APPLICATION CIRCUIT NOTES                                            | 10 |  |  |  |  |

|   | 7.1 SPI CHAIN DETAILS                                                | 10 |  |  |  |  |

|   | 7.2 GATE CONTROL OUTPUT POLARITY (PH, PL PINS)                       |    |  |  |  |  |

|   | 7.3 ENCODER INPUT PINS                                               | 10 |  |  |  |  |

|   | 7.4 CURRENT REGULATION PINS                                          | 10 |  |  |  |  |

|   | 7.5 OVER CURRENT PROTECTION                                          |    |  |  |  |  |

|   | 7.6 STANDALONE PINS                                                  |    |  |  |  |  |

|   | 7.6.1 Configuration input description                                |    |  |  |  |  |

|   | 7.7 SCHEMATICS                                                       |    |  |  |  |  |

|   | 7.8 SELECTING THE EXTERNAL COMPONENTS                                |    |  |  |  |  |

| 8 | REGISTER DESCRIPTION                                                 | 15 |  |  |  |  |

|   | 8.1 SPI COMMUNICATION EXAMPLES                                       | 19 |  |  |  |  |

|   | 8.2 FULL INITIALIZATION EXAMPLE                                      | 19 |  |  |  |  |

| 9 | PARAMETERIZING THE TMC332                                            | 20 |  |  |  |  |

|   | 9.1 POSITION COUNTER (ADDRESS \$00 TO \$02)                          | 20 |  |  |  |  |

|   | 9.1.1 Additional notes                                               |    |  |  |  |  |

|   | 9.1.2 Example                                                        |    |  |  |  |  |

|   | 9.2 MICRO STEP WIDTH (ADDRESS \$03 AND \$04)                         | 20 |  |  |  |  |

|   | 9.2.1 Additional notes                                               | 20 |  |  |  |  |

|   | 9.2.2 Examples                                                       |    |  |  |  |  |

|   | 9.3 PWM SETTINGS (ADDRESS \$06 AND \$07)                             |    |  |  |  |  |

|   | 9.3.1 Additional notes                                               |    |  |  |  |  |

|   | 9.3.2 Example                                                        |    |  |  |  |  |

|   | 9.4 ABN ENCODER INTERFACE (ADDRESS \$09, \$0A AND \$10 TO \$12)      |    |  |  |  |  |

|   | 9.4.1 Additional notes                                               |    |  |  |  |  |

|   | 9.4.2 Encoder constant                                               |    |  |  |  |  |

|   | 9.4.4 Encoder compare registers                                      |    |  |  |  |  |

|   | 9.4.5 Examples                                                       |    |  |  |  |  |

|   | 9.5 CURRENT MEASUREMENT AND CURRENT REGULATOR (ADDRESS \$0B TO \$0D) |    |  |  |  |  |

|   | 9.5.1 Additional notes                                               |    |  |  |  |  |

|   | 9.5.2 Example                                                        |    |  |  |  |  |

|   | 9.6 AUTOMATIC MICRO-/FULL STEP SWITCHING (ADDRESS \$0E)              |    |  |  |  |  |

|   | 9.6.1 Additional notes                                               |    |  |  |  |  |

|   | 9.6.2 Example                                                        |    |  |  |  |  |

|   | 9.7 CALCULATION OF ROTATIONAL SPEED                                  |    |  |  |  |  |

|   | 9.7.1 Example for high rotational speeds                             | 26 |  |  |  |  |

|   |                                                                      |    |  |  |  |  |

| 1 | 0 NOTATION OF NUMBER SYSTEMS                                         | 26 |  |  |  |  |

# 3 Table of Figures

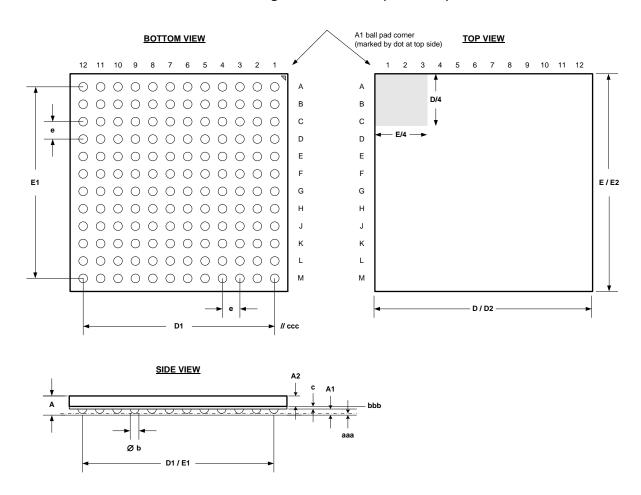

| Figure 1: Package Outline Drawing FBGA144 – (JEDEC MO-192 VAR DAD-1)         |    |

|------------------------------------------------------------------------------|----|

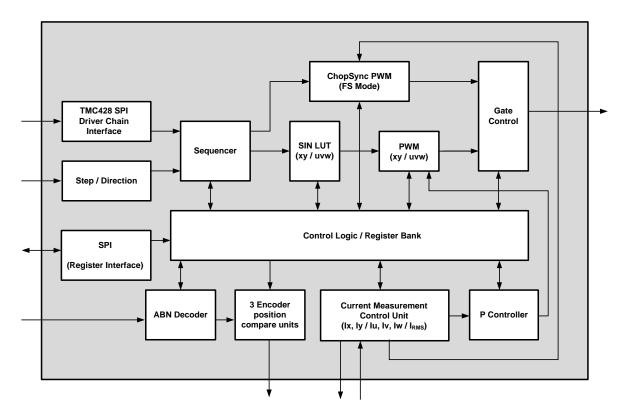

| Figure 2: TMC332 Functional Block Diagram                                    | 8  |

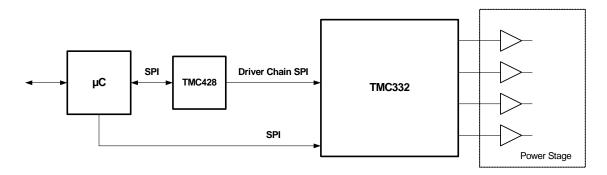

| Figure 3: Outline of a typical TMC332 setup with TMC428 and µC               | 9  |

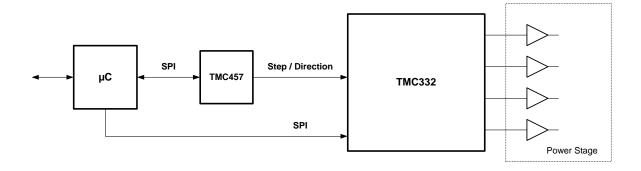

| Figure 4: Outline of a TMC332 Setup with TMC457 and µC                       |    |

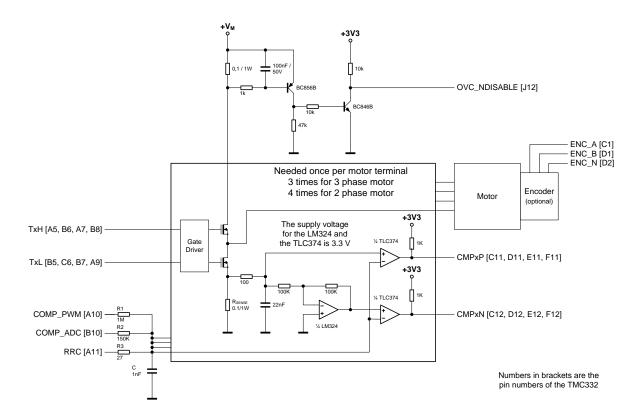

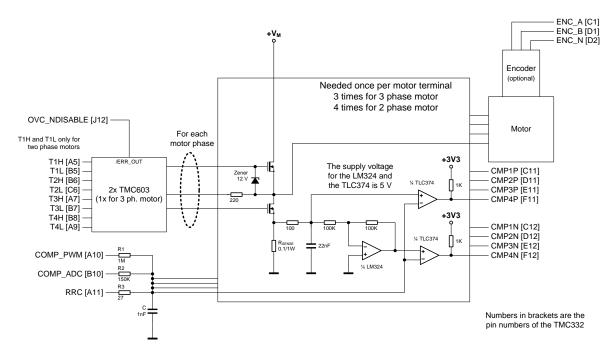

| Figure 5: Schematic with over current detection circuit                      |    |

| Figure 6: Example layout with TMC603                                         |    |

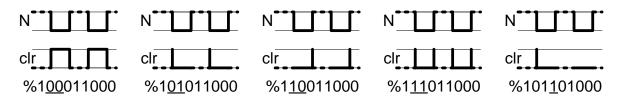

| Figure 7: Effects of the Encoder clear mode bits                             |    |

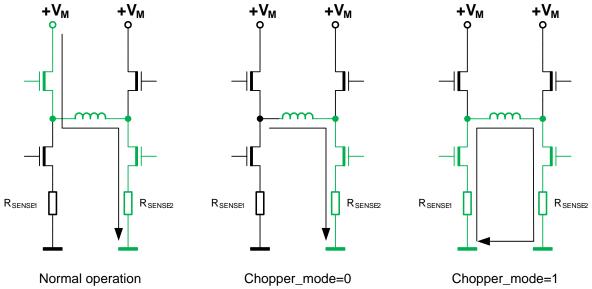

| Figure 8: Full step chopper modes                                            | 25 |

| 4 <u>Table of Tables</u>                                                     |    |

| Table 5-1: TMC332-FG144 Pinning                                              | 6  |

| Table 5-2: Dimensions of FBGA144 (Note: BSC = Basis Spacing Between Centers) | 7  |

| Table 8-1: TMC332 register address mapping (read access)                     |    |

| Table 8-2: TMC332 register address mapping (write access)                    |    |

| Table 8-3: TMC332 functional register description                            |    |

| Table 9-1: Description of the enc. clr. mode bits                            | 22 |

## 5 Pinning

A single package variant (BGA FG144, 0.5mm pitch) is available for the TMC332. For proper operation, it is strongly recommended to connect all power and ground pins (3.3V, 1.5V, GND).

| Pin            | FG144 | I/O | Description                              |                          |                          |                      |

|----------------|-------|-----|------------------------------------------|--------------------------|--------------------------|----------------------|

| NRST           | F1    | ı   | low active reset input                   |                          |                          |                      |

| CLK            | G1    | ı   | clock input                              |                          |                          |                      |

| nEN            | H2    | ı   | low active enable in                     | nput, nEN='1' disables   | all gate control signa   | Is equivalent to OVC |

| nSCS           | М3    | ı   |                                          | select input of the TM   |                          |                      |

| nSCS_428       | L4    | ı   | low active SPI chip                      | select input driven fro  | m μC to select the TN    | //C428               |

| SCK            | M4    | ı   | serial data clock in                     | out driven from µC       | -                        |                      |

| SDI            | M5    | ı   | serial data input dri                    | ven from μC              |                          |                      |

| SDO_OF_428     | L6    | ı   | input driven by the                      | SDO_C of the TMC42       | 28                       |                      |

| SDO            | M6    | O/Z | serial data output nSCS_428)             | to μC (from TMC3         | 332 or TMC428, de        | pending on nSCS /    |

| STP            | J1    | I   | step pulse input ( chain)                | logical ored with inte   | rnal STEP pulse via      | TMC428 SPI driver    |

| DIR            | K1    | I   |                                          | cal ored with internal S |                          |                      |

| nSCS_DRV       | M8    | ı   |                                          | select input driven fro  |                          |                      |

| SCK_DRV        | L8    | ı   |                                          | out driven from TMC42    |                          |                      |

| SDI_DRV        | M7    | ı   | serial data input dri                    | ven from TMC428 (dri     | ven by SDO_S)            |                      |

| SDO_DRV        | L7    | 0   |                                          | TMC428 SDI_S or to       |                          |                      |

| PH             | A4    | ı   |                                          | de, 0 : low active gate  |                          |                      |

| PL             | B4    | ı   |                                          | le, 0 : low active gate  |                          |                      |

| OVC_PH         | K12   | ı   |                                          | rol outputs T1H, T2H,    |                          |                      |

| OVC_PL         | K11   | ı   |                                          | ol outputs T1L, T2L, T   |                          |                      |

| OVC_DISABLE    | J11   | ı   |                                          | put (from comparator of  |                          |                      |

| OVC_NDISABLE   | J12   | ı   |                                          | ut (from comparator o    |                          |                      |

| OVC            | H11   | 0   | over current status                      | (0: no over current c    | ondition / 1 : over curr | rent condition)      |

| SHAFT          | A3    | ı   |                                          | clockwise / counter clo  |                          |                      |

| nXY_UVW        | B3    | ı   | '0' : selects two pha                    | ase stepper scheme       | '1': selects three pha   |                      |

| T1H            | A5    | 0   | T1H_Y2                                   | Y2                       | deactivated (level       | I depending on PL)   |

| T1L            | B5    | 0   | T1L_Y2                                   | 12                       | deactivated (level       | depending on PH)     |

| T2H            | B6    | 0   | T2H_Y1                                   | Y1                       | T3H_W                    | W                    |

| T2L            | C6    | 0   | T2L_Y1                                   | ī I                      | T3L_W                    | VV                   |

| T3H            | A7    | 0   | T3H_X2                                   | X2                       | T2H_V                    | V                    |

| T3L            | B7    | 0   | T3L_X2                                   | ΛZ                       | T2L_V                    | V                    |

| T4H            | B8    | 0   | T4H_X1                                   | X1                       | T1H_U                    | U                    |

| T4L            | A9    | 0   | T4L_X1                                   | Λī                       | T1L_U                    | U                    |

| ENC_A          | C1    | I   |                                          | mental encoder signal    |                          |                      |

| ENC_B          | D1    | ı   |                                          | mental encoder signal    |                          |                      |

| ENC_N          | D2    | I   |                                          | mental encoder signal    | N (a pull up-resistor    | might be required)   |

| ENC_O_1        | M2    | 0   | Encoder compare of                       |                          |                          |                      |

| ENC_O _2       | L3    | 0   | Encoder compare of                       |                          |                          |                      |

| ENC_O _3       | K4    | 0   | Encoder compare of                       |                          |                          |                      |

| RRC            | A11   | 0   | RC control for curre                     |                          |                          |                      |

| COMP_ADC       | B10   | 0   |                                          | ent measurement/limiti   | ing                      |                      |

| COMP_PWM       | A10   | 0   | RC control for curre                     |                          |                          |                      |

| CMP1P          | C11   | ı   |                                          | r input for phase Y2     |                          |                      |

| CMP1N          | C12   | ı   |                                          | or input for phase Y2    |                          |                      |

| CMP2P          | D11   | ı   |                                          | r input for phase W/Y    |                          |                      |

| CMP2N          | D12   | ı   |                                          | or input for phase W/Y   |                          |                      |

| CMP3P          | E11   | ı   |                                          | r input for phase V/X2   |                          |                      |

| CMP3N          | E12   | ı   | Negative comparator input for phase V/X2 |                          |                          |                      |

| CMP4P          | F11   | l   | Positive comparator input for phase U/X1 |                          |                          |                      |

| CMP4N          | F12   | ı   | Negative comparator input for phase U/X1 |                          |                          |                      |

| STDBY          | F3    | !   |                                          | able (power down mo      |                          |                      |

| STANDALONE_EN  | H6    | -   |                                          | mode (settings via SC    |                          |                      |

| SC_FS_CUR_0    | F9    |     |                                          | configuration, Fullstep  |                          |                      |

| SC_FS_CUR_1    | G9    | I   |                                          | configuration, Fullstep  |                          |                      |

| SC_FS_THRS_0   | E8    | I   |                                          | configuration, Fullstep  |                          |                      |

| SC_FS_THRS_1   | F8    |     |                                          | configuration, Fullstep  |                          |                      |

| SC_FS_THRS_2   | G8    |     |                                          | configuration, Fullstep  |                          |                      |

| SC_P_REG_CUR_0 | J9    | I   |                                          | configuration, Current   |                          |                      |

| SC_P_REG_CUR_1 | K9    |     | Standalone mode of                       | configuration, Current   | regulator target, bit 1  |                      |

SC P REG P 0 H7 Standalone mode configuration, Current regulator P parameter, bit 0 SC\_P\_REG\_P\_1 H8 Standalone mode configuration, Current regulator P parameter, bit 1 SC\_PD\_AMOUNT\_0 E2 1 Standalone mode configuration, power down mode, bit 0 SC\_PD\_AMOUNT\_1 E3 Ī Standalone mode configuration, power down mode, bit 1 SC\_PHI\_0 D9 Standalone mode configuration, phi setting (microstepping), bit 0 1 SC\_PHI\_1 D10 Standalone mode configuration, phi setting (microstepping), bit 1 SC\_PWM\_AMPL\_0 J5 1 Standalone mode configuration, pwm amplitude, bit 0 SC\_PWM\_AMPL\_1 J6 Standalone mode configuration, pwm amplitude, bit 1 SC\_PWM\_AMPL\_2 K5 П Standalone mode configuration, pwm amplitude, bit 2 SC\_PWM\_AMPL\_3 K6 Standalone mode configuration, pwm amplitude, bit 3 SC\_SD\_SEL\_0 G11 Standalone mode configuration, slow decay mode setting, bit 0 Standalone mode configuration, slow decay mode setting, bit 1 SC\_SD\_SEL\_1 G12 A8, C4, 1V5 1.5V core supply voltage (all pins have to be connected proper operation) E1, E10, G3, H1, H5, H12, J7 3V3 A2, B12, 3.3V IO supply voltage (all pin have to be connected for proper operation) E4, E6, E7, E9, H10, J3, L2, L5, L10, L11, M10, M11 GND A1, A6, ground (all pins have to be connected for proper operation) A12, B2, B11, F2, F5, F6, F7, F10, G2, G5, G6, G7, K7, K10, L1, M1, M12 reserved B1, B9, not connected, may be used in the future C2, C3, C5, C7, do not connect C8, C9, C10, D3, D4, D5, D6, D7, D8, E5, F4, G4, G10, H3, H4, H9, J2, J4, J8, J10, K2, K3, K8, L9, L12, M9

Table 5-1: TMC332-FG144 Pinning

## 5.1 Package Outlines and Dimensions

## 5.1.1 TMC332-BC - Fine Pitch BGA Package with 144 Balls (FBGA144)

Figure 1: Package Outline Drawing FBGA144 – (JEDEC MO-192 VAR DAD-1)

| Symphol | Dimer | nsions in MILLIMETERS |       | Dimensions in INCHES |     |     |

|---------|-------|-----------------------|-------|----------------------|-----|-----|

| Symbol  | Min   | Тур                   | Max   | Min                  | Тур | Max |

| A       | 1.35  | 1.45                  | 1.55  |                      |     |     |

| A1      | 0.35  | 0.40                  | 0.45  |                      |     |     |

| A2      | 0.65  | 0.70                  | 0.75  |                      |     |     |

| aaa     |       | 0.12                  |       |                      |     |     |

| b       | 0.45  | 0.50                  | 0.55  |                      |     |     |

| bbb     |       | 0.25                  |       |                      |     |     |

| С       | -     | 0.35                  | -     |                      |     |     |

| ccc     |       | 0.35                  |       |                      |     |     |

| D       | 12.80 | 13.00                 | 13.20 |                      |     |     |

| D1      |       | 11.00 BSC             |       |                      |     |     |

| D2      | 12.80 | 13.00                 | 13.20 |                      |     |     |

| E       | 12.80 | 13.00                 | 13.20 |                      |     |     |

| E1      |       | 11.00 BSC             |       |                      |     |     |

| E2      | 12.80 | 13.00                 | 13.20 |                      |     |     |

| е       |       | 1.00                  |       | •                    |     |     |

Table 5-2: Dimensions of FBGA144 (Note: BSC = Basis Spacing Between Centers)

## 6 General Description

The functional block structure of the TMC332 is given by Figure 2. The TMC332 is equipped with two step direction interfaces processed by the micro step sequencer. The micro step width can be programmed in a wide range with a high resolution. Together with the additional 32 bit position counter, one can easily realize stepping within physical units. The TMC428 step direction interface of the TMC332 is directly compatible to the driver chain interface of the TMC428. The other step direction interface is a classical two wire step direction interface. The parameterizing of the TMC332 takes place via a separate four wire serial interface (SPI) for microcontroller access to the internal register (Control Logic / Register Bank). The integrated sine wave look up table (SIN LUT) can output either two sine waves with a phase shift of 90° for two phase stepper motors or three sine waves with +/- 120° phase shift for three phase stepper motors. The gate control block provides the gate control signals for the power stage half bridges, including programmable break-before-make timing and over current protection. PWM frequency and brake-before-make timing are programmable.

Incremental encoders with ABN output can be connected to the TMC332 to evaluate the physical motor position. Three output lines are available to trigger external actions when previously set encoder positions are reached.

The TMC332 also contains a current measurement unit and a current regulator, requiring only a few inexpensive external components.

Figure 2: TMC332 Functional Block Diagram

## 6.1 Chipset Configuration Outlines

Figure 3: Outline of a typical TMC332 setup with TMC428 and  $\mu$ C

Figure 4: Outline of a TMC332 Setup with TMC457 and  $\mu$ C

## 7 Application circuit notes

#### 7.1 SPI chain details

When using the TMC428 to drive the TMC332, the SDO line of the SPI bus, leading to the microcontroller is shared between the TMC332 and the TMC428. Usually the TMC428 requires external logic if the SPI bus has to be shared with other ICs. To avoid another IC, the TMC332 includes logic which switches the SDO signal of the TMC428 through as long as the nSCS428 input is low (active). In all other conditions, the line uses the SDO signal of the TMC332. This means that both chips are connected parallel with distinct chip select lines. That makes it possible to send small datagrams either to the TMC428 or to the TMC332 instead of having to send a large datagram through a daisy chain of both chips.

Since it makes no sense to write the same data to both chips at once, only one chip select line should be active. If both chip select lines are active and data is transferred, both chips will evaluate the data but only the output of the TMC428 will be returned.

If the step/direction input is used, the nSCS\_428 pin should be connected to 3.3V and the SDO\_OF\_428 pin should be connected to GND. When using a TMC428, the STP and DIR pins should be connected to GND.

## 7.2 Gate control output polarity (PH, PL pins)

The PH and PL pins define the polarity of the high- respectively low-side-gates of the bridges. When using non inverting gate drivers and N-MOSFETS on the high side and the low side, both pins would be tied to 3.3V.

If one of the pins sets the wrong polarity, both transistors in the bridge would be switched at once and most probably trigger the over current protection. If both polarities are inverted, the short circuit state would only last as long as the break-before-make delay and if this time is too short to trigger the over current protection, this would lead to a high power consumption in the bridge transistors.

## 7.3 Encoder input pins

If no encoder is used in the application, the encoder input pins ENC\_A, ENC\_B and ENC\_N pins should be connected to either GND or 3.3V.

## 7.4 Current regulation pins

If no current measurement/regulation and no full step mode is needed in the application circuit (when the motor is only operated at low speeds), the external current sensing parts can be omitted. In this case, the comparator inputs (CMPnP and CMPnN, with n=1,2,3,4) should be connected to GND. If full step mode is needed, all inputs should be connected together and should be high, as long as the motor current is too high (The bridges are turned on while no input is high, where CMP1P/N are not evaluated in three phase stepper mode and the phases are evaluated separately in two phase stepper mode).

### 7.5 Over current protection

An external signal, either created by another integrated circuit or by some discrete components can be used to detect over current conditions in the motor power path. The TMC332 provides two complementary inputs, which disable the bridges immediately. This over current condition is not reset automatically but needs a SPI datagram to be sent to the TMC332. The datagram contains the set O (clear over current condition) bit: \$88 00 00 01

Usually only one of the two inputs is used and the other is tied to GND or 3.3V, to disable its function:

| Over current signal active level | OVC_DISABLE | OVC_NDISABLE |

|----------------------------------|-------------|--------------|

| low                              | GND         | signal       |

| high                             | signal      | 3.3V         |

The state of the high and low side outputs during an over current condition is defined by the OVC\_PH and OVC\_PL pins, which work equivalent to the PH and PL pins.

The pin OVC is a representation of the over current flag in the register bank and can be used to trigger an interrupt in a microcontroller.

## 7.6 Standalone pins

When using the standalone mode (external configuration), the **STANDALONE\_EN** pin has to be connected to 3.3V and the SC\_\* inputs have to be connected to 3.3V or GND to set the needed values. The exact function of these pins is explained below.

When using the classic configuration mode via the SPI bus, the **STANDALONE\_EN** pin has to be connected to GND.

In standalone mode, the SC\_\* inputs override some settings in the register bank.

## 7.6.1 Configuration input description

The numbers of the inputs with the same name are the bit numbers, where bit 0 is the LSB. The binary value 0 represents 0V/GND and 1 represents 3.3V.

#### SC PWM AMPL \*

The 4 bit value is used as the upper 4 bits of the 8 bit pwm\_ampl value. The lower 4 bits are set to 1, resulting in 16 possible values from 15 to 255 in steps of 16.

## SC PHI \*

The four possible settings for PHI are:

| The real presents coming the real section of |      |     |                      |  |  |

|----------------------------------------------|------|-----|----------------------|--|--|

| SC_                                          | PHI_ | phi | microstepping with 2 |  |  |

| 1                                            | 0    |     | phase stepper        |  |  |

| 0                                            | 0    | 1   | 256x                 |  |  |

| 0                                            | 1    | 4   | 64x                  |  |  |

| 1                                            | 0    | 16  | 16x                  |  |  |

| 1                                            | 1    | 64  | 4x                   |  |  |

#### SC PD AMOUNT \*

The power down amount bits are the same as the stdby value in the register bank but the reduced power setting is used as long as one of the inputs is set high.

| SC_PD_A | AMOUNT_ | pwm_ampl /               |

|---------|---------|--------------------------|

| 1       | 0       | current regulator target |

| 0       | 0       | * 1                      |

| 0       | 1       | * 0.5                    |

| 1       | 0       | * 0.25                   |

| 1       | 1       | * 0.125                  |

### SC\_P\_REG\_CUR\_\* and SC\_P\_REG\_P\_\*

The current regulator is disabled as long as **SC\_P\_REG\_CUR\_0** and **SC\_P\_REG\_CUR\_1** are both 0. In other cases the current regulator is enabled and the P parameter selected with SC\_P\_REG\_P\_\* is used. The regulator tolerance is set to 12.5%.

| SC_P_RE | EG_CUR_ | current          |

|---------|---------|------------------|

| 1       | 0       | regulator target |

| 0       | 0       | disabled         |

| 0       | 1       | 40               |

| 1       | 0       | 60               |

| 1       | 1       | 80               |

The P parameter is configured via the SC\_P\_REG\_P inputs

| SC_P_REG_P_ |   | P parameter | equivalent setting |

|-------------|---|-------------|--------------------|

| 1           | 0 |             | in register bank   |

| 0           | 0 | 1/512       | \$0008             |

| 0           | 1 | 1/256       | \$0010             |

| 1           | 0 | 1/128       | \$0020             |

| 1           | 1 | 1/64        | \$0040             |

## SC\_FS\_THRS\_\* and SC\_FS\_CUR \_\*

The manual/automatic full step switching is configured with the SC\_FS\_THRS\_\* inputs.

| S | C_FS_THRS | _ | Full step switching (threshold |

|---|-----------|---|--------------------------------|

| 2 | 1         | 0 | equivalent to register bank)   |

| 0 | 0         | 0 | always off                     |

| 0 | 0         | 1 | \$10                           |

| 0 | 1         | 0 | \$20                           |

| 0 | 1         | 1 | \$30                           |

| 1 | 0         | 0 | \$40                           |

| 1 | 0         | 1 | \$80                           |

| 1 | 1         | 0 | \$C0                           |

| 1 | 1         | 1 | always on                      |

Note that in "always on" mode the phi setting from the **SC\_PHI\_\*** inputs is still active, meaning that more than one step pulse (4/16/64/256) is needed to make the motor do one full step.

The SC\_FS\_CUR\_\* inputs configure the current setting in full step mode.

| SC_FS | _CUR_ | Setting equivalent |

|-------|-------|--------------------|

| 1     | 0     | to register bank   |

| 0     | 0     | 2                  |

| 0     | 1     | 4                  |

| 1     | 0     | 6                  |

| 1     | 1     | 8                  |

## SC\_SD\_SEL\_\*

The slow decay configuration inputs have the same functionality as the sl\_d bits in the register bank.

| SC_SD_SEL_ |   |   | Setting equivalent to  |

|------------|---|---|------------------------|

|            | 1 | 0 | register bank          |

| 0          |   | 0 | no slow decay phase    |

| 0          |   | 1 | 50% slow decay phase   |

| 1          |   | 0 | 75% slow decay phase   |

| 1          |   | 1 | 87.5% slow decay phase |

## 7.7 Schematics

Figure 5: Schematic with over current detection circuit

Figure 5 shows the external components of the TMC332 needed to drive a motor with current measurement/control and over current protection. Not shown are the SPI bus to access the register bank and the control hardware (TMC428 SPI or step/direction interface). The over current detection circuit in the  $V_{\rm M}$  line switches at approximately 5A.

Figure 6: Example layout with TMC603

When using the TMC603 as gate driver, the parts for the over current protection can be omitted as the signal is provided by the TMC603. One TMC603 is able to drive 3 half bridges, which is enough for a three phase motor. For a two phase motor, two TMC603 are required, where every TMC603 drives the half bridges of one motor phase. In that case the error outputs of the two TMC603 are both connected to the OVC NDISABLE pin.

## 7.8 Selecting the external components

For different current requirements, the values of the external components can be adapted. The best way is to change the value of the sense resistor.

For good regulation results, the target current value should be around 80 but not higher than 90. With a two phase motor, this equals a charging time of about 10 $\mu$ s for the capacitor C. With the values in the example layouts (R2 = 150k, C = 1nF), this results in a voltage of 0.22V. With an 1A (RMS) motor, a 0.15 Ohm sense resistor would create a 0.21V sense voltage at 1.41A peak phase current.

For three phase motors the charging time should be about 8.125µs, so the voltage is at 0.18V. With a 6A three phase motor, a 0.033 Ohm sense resistor would create 0.198V sense voltage.

The operational amplifiers and the comparators can be different parts than LM324 and TLC374, but care should be taken with the comparators as they should have a low input bias current.

## 8 Register Description

The TMC332 is equipped with a set of registers for parameterizing. An overview of the registers is given in Table 8-2: TMC332 register address mapping and the detailed explanation follows in Table 8-3: TMC332 functional register description.

\$b1 describes the hexadecimal value of the first byte to send to the TMC332. It contains the w bit which describes if data should be read (0) or written (1) followed by the seven address bits %add. If the w bit is 1, the remaining 24 bits of the datagram contain the data that should be written to that address according to the table, if the w bit is 0 for reading data from the TMC332, the value of the remaining bits is not important (don't care).

|      |   |   |        |     | 3      | 2 b | it C   | ΑT   | 32 bit DATAGRAM to send from a μC to the TMC332 via pin SDI |                     |    |             |        |        |        |        | μC     | to t | he   | TM    | C3    | 32    | via   | pin    | SE  | )I   |      |                |     |                                        |      |     |

|------|---|---|--------|-----|--------|-----|--------|------|-------------------------------------------------------------|---------------------|----|-------------|--------|--------|--------|--------|--------|------|------|-------|-------|-------|-------|--------|-----|------|------|----------------|-----|----------------------------------------|------|-----|

|      |   |   |        |     |        |     |        |      |                                                             |                     |    |             |        | rea    | ıd a   | acc    | ess    | •    |      |       |       |       |       |        |     |      |      |                |     |                                        |      |     |

|      | 3 | 3 | 2      | 2   | 2      | 2   | 2 5    | 2 4  | 2                                                           | 2 2                 | 2  | 2           | 1 9    | 1 8    | 1 7    | 1      | 1 5    | 1 4  | 1 3  | 1 2   | 1     | 1 0   | 9     | 8      | 7   | 6    | 5    | 4              | 3   | 2                                      | 1    | 0   |

| \$b1 |   |   |        |     |        | 4   | 3      | data |                                                             |                     |    |             |        |        |        |        |        |      |      |       |       |       |       |        |     |      |      |                |     |                                        |      |     |

| \$00 | 0 | 0 | 0      | 0   | 0      | 0   | 0      | 0    |                                                             |                     |    |             |        |        |        |        |        |      |      | Х     |       |       |       |        |     |      |      |                |     |                                        |      |     |

| \$01 | 0 | 0 | 0      | 0   | 0      | 0   | 0      | 1    |                                                             |                     |    |             |        |        |        |        |        |      |      |       |       |       |       |        |     |      |      | X              | h   |                                        |      |     |

| \$03 | 0 | 0 | 0      | 0   | 0      | 0   | 1      | 1    |                                                             | •                   | •  | •           |        |        |        |        |        |      |      | phi.  | fra   | С     |       |        |     |      |      |                |     |                                        |      |     |

| \$04 | 0 | 0 | 0      | 0   | 0      | 1   | 0      | 0    |                                                             |                     |    |             |        |        |        |        |        |      |      |       |       |       |       |        |     |      | phi  | _int           |     |                                        |      |     |

| \$06 | 0 | 0 | 0      | 0   | 0      | 1   | 1      | 0    |                                                             |                     |    |             |        |        |        |        |        |      |      |       |       |       |       |        |     |      | p۱   | wm_            | _am | pl                                     |      |     |

| \$07 | 0 | 0 | 0      | 0   | 0      | 1   | 1      | 1    |                                                             | pwm pwm bbm_dlyoffs |    |             |        |        |        |        |        |      |      |       |       |       |       |        |     |      |      |                |     |                                        |      |     |

| \$08 | 0 | 0 | 0      | 0   | 1      | 0   | 0      | 0    |                                                             |                     |    |             |        |        |        | stat   | tus    | (h=i | nhik | oit & | 0=    | ovc)  | )     |        |     |      |      |                |     |                                        | h    | 0   |

| \$09 | 0 | 0 | 0      | 0   | 1      | 0   | 0      | 1    |                                                             | enc_count           |    |             |        |        |        |        |        |      |      |       |       |       |       |        |     |      |      |                |     |                                        |      |     |

| \$0A | 0 | 0 | 0      | 0   | 1      | 0   | 1      | 0    |                                                             |                     |    |             |        |        |        |        |        |      |      |       |       |       | n     |        |     |      |      |                |     |                                        |      |     |

| \$0B | 0 | 0 | 0      | 0   | 1      | 0   | 1      | 1    |                                                             |                     |    |             |        | dc4    | )      |        |        |      | i_v/ | 'i_x2 | 2 (a  | dc3)  | )     | ,      |     |      | i_w/ | _              |     |                                        |      |     |

| \$0C | 0 | 0 | 0      | 0   | 1      | 1   | 0      | 0    |                                                             |                     | i_ | <u>y</u> 2( | adc    | 1)     |        |        |        |      |      | Limit | Err_u | Err_v | Err_w | Err_y2 | i_a | abs: |      | t(i_u<br>t(i_> |     | _V <sup>2</sup> +<br>_y <sup>2</sup> ) | i_W² | ) / |

| \$0E | 0 | 0 | 0      | 0   | 1      | 1   | 1      | 0    |                                                             |                     |    |             |        |        |        |        |        |      |      |       |       |       |       |        |     |      |      |                |     |                                        |      | f   |

| \$0F | 0 | 0 | 0      | 0   | 1      | 1   | 1      | 1    |                                                             |                     |    |             | ty     | уре    | (33    | 2)     |        |      |      |       |       |       |       |        | ve  | rsio | n (2 | 00)            |     |                                        |      |     |

| \$10 | 0 | 0 | 0      | 1   | 0      | 0   | 0      | 0    |                                                             |                     |    |             |        |        |        |        |        |      | er   | C_C   | om    | p_1   |       |        |     |      |      |                |     |                                        |      |     |

| \$11 | 0 | 0 | 0      | 1   | 0      | 0   | 0      | 1    |                                                             | enc_comp_2          |    |             |        |        |        |        |        |      |      |       |       |       |       |        |     |      |      |                |     |                                        |      |     |

| \$12 | 0 | 0 | 0      | 1   | 0      | 0   | 1      | 0    |                                                             | enc_comp_3          |    |             |        |        |        |        |        |      |      |       |       |       |       |        |     |      |      |                |     |                                        |      |     |

| \$b1 | w |   |        |     | 6aa    | ld  |        |      |                                                             | data                |    |             |        |        |        |        |        |      |      |       |       |       |       |        |     |      |      |                |     |                                        |      |     |

|      | 3 | 3 | 2<br>9 | 2 8 | 2<br>7 | 2   | 2<br>5 | 2 4  | 2 3                                                         | 2                   | 2  | 2           | 1<br>9 | 1<br>8 | 1<br>7 | 1<br>6 | 1<br>5 | 1 4  | 1 3  | 1 2   | 1     | 1 0   | 9     | 8      | 7   | 6    | 5    | 4              | 3   | 2                                      | 1    | 0   |

Table 8-1: TMC332 register address mapping (read access)

|      | 32 bit DATAGRAM to send from a μC to the TMC332 via pin SDI |   |        |   |        |    |        |   |   |            |     |     |     |        |        |        |        |            |      |           |        |      |     |         |          |            |       |     |     |       |      |                |   |

|------|-------------------------------------------------------------|---|--------|---|--------|----|--------|---|---|------------|-----|-----|-----|--------|--------|--------|--------|------------|------|-----------|--------|------|-----|---------|----------|------------|-------|-----|-----|-------|------|----------------|---|

|      |                                                             |   |        |   |        |    |        |   |   |            | wri | ite | acc | ess    | S      |        |        |            |      |           |        |      |     |         |          |            |       |     |     |       |      |                |   |

|      | 3                                                           | 3 | 2<br>9 | 2 | 2<br>7 | 2  | 2<br>5 | 2 | 2 | 2          | 2   | 2   | 1   | 1<br>8 | 1<br>7 | 1<br>6 | 1<br>5 | 1 4        | 1    |           | 1      | 1    | 1   | 9       | 8        | 7          | 6     | 5   | 4   | 3     | 2    | 1              | 0 |

| \$b1 | w                                                           |   |        | 9 | ∕ao    | ld |        |   |   | data       |     |     |     |        |        |        |        |            |      |           |        |      |     |         |          |            |       |     |     |       |      |                |   |

| \$80 | 1                                                           | 0 | 0      | 0 | 0      | 0  | 0      | 0 |   |            |     |     |     |        |        |        |        |            |      |           | X      | l    |     |         |          |            |       |     |     |       |      |                |   |

| \$81 | 1                                                           | 0 | 0      | 0 | 0      | 0  | 0      | 1 |   |            |     |     |     |        |        |        |        |            |      |           |        |      |     |         |          |            |       |     | >   | (_h   |      |                |   |

| \$82 | 1                                                           | 0 | 0      | 0 | 0      | 0  | 1      | 0 |   |            |     |     |     |        |        |        |        |            | dx   |           |        |      |     |         |          |            |       |     |     |       |      |                |   |

| \$83 | 1                                                           | 0 | 0      | 0 | 0      | 0  | 1      | 1 |   |            |     |     |     |        |        |        |        |            |      | pl        | hi_    | frac | )   |         |          |            |       |     |     |       |      |                |   |

| \$84 | 1                                                           | 0 | 0      | 0 | 0      | 1  | 0      | 0 |   |            |     |     |     |        |        |        |        |            |      |           |        |      |     | phi_int |          |            |       |     |     |       |      |                |   |

| \$85 | 1                                                           | 0 | 0      | 0 | 0      | 1  | 0      | 1 |   |            |     |     |     |        |        |        |        | not in use |      |           |        |      |     |         |          |            |       |     |     |       |      |                |   |

| \$86 | 1                                                           | 0 | 0      | 0 | 0      | 1  | 1      | 0 |   |            | sl  | _d  | sto | lby    |        | m      |        |            | sto  | dby       | y_t    | ime  | ou  | t       |          |            |       | р   | wn  | _ar   | npl  |                |   |

| \$87 | 1                                                           | 0 | 0      | 0 | 0      | 1  | 1      | 1 |   |            |     |     |     |        |        |        |        |            |      | wr<br>off |        |      |     | þ       | wm<br>_f |            |       |     |     |       | bbm  | _dly           | ′ |

| \$88 | 1                                                           | 0 | 0      | 0 | 1      | 0  | 0      | 0 |   |            |     |     | sta | us (   | & co   | ontro  | ol (p  | р=р        | hi_۱ | wr        | & I    | n=ir | hik | oit 8   | , o=     | ovc)       | )     |     |     |       | р    | h              | 0 |

| \$89 | 1                                                           | 0 | 0      | 0 | 1      | 0  | 0      | 1 |   |            |     |     |     |        |        |        |        |            | b    | 1         |        |      | enc | _ac     | CC_C     | ons        | st_in | t   |     |       |      | _acc_<br>t_fra |   |

| \$8A | 1                                                           | 0 | 0      | 0 | 1      | 0  | 1      | 0 |   |            |     |     |     |        |        |        |        |            |      |           |        |      | С   | t       |          |            | е     | nc_ | clr | _mo   | de   |                |   |

| \$8B | 1                                                           | 0 | 0      | 0 | 1      | 0  | 1      | 1 |   |            |     |     |     |        |        |        |        |            |      | no        | t ir   | us   | е   |         |          |            |       |     |     |       |      |                |   |

| \$8C | 1                                                           | 0 | 0      | 0 | 1      | 1  | 0      | 0 |   |            |     |     |     |        |        |        |        |            |      |           |        |      |     |         | r        |            |       |     | ta  | rg_c  | curr |                |   |

| \$8D | 0                                                           | 0 | 0      | 0 | 1      | 1  | 1      | 0 |   |            |     |     |     | tol    | erai   | nce    |        |            |      |           |        |      |     |         |          | <b>p</b> _ | _par  | am  |     |       |      |                |   |

| \$8E | 1                                                           | 0 | 0      | 0 | 1      | 1  | 1      | 0 |   |            |     |     |     | d      | е      | s      |        |            |      |           | F      | S_1  | arg | _cu     | ırr      |            |       |     | FS  | S_thr | •    |                |   |

| \$8F | 1                                                           | 0 | 0      | 0 |        | 1  |        | 1 |   |            |     |     |     |        |        |        |        |            |      | no        | t ir   | us   | е   |         |          |            |       |     |     |       |      |                |   |

| \$90 | 1                                                           | 0 | 0      | 1 | 0      | 0  | 0      | 0 |   |            |     |     |     |        |        |        |        |            | eı   | nc_       | CC     | mp   | _1  |         |          |            |       |     |     |       |      |                |   |

| \$91 | 1                                                           | 0 | 0      | 1 | 0      | 0  | 0      | 1 |   | enc_comp_2 |     |     |     |        |        |        |        |            |      |           |        |      |     |         |          |            |       |     |     |       |      |                |   |

| \$92 | 1                                                           | 0 | 0      | 1 | 0      | 0  | 1      | 0 |   |            |     |     |     |        |        |        |        |            | eı   | nc_       | _cc    | mp   | )_3 |         |          |            |       |     |     |       |      |                |   |

| \$b1 | w                                                           |   |        | 9 | 6aa    | ld |        |   |   |            |     |     |     |        |        |        |        |            |      |           | da     | ta   |     |         |          |            |       |     |     |       |      |                |   |

|      | 3                                                           | 3 | 2      | 2 | 2 7    | 2  | 2 5    | 2 | 2 | 2          | 2   | 2   | 1 9 | 1 8    | 1<br>7 | 1      | 1 5    | 1 4        | 1    |           | 1<br>2 | 1    | 1   | 9       | 8        | 7          | 6     | 5   | 4   | 3     | 2    | 1              | 0 |

Table 8-2: TMC332 register address mapping (write access)

The x I and x h registers together form a 32 bit wide position counter.

The register dx holds the step width for the position counter.

For each micro step, a 34 bit wide register accumulates the micro step position by an amount of phi where phi is composed by an integer part phi\_int and a fractional part phi\_frac. With this, one can realize non-integer micro stepping. The most significant 10 bits of the micro step position register form the micro step pointer within the sine wave look-up table.

The register pwm\_ampl controls the scaling of the PWM. An additional control bit named 'm' is for selection of a PWM modulation that gives a higher resolution at low values of pwm\_ampl.

The pwm\_f register controls the PWM frequency and the bbm\_dly controls the brake-before-make timing.

The status and control register bits named 'p', 'h' are for enabling of the micro step counters to keep them consistent under every condition. The status bit 'o' indicates an over current condition.

The version of the TMC332 can be read out via a dedicated register.

| addr | r/w | register                          | bit(s)                 | functional description                                                                                                                                                                              |

|------|-----|-----------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$00 | r   | Position low                      | x_l                    | read lower 24 bits of 32 bit physical position counter X, 1st read x_l followed by read x_h to get a consistent 32 bit position                                                                     |

|      | W   |                                   |                        | set lower 24 bits of 32 bit physical position counter X                                                                                                                                             |

| \$01 | r   | Position high                     | x_h                    | read higher 8 bits of 32 bit physical position counter X, 1st read x_l before you read x_h to get a consistent 32 bit position                                                                      |

|      | W   |                                   |                        | set higher 8 bits of 32 bit physical position counter X                                                                                                                                             |

| \$02 | W   | Position step width               | Dx                     | write the dx register, the value dx is added or substracted with each step according to the direction input                                                                                         |

| \$03 | r/w | micro step width, fractional part | phi_frac               | 24 bit wide fractional part of the of the micro step width                                                                                                                                          |

| \$04 | r/w | Micro step width, integer part    | phi_int                | 10 bit wide integer part of the micro step width                                                                                                                                                    |

| \$06 | r   | pwm amplitude                     | pwm_ampl               | read PWM amplitude                                                                                                                                                                                  |

|      | W   |                                   | m                      | enable PWM sub-modulation                                                                                                                                                                           |

|      |     |                                   | sl_d                   | slow decay between PWM polarity changes sl_d = %00 : no slow decay phase sl_d = %01 : t*1/2 slow decay phase sl_d = %10 : t*3/4 slow decay phase                                                    |

|      |     |                                   | . (.1)                 | sl_d = %11 : t*7/8 slow decay phase                                                                                                                                                                 |

|      |     |                                   | stdby                  | pwm amplitude/current during power down mode<br>stdby = %00 : 100% of normal value<br>stdby = %01 : 50% of normal value<br>stdby = %10 : 25% of normal value<br>stdby = %11 : 12.5% of normal value |

|      |     |                                   | stdby_timeout          | Delay between last full step and power down activation: delay [s] = (stdby_timeout * 1048576) / f_clk[Hz]                                                                                           |

|      |     |                                   | pwm_ampl               | set PWM amplitude pwm_ampl is used as the upper limit if the current regulator is active                                                                                                            |

| \$07 | r/w | pwm control                       | pwm_offs               | PWM offset; adds an offset to the PWM values to create steeper zero crossings of the current wave                                                                                                   |

|      |     |                                   | pwm_f                  | PWM frequency [Hz] = $f_{clk}[Hz] / ((pwm_f+1)*2^{10})$                                                                                                                                             |

|      |     |                                   | bbm_dly                | break before make delay time [s] = 2^( bbm_dly+1) / f_clk[Hz]                                                                                                                                       |

| \$08 | r/w | status & control                  | р                      | phi register write bit (change of phi)                                                                                                                                                              |

|      |     |                                   |                        | p = 0 : leave phi untouched                                                                                                                                                                         |

|      |     |                                   |                        | p = 1 : update phi := phi_int & phi_frac<br>(write only bit, read always '0')                                                                                                                       |

|      |     |                                   | h                      | inhibit step direction interfaces (no count x_h, x_l, phi_int,                                                                                                                                      |

|      |     |                                   |                        | phi_frac) h = 1 : inhibit STP / DIR (and TMC428_DRV interface) h = 0 : enable STP / DIR (and TMC428_DRV interface)                                                                                  |

|      |     |                                   | 0                      | over current status bit o = 1 : over current condition (read) / reset OVC (write) o = 0 : no over current condition                                                                                 |

| \$09 | r   | encoder counter                   | enc_count              | 24 bit wide encoder counter                                                                                                                                                                         |

|      | W   | encoder step width                | b                      | Interpret fractional part normally (enc_acc_const_frac/16) when 0 or decimal (enc_acc_const_frac/10) when 1                                                                                         |

|      |     |                                   | enc_acc_<br>const_int  | 9 bit wide integer part of the encoder constant                                                                                                                                                     |

|      |     |                                   | enc_acc_<br>const_frac | 4 bit wide fractional part of the encoder constant                                                                                                                                                  |

| \$0A | r   | encoder status                    | n                      | Encoder is cleared at the next clear condition                                                                                                                                                      |

|      | W   | encoder control                   | С                      | Manual reset of enc_count                                                                                                                                                                           |

|      |     |                                   | t                      | Trigger reset of enc_count via bit 5 of cm                                                                                                                                                          |

|                     | 1   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              | Clear made (and 0.4.2 Emander Clear Made)                       |

|---------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------|

| <b>#</b> 0 <b>D</b> |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | enc_clr_mode |                                                                 |

| \$0B                | r   | current register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | i_u          | measured current of terminal U or X1                            |

|                     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | i_v          | measured current of terminal V or X2                            |

| 400                 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | i_W          | measured current of terminal W or Y1                            |

| \$0C                | r   | current register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | i_y2         | Measured current of terminal Y2                                 |