#### 新特器件应用

# 大容量数字交换芯片 MT90820 及其应用

西安邮电学院 刘钊远

摘要: M T 90820 芯片是 M I T E L 公司最新推出的大容量数字交换器件,当串行数据码流速率为 8.192 Mb/s 时,单片可实现  $2048 \times 2048$  通道的无阻塞交换。利用该器件的组合可构成更大容量的交换网络或交叉连接矩阵。本文简要介绍了该器件的主要功能及典型应用。

关键词:帧 交换网络 数字交叉连接 ST-BUS/GCI接口

# 1. 引言

随着通信事业的发展,交换机最初按照交换网络的原理,采用一系列存储器及控制集成电路所构成的交换网络系统存在的生产成本高、调试困难、稳定性差等问题变得突出起来。专用交换网络芯片的出现克服了这些缺点。MITEL 公司最新推出的大容量数据交换芯片 MT90820 具有以下特点:

8. 192Mb/s时可实现 2048 ×2048 通道无阻塞交换:

各通道采用可变或恒定延时,芯片能够自动识别 ST - BUS/ GCI 接口;

接受 ST - BUS 码流 2.048Mb/s,4.096Mb/s 或是 8.192Mb/s 的速率:

自动帧偏移延时测量,可对每帧延时偏移编程;

每通道高阻输出可控,可工作于信息方式,连接存储器可进行块编程;

控制接口与 Motorola 及非复用的 CPU 系列兼容、提供 IEEE - 1149.1(J TAG)测试端口。

# 2. 功能描述

#### 2.1 芯片管脚描述

该芯片采用 PLCC 84 脚封装,管脚说明如表 1 所列。

# 2.2 功能简述

(1)数据和连接存储器

输入的串行码流经串并变换后按顺序写入数据 存储器,连接存储器由 CPU 控制写入。

(2)连接与信息模式

连接方式时,连接存储器中的数据是输出数据 存储器的地址。

信息方式时,微处理器将数据写至连接存储器的相应输出码流和通道单元,低 8 位连接存储器的内容直接通过串并变换输出。

设置高阻态,单通道可被置成高阻态,整条 ST-BUS通过对控制寄存器OSB置位也可被置成 高阻态。

#### (3) 串行数据接口时序

主时钟频率必须二倍于数据速率,WFPS 位为低电平,MT90820 工作于 ST - BUS/GCI 方式,MT90820 能够自动识别 ST - BUS 或 GCI 方式;WFPS 位为高电平时,MT90820 工作于宽帧脉冲(WFP)帧同步方式。

# 2.3 交换配置

M T90820 的串口数据速率与变换矩阵容量的 交换配置如表 2 所列。

(1)输入帧偏移选择

串行线长度不同可导致延时不同,利用该特点 可以进行有效的延时补偿。

现数据的准确传输。本文介绍的 LM 1893 就是一种能实现可靠数据传输的电力线 MODEM 芯片。若用于电度表自动抄表系统、办公楼内部通信、防盗防火报警等系统,可获得很高的性价比。

如对以上器件感兴趣,请与美国国家半导体有限公司北京办事处联系。

电话:010 - 68042453/7 传真:010 - 68042458

咨询编号:980102

表 1 MT90820 管脚说明

| <b>管脚</b>   | 名称        | 功能描述                                                                                                                               |

|-------------|-----------|------------------------------------------------------------------------------------------------------------------------------------|

| 1 ,11 ,30 , | $V_{SS}$  | <br>  地                                                                                                                            |

| 54 ,64 ,75  |           |                                                                                                                                    |

| 2 ,32 ,63   | $V_{DD}$  | 5V 电源                                                                                                                              |

| 3 ~ 10      | STo 8~15  | 程值 ,这些码流以 2.048、4.096 或 8.192Mb/ s 的不同速度输出                                                                                         |

| 12 ~ 27     | STi 0~15  | ST - BUS 输入 0 至 15 :串行输入码流。依据 IMS 寄存器中 DR0 ~ 1 位的不同编程值 ,这些码流以 2.048、4.096 或 8.192 Mb/s 不同速度输出                                      |

| 28          | FOI       | 帧脉冲输入:当 WFPS 管脚为低时,该输入按照 ST - BUS 或 GCI 的特性接受、自动识别帧同步信号;当 WFPS 为高时,该管脚接受 WFPS 格式的负帧脉冲                                              |

| 29          | FE/ HCL K | 帧估值HCL K时钟输入:当 WFPS 为低时,该管脚是帧测试输入端;当 WFPS 为高时,HCL K(4.096Mb/s时钟)是宽脉冲(WFP)模式所必须的                                                    |

| 31          | CL K      | 时钟输入:是串行码流输入/输出时钟。依据 IMS 寄存器中 DR0~1 的不同编程值,该输入接受4.096、8.192 或 16.384 Mb/s 的时钟                                                      |

| 33          | TMS       | 测试模式选择输入:JTAG信号控制 TAP控制器的状态转换。不用时,该脚由内部上拉为高                                                                                        |

| 34          | TDI       | <u>测试串行数据输入:JTAG串行测试指令和数据由该管脚输入。不用时,该脚由内部上拉为高</u>                                                                                  |

| 35          | TDO       | 测试串行数据输出 :在 TCK的下降沿该管脚串行输出数据。当 J TA G 未被使用时该管脚保持高                                                                                  |

| 36          | TCK       | 测试时钟输入:提供JTAG测试逻辑时钟。不用时,该脚由内部上拉为高                                                                                                  |

| 37          | TRST      | 测试复位输入:通过设置测试逻辑复位状态,异步初始化JTAGTAG控制器。不用时,该脚由内<br>  部上拉为高、加电时,该管脚应该输出低脉冲或保持低,以保证 MT90820 正常工作                                        |

| 38          | IC        | 内部连接输入:通常接地。不用时.该脚由内部下拉为低                                                                                                          |

| 39          | RESET     | 设备复位(施密特触发输入):输入为低时,使 MT90820 复位,清除内部计数器、寄存器,它使<br>Sto0~15 及微处理机数据输出高阻态。通常复位时.该管脚至少保持 100ns 的低电平                                   |

| 40          | WFPS      | 宽帧脉冲选择输入:为1使设备工作于宽帧脉冲(WFP)帧同步接口;为0使设备工作于ST-BUS/GCI模式                                                                               |

| 41 ~ 48     | A0 ~ A7   | 地址 0~7 输入:当 CPU 总线工作与非复用方式时,这些线提供 A0~A7 地址线                                                                                        |

| 49          | DS/ RD    | 数据选通/读输入信号:在选通复用方式时,该管脚为高、CS为低才允许读写操作;在复用 <u>方</u> 式而<br>该管脚是读信号时(Intel),该管脚为低允许读操作;在 Motorola 非复用方式时,该管脚与CS为低<br>则允许读写操作          |

| 50          | R/ W/ WR  | 读或写输入信号:在 Motorola <u>复</u> 用与非复用方式时,它是读写信号,控制微处理机访问数据的方向:在 Intel 复用方式时,它是WR信号,控制数据的写入                                             |

| 51          | CS        | 片选输入信号:低时微处理机选中该片                                                                                                                  |

| 52          | AS/ ALE   | 地址选通或地址锁存输入:经过 IM 输入管脚选择操作复用方式。Motorola 非复用方式时该管脚为低。不用该管脚时,它由内部下拉为低                                                                |

| 53          | IM        | CPU 接口方式输入: IM 为高, CPU 端口是复用方式; IM 为低, CPU 端口为非复用方式。不用该管脚时, IM 由内部下拉为低                                                             |

| 55 ~ 62     | AD0 ~ AD7 | 地址/数据总线 0~7:CPU 端口的低 8 位数据线,在地址复用方式时,它们还充当 CPU 的低 8 位地址信号                                                                          |

| 65 ~ 72     | D8 ~ D15  | 数据总线 8~15:它们是 CPU 的高 8 位有效数据线                                                                                                      |

| 73          | DTA       | 数据传输应答(开路输出):低有效输出表示数据传输完成,典型应用中接 10k 上拉电阻                                                                                         |

| 74          | CSTo      | 控制输出:输出 2.048、4.096 或 8.192Mb/s 信号时,每帧分别包含 512、1024 或 2048 位。每位的<br>电平由连接存储器的 CSTo 决定,细节参看外部驱动控制                                   |

| 76          | ODE       | 输出驱动使能输入:STo0~15 串行码流输出的使能控制信号,当 ODE 输入为低,同时 IMS 寄存器的 OSB 位也为低时,STo0~15 输出为高阻态;ODE 为高允许 STo0~15 输出。注意,通过连接存储器的通道控制位的控制,各通道仍可被置为高阻态 |

| 77 ~ 84     | STo 0~7   | 数据码流输出 0~7(三态输出):串行数据输出码流。这些码流有可选的 2.048、<br>4.096 或 8.192 Mb/s 速率输出                                                               |

# (2) 串行输入帧校准估值

M T 90820 利用帧估值 (FE) 输入来决定不同数据输入的延时与帧脉冲 Foi 的对应。

(3)存储器块编程

MT90820 可使用户在两帧时间里初始化所有连接存储块。该性能使每一个连接存储器的 Bit11~15 被存储在 IMS 寄存器的 Bit5~9 中。

当控制寄存器的 MBP 位置高电平时,即被设

置为块编程模式。当 IMS 寄存器的块编程使能位 BPE 置高电平时, 块编程数据将被加载到每一个连接存储器的 Bit11~15 位, 其他的连接存储器位 Bit0~10 置为 0。当存储器块编程完成以后,设置复位 BPE 位为 0。

#### (4) 自环控制

每一个连接存储器单元的LPBK位允许ST-BUS输出数据自环返回至内部的ST-BUS输入,用以诊断。当LPBK位置高电平时,相应的ST-BUS输出通道被内部自环连至该通道的输入;当LPBK位为低电平时,不允许自环。在每一个通道的自环操作期间,帧延时偏移寄存器的内容必须设置为0。

#### 2.4 MT90820 的延时

交换信息从输入码流至输出码流会导致一个通过延时。该器件可编程为建立在每一个通道基础上、附带不同的通过延时的时隙交换功能。在语音应用方面,选择可变的通过延时能够确保输入至输出的最小延时;在宽带数据应用方面,选择恒定延时能维持信息帧完整通过交换。

可变延时(V/C Bit = 0)

该模式下的延时仅与输入、输出通道的组合有关,与输入、输出码流无关。MT90820 能够达到的最小延时为3个时隙时间长度(如表3所列)。

恒定延时(V/C Bit = 1)

在该模式下,输入、输出通道号一旦确定,延时也就确定。恒定延时下最小延时为一帧时间(如表 4 所列)。

# 2.5 M T90820 与微处理器的接口

IM = 0,为 Motorola 非复用总线方式;

IM = 1, 为复用总线方式, 又可分为 Motorola

表 2 交换配置

| 串口数据速率 | 主时钟要求(MHz) | 矩阵容量               |

|--------|------------|--------------------|

| 2Mb/s  | 4. 096     | 512 <b>×</b> 512   |

| 4Mb/s  | 8. 192     | 1024 <b>×</b> 1024 |

| 8Mb/ s | 16.384     | 2048 <b>×</b> 2048 |

与 Intel 两种方式。

M T90820 微处理器端口可以访问内部寄存器、连接和数据寄存器。数据存储器和帧基准寄存器只能进行读操作,其他单元都可以进行读写操作。

#### (1)存储器地址映象(如表 5 所列)

CR 和 IMS 寄存器控制着器件的主要功能。上电之后,IMS 寄存器必须立即编程,以完成串行数据接口的时序和交换配置。

(2) 连接存储器控制如表 6 所列。

# 3. MT90820 的应用

#### 3.1 M T90820 组成的交叉矩阵结构

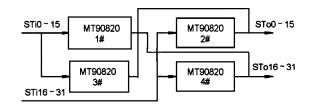

图 1 给出了四片 M T 90820 以 8Mb/s 速率构成的 4096 通道的无阻塞交换矩阵。

# 3.2 8 位处理机与 M T90820 的接口处理

MT90820 是 16 位数据总线,当 CPU 为 8 位数据总线时,为达到 CPU 能对 MT90820 操作的目的,必须进行 8 位与 16 位数据的转换,可按下述方法进行操作处理。

写操作时, 先把高 8 位数据写进一个寄存器地址,写低 8 位数据时同时打开高 8 位数据寄存器,这样 16 位数据就能一次写进 M T90820;读操作时,由相应地址一次读取 16 位数据,低 8 位数据直接进入

图 1 M T90820 组成的交叉矩阵

表 4 恒定延时(V/C bit = 1)

| 输入速率        | 恒定延时模式下的延时(其中 m 为输出通道号,n 为输入通道号) |

|-------------|----------------------------------|

| 2.048Mb/ s  | 32 + (32 - n) + (m - 1)个时隙       |

| 4.096Mb/ s  | 64 + (64 - n) + (m - 1)个时隙       |

| 8. 192Mb/ s | 128 + (128 - n) + (m - 1)个时隙     |

表 3 可变延时 (V/C bit = 0)

| <i>t</i> △ \ `≠ <i>t</i> z | 可变延时模式下的延时(其中 m 为输出通道号 ,n 为输入通道号) |                     |           |  |  |  |  |

|----------------------------|-----------------------------------|---------------------|-----------|--|--|--|--|

| 输入速率                       | m < n                             | m = n, n + 1, n + 2 | m > n + 2 |  |  |  |  |

| 2.048Mb/ s                 | 32 - (n - m)个时隙                   | m - n + 32 个时隙      | m - n 个时隙 |  |  |  |  |

| 4. 096Mb/ s                | 64 - (n - m)个时隙                   | m - n + 64 个时隙      | m - n 个时隙 |  |  |  |  |

| 8. 192Mb/ s                | 128 - (n - m) 个时隙                 | m - n + 128 个时隙     | m - n 个时隙 |  |  |  |  |

| A7 | A6 | A5 | A4 | A3 | A2 | A1  | A0 | 存储单元                 |

|----|----|----|----|----|----|-----|----|----------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0  | 00H,控制寄存器,CR         |

| 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1  | 01H,接口模式选择寄存器,IMS    |

| 0  | 0  | 0  | 0  | 0  | 0  | 1   | 0  | 02H,帧同步寄存器,FAR       |

| 0  | 0  | 0  | 0  | 0  | 0  | 1   | 1  | 03H,帧输入偏移寄存器 0 ,FOR0 |

| 0  | 0  | 0  | 0  | 0  | 1  | 0   | 0  | 04H,帧输入偏移寄存器 1,FOR1  |

| 0  | 0  | 0  | 0  | 0  | 1  | 0   | 1  | 05H,帧输入偏移寄存器 2,FOR2  |

| 0  | 0  | 0  | 0  | 0  | 1  | 1   | 0  | 06H,帧输入偏移寄存器 3,FOR3  |

| 1  | 0  | 0  | 0  | 0  | 0  | 0   | 0  | Ch0                  |

| 1  | 0  | 0  | 0  | 0  | 0  | 0   | 1  | Ch1                  |

| 1  | 0  | 0  |    |    |    |     |    |                      |

| 1  | 0  | 0  | 1  | 1  | 1  | 1   | 0  | Ch30                 |

| 1  | 0  | 0  | 1  | 1  | 1  | 1   | 1  | Ch31                 |

| 1  | 0  | 1  | 0  | 0  | 0  | 0   | 0  | Ch32                 |

| 1  | 0  | 1  | 0  | 0  | 0  | 0   | 1  | Ch33                 |

| 1  | 0  | 1  |    |    |    |     |    |                      |

| 1  | 0  | 1  | 1  | 1  | 1  | 1   | 0  | Ch62                 |

| 1  | 0  | 1  | 1  | 1  | 1  | 1   | 1  | Ch63                 |

| 1  | 1  | 0  | 0  | 0  | 0  | 0   | 0  | Ch64                 |

| 1  | 1  | 0  | 0  | 0  | 0  | 0   | 1  | Ch65                 |

| 1  | 1  | 0  |    |    |    |     |    |                      |

| 1  | 1  | 1  | 1  | 1  | 1  | 1   | 0  | Ch126                |

| 1  | 1  | 1  | 1  | 1  | 1  | l 1 | 1  | Ch127                |

表 5 内部寄存器及地址存储器映象

注意:

- 1、在访问数据和连接存储器时 A7 必须置 1,访问寄存器时 A7 必须为 0。

- 2、当串口为 2Mb/s 速率时,通道数为 0~31。

- 3、当串口为 4Mb/s 速率时,通道数为 0~63。

- 4 当串行口为 8Mb/s 速率时,通道数为 0~127。

表 6 连接存储器单元

| <br>名   称   | 功能描述                                                                         |

|-------------|------------------------------------------------------------------------------|

| L PB K      | 各通道自环。当该位为 1 时,相应通道自环。在通道自环方式下,设置延时偏移寄存器 OFn[2 0]为 0                         |

| V/ C        | 可变/恒定通过延时。该位为0时相应通道选择可变延时;该位为1时,相应通道选择恒定延时方式                                 |

| MC          | 信息通道。为1时,连接存储器的低8位的内容将出现在相应码流通道的输出端;为0时,连接存储器内容作为被交换输入码流通道数据存储器的地址,进行交换方式的控制 |

| CSTo        | 控制 ST - BUS 输出。该位早一个通道出现在 CSTo 管脚 ,码流 0 的 CSTo 位先出                           |

| <u>OE</u>   | 输出使能。该位控制每一个通道的输出驱动。为 1 输出驱动功能正常 ;为 0 输出驱动置高阻态                               |

| SAB3 ~ SAB0 | 源码流地址位。二进制值就是连接源数据码流的数字号码                                                    |

| CAB6 ~ CAB0 | 源通道地址位。二进制值就是连接源通道的数字号码                                                      |

CPU,高8位数据通过第二次读取相应寄存器地址读取数据。

# 3.3 软件设计

#### 3.3.1 软件初始化 MT90820

- (1) 上电复位之后,连接存储器的内容处于不稳定态, ODE 管脚必须为低电平, 以使 ST BUS 输出为高阻态,直至处理器初始化交换矩阵完毕。

- (2) 块编程所有通道为高阻态,程序等待 2 帧之

# 后块编程有效。

- (3) 置 ODE 或 OSB 位为高电平,这时假如 OE 置位,任何连接都可以建立。

- (4)接着可以给不同码流设置偏移延时。

### 3.3.2 软件设计示例

控制寄存器选择输出码流,连接存储器地址低7位为输出通道号,其中SAB3~0选择输入码流, CAB6~0选择输入通道号。控制存储器及连接存储

| 表 7 | 以延时方式连接码流 STo15 | . 通道 14 至码流 STi2 | . 诵道 11 操作 |

|-----|-----------------|------------------|------------|

| 12  |                 | ᇪᇩᆦᅩᇏᆒᆒᇰᇄ        |            |

| 地址(00H)  | 地址(00H) 数据(000FH) |                                                    |    |      |    |          |          |  |  |  |

|----------|-------------------|----------------------------------------------------|----|------|----|----------|----------|--|--|--|

| 00000000 | Unus              | Unused(000000000) MBP(0) MS(0) STA3 $\sim$ 0(1111) |    |      |    |          |          |  |  |  |

|          |                   |                                                    |    |      |    |          |          |  |  |  |

| 地址(8EH)  |                   | 数据(090BH)                                          |    |      |    |          |          |  |  |  |

|          | L PB K            | V/C                                                | MC | CSTo | OE | SAB3 ~ 0 | CAB6 ~ 0 |  |  |  |

| 10001110 | 0                 | 0                                                  | 0  | 0    | 1  | 0010     | 0001011  |  |  |  |

#### 表 8 以恒定延时方式连接码流 STo14、通道 5 至码流 STi15、通道 1 的连接操作

| 地址(00H) 数据(000EH) |           |                |    |                |    |                 |          |  |  |

|-------------------|-----------|----------------|----|----------------|----|-----------------|----------|--|--|

| 00000000          | Unus      | sed(000000000) | N  | MBP(0) $MS(0)$ |    | STA3 ~ 0 (1110) |          |  |  |

|                   |           |                |    |                |    |                 |          |  |  |

| 地址(85H)           | 数据(4F01H) |                |    |                |    |                 |          |  |  |

|                   | L PB K    | V/C            | MC | CSTo           | OE | SAB3 ~ 0        | CAB6 ~ 0 |  |  |

| 10000101          | 0         | 1              | 0  | 0              | 1  | 1110            | 0000001  |  |  |

#### 表 9 以信息方式输出数据 1111 1111B 至 STo12、通道 64 的连接操作

| 地址(00H)  |        | 数据(000CH)       |    |                |    |                 |          |  |  |  |

|----------|--------|-----------------|----|----------------|----|-----------------|----------|--|--|--|

| 00000000 | Unus   | sed(0000000000) | N  | MBP(0) $MS(0)$ |    | STA3 ~ 0 (1100) |          |  |  |  |

|          |        |                 |    |                |    |                 |          |  |  |  |

| 地址(C0H)  |        | 数据(28FFH)       |    |                |    |                 |          |  |  |  |

|          | L PB K | V/ C            | MC | CSTo           | OE | SAB3 ~ 0        | CAB6 ~ 0 |  |  |  |

| 11000000 | 0      | 0               | 1  | 0              | 1  | 0001            | 1111111  |  |  |  |

### 器的具体操作示例如下:

- (1) 以可变延时方式连接码流 STo15、通道 14 至码流 STi2、通道 11(如表 7 所列)。

- (2) 以恒定延时方式完成 STo 14、通道 5 至 STi 15、通道 1 的连接,按表 8 所列方式操作。

- (3) 以信息方式输出数据 1111 1111B 至 STo 12、通道 64 的连接操作如表 9 所列。

如果要实现  $n \times 64kbit/s$  信号的交叉连接, 控制存储器设置为交换模式, 连接存储器置为恒定延时方式, n 次交换连接即可完成, 也能保持同一帧内

#### 8 比特序列的完整性。

如果要实现 2Mbit/s 信号的交叉连接,控制存储器设置为交换模式,连接存储器置为可变延时方式,32 次交换连接即可完成。

#### 编者注:

如对以上器件感兴趣,请与深圳和龙贸易有限 公司联系。

电话:0755 - 3220755 3608219

传真:0755 - 3608219

咨询编号:990103

#### 元器件快讯

# PMMAD 系列高频(RAIL CLAMP)保护器件

美国 PROTEK 公司近期推出专门为 RAIL CLAMP 保护而设计的 PMMAD 系列器件。完全替代 MOTOROLA 公司的 MMAD11XX 系列产品,符合 IEC1000 - 4 - 2、- 4 & - 5 标准。ESD 保护大于 40kV,工作电压大于 50V,峰值电流 40A,25pF 电容值。采用 14 或 16 脚 SOIC 封装。

# 应用范围:

RS - 232 & RS - 422 总线网络保护;

# 高频数据线保护;

10 Base T Networks;

Lans/Wans, Hubs, Routers, Servers

计算机 I/O 端口和大型数字式通讯系统保护

### 编者注:

详细资料请与西安虹飞公司联络。

电话:029 - 8483659 8481452

咨询编号:990116