## Technical Note

—Netin & Backannotation in Allegro & Capture

(Allegro中网络表的导入以及回编到Capture中的一些注意事项)

Created by Jacky\_Jin (金字华)

Application Engineer, Graser Technology

I can now be reached at the following address:

E-mail: <u>Jacky@graser.com.cn</u>

Tel: 0512-62523455-226

## 前言:

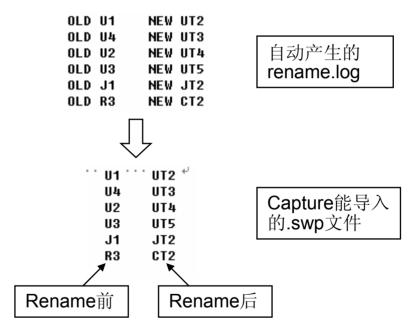

网络表(Netlist)是沟通电路原理图和Layout实际板子的桥梁 网络表包含的内容有零件Pin的连接线关系以及零件的包装等基本信息,

Cadence提供的Capture到Allegro新的网络表的转发除了可以把一基本信息带到PCB Layout中,还可以把一些layout时用到的设定、约束通过网络表带到Allegro中,使工程师在设计电路时就可以大致了解PCB板子上的布线情况,从而也节省了Layout工程师的时间,提高了工作效率! 例如: 电子工程师可以在原理图中把一些Power线设定好最小线宽,这样用新转法时就可以直接把设定带入Allegro,可以防止Layout工程师疏忽忘了设定走线没有达到要求。

相反把PCB上的信息反馈到原理图中,这过程一般称为回编(Backannotation),以保证实物PCB与原理图同步。例如: Layout工程师会对PCB上的零件作swap, rename等动作,为了保持PCB与原理图的统一必须把PCB中更改的内容回编到原理图中。

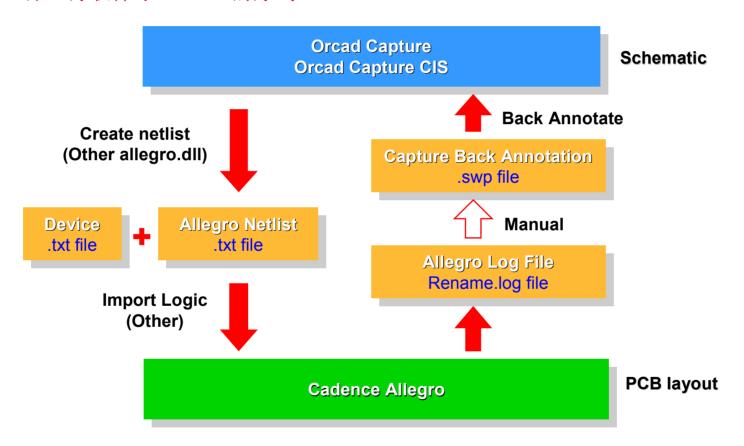

用Capture设计的原理图转入Allegro中有两种方式:

第一种,第三方软件导入netlist的方式

第二种,针对Cadence产品的直接导入方式,也称为新转法

下面内容将会对这两种方式的特定和操作做相应介绍。

## 第一种,第三方软件导入netlist的方式

优点: 在Capture中定义可以相对简单, 缺点: 导入网络表和回编原理图都相对复杂,导入时需要Device file,回编时需要提供.swp file

## 主要特点:

这种方式是Capture 9.2以前的版本产生网络表导入Allegro的唯一方法,就是通过Capture Create Netlist的Other方式,格式选Allegro.dll就可以了,现在很多公司还常使用这种方式。注意,在9.2以后的Capture中已经取消了这种转法,不过用户可以在9.2以前的版本中将allegro.dll复制到9.2以后的版本,放置路径预设 C: \Cadence\PSD14.1\Capture\Netforms,就可以使用这种转法了。

这种方式的主要优点: 在Capture中原理图的整理相对简单

主要缺点:导入网络表和回编原理图都相对复杂,导入时需要Device file,回编时需要手

动提供.swp file

#### 产生和导入网络表操作步骤:

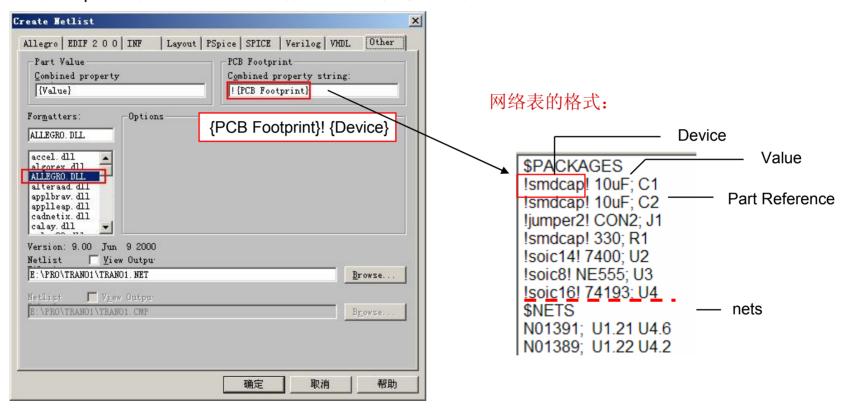

1。在Capture 中Create netlist 选择Other方式出现下图窗体:

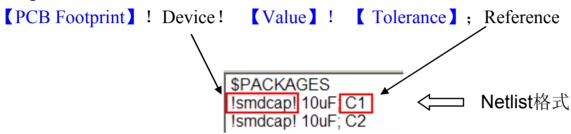

注意: {PCB Footprint}前面需要加"!",加叹号的作用是防止导入Allegro中产生错位(见下页)因为PCB Footprint名和Device一般相同,这里的{PCB Footprint} 产生网络表时对应的是Device项

#### 2. Import netlist preparing

Allegro导入网络表的格式: (其中【】中的内容可以省略)

因为Device中包含可以Footprint信息,所以网络表种PACKAGE部分只需包含Device和Reference就可以其它都可以省略。

产生Device的几种方式:

- 1。手动编写

- 2。9.2版的Capture有种转发直接产生

- 3。通过Skill产生 (如有疑问请联系)

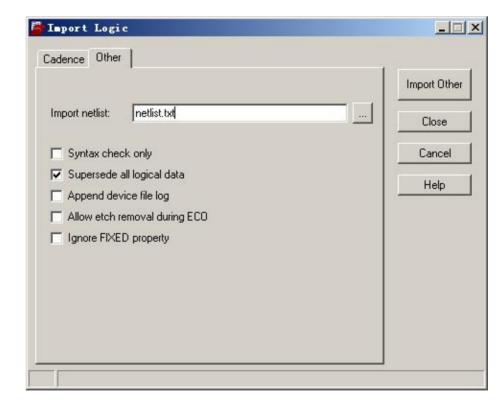

#### 3. Import netlist

在Allegro中选择Import Logic选择Other出现下面窗体,选择Netlist的路径

注意:要把Device文件放在当前工作路径或Env中预先定义好的Device路径中

- •只做语法检查

- •取代现有的Logic

- •追加device file 到netin.log

- •当netin时零件有改变就把相 应net走线删除

- •忽略Fixed设定

然后点击Import Logic就完成导入网络表了

## 从Capture回编到Allegro 中(Backannotation)

目的:保持PCB与原理图同步

主要回编内容:

- 1。Rename后的reference

- 2。Pin、Gate做了swap

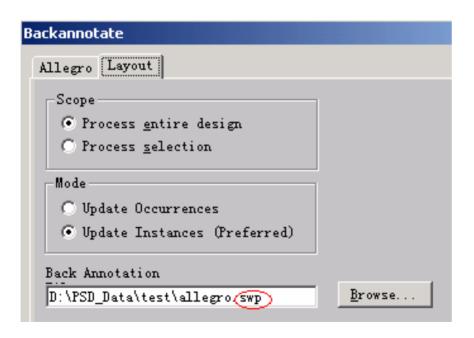

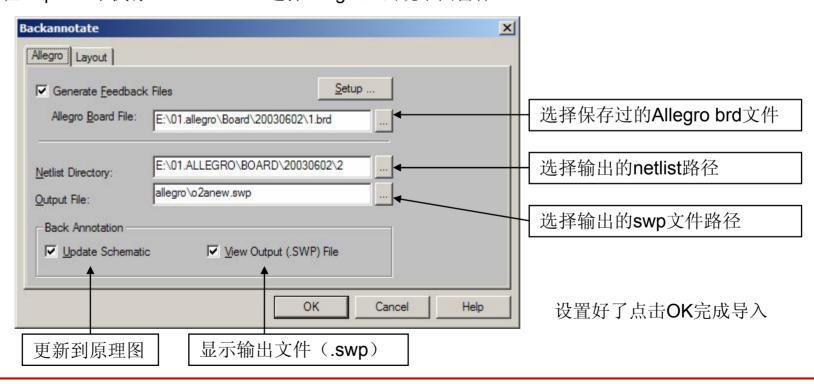

可以从Capture着手, Capture在执行Back annotate时选择Layout, 出现下面窗体:

回编需要的只有一个\*. Swp文件

把Allegro中更改的Reference以及做过swap的内容编辑到这\*.Swp就可以了,

具体这文件的格式可以参考下面内容:

## SWAP文件的格式:

普通文本文件格式,可以包含下面内容:

其中斜体部分就是swap的内容

1。CHANGEREF (改变零件Reference)

#### Examples:

CHANGEREF U1 U2 ; Change part reference U1 to U2 CHANGEREF U1A U1B ; Change part reference U1A to U1B U1C U2B ; Change part reference U1C to U2B,

注意:可以省略CHANGEREF,默认为改变Reference

2。GATESWAP (改变零件Gate Swap信息)

GATESWAP U1 U2 ; 改变 part U1 to U2 and part U2 to U1

GATESWAP U1A U1B ; 改变gates A and B on U1 GATESWAP U1C U2B ; 改变gates U1C and U2B

3。PINSWAP(改变零件Pin Swap信息)

PINSWAP U5B "D0" "D1" ; Swap the pins named D0 and D1 on U5B

PINSWAP U3 5 6 ; Swap pins 5 and 6 on U3

#### 回编操作步骤:

1. 当用户在Allegro中对零件Auto Rename完成后, 在当前目录下面会产生一个文档Rename.log,打开文 档可以看到是下面的形式的排列

这个文档不能直接被Capture导入, 需要修改内容,并存成.swp才可以

- 2。 Capture在执行Back annotate时选择Layout,选择相应swap文件就可以了

- Pin swap与Gate Swap只有编辑相应swp文件就可以了,不同的是需要记下swap过的零件,以便编辑swp文件。

## 第二种,针对Cadence产品的直接导入方式,也称为新转法

优点:导入方便,不需要Device档,而且可以把对symbol,net等的相关设定一起导入Allegro,

对于做过rename, swap, net logic等修改可以方便直接back annotate到Capture原理图中

缺点: 在Capture中要定义好所有零件的Pin name, Pin number以及Footprint, Pin name、number

不能重复,如果Pin type为Power则Pin name允许重复

## 主要特点:

Capture 9. 2以后的版本,即从9. 2. 1开始Capture针对Allegro提供了一种新的转netlist的方法,这种转法使Allegro与Capture沟通更加紧密,操作也更加简单。这种转法除了可以把一基本信息带到PCB Layout中,还可以把一些layout时用到的设定、约束通过网络表带到Allegro中,使工程师在设计电路时就可以大致了解PCB板子上的布线情况,从而也节省了Layout工程师的时间,提高了工作效率。当Layout工程师作

优点:导入方便,不需要Device档,而且可以把对symbol, net等的相关设定一起导入Allegro, 对于做过rename, swap, net logic等修改可以方便直接back annotate到Capture原理图中

缺点: 在Capture中要定义好所有零件的Pin name, Pin number以及Footprint等设定, Pin name、number不能重复,如果Pin type为Power则Pin name才允许重复

## 注意事项:

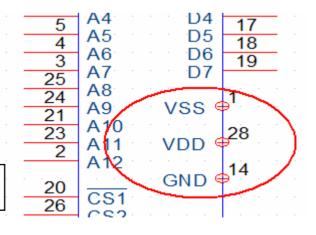

- 一.Capture原理图的准备工作

- 1。Part的Pin的定义

为了能顺利产生网络表,必须对Part Pin的 Name、Number和Type都要定义好,并且同一Part 的Name和Number是不能重复的,只有当Pin Type 为Power是Pin Name才允许相同

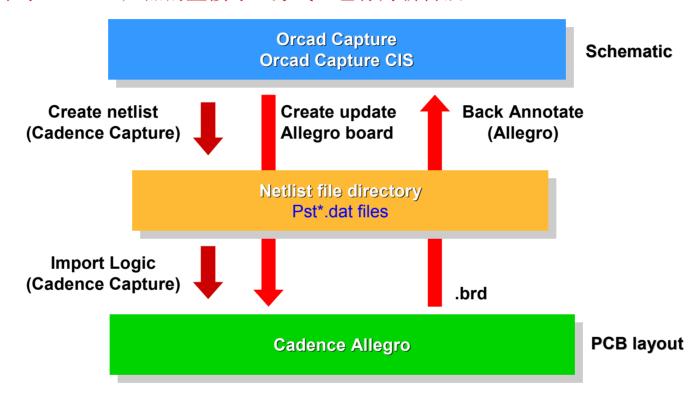

注意: 如果一个零件的Power Pin有好几种Pin Name, 而不同的Pin Name的Pin要接相同的Net, 如: Pin name为VDD但需要接到VCC, 而且Pin name为VSS也要接到VCC, 此时就必须对Capture 里的零件Part做一些设定

Part-Edit Properties

12 Allegro Technical Note

#### provide the best service!

2。Part的PCB Footprint的定义

Edit-Properties

的结果

出现下面窗体,设定PCB Footprint

| NO_SWAP_PIN   |        |

|---------------|--------|

| PART NUMBER   |        |

| PCB Footprint | soic16 |

| PIN_ESCAPE    |        |

| PINUSE        |        |

3。不同Part的Device设定必须不同

Edit-Properties在DEVICE栏设定值,不同Part的值不能相同,或者干脆不命名生成网表时CAPTURE会自动命名,使用他的封装,参数,还有其他的属性给他联合命名即类似"CAP NP 0805 0.1U"这就是自动命名

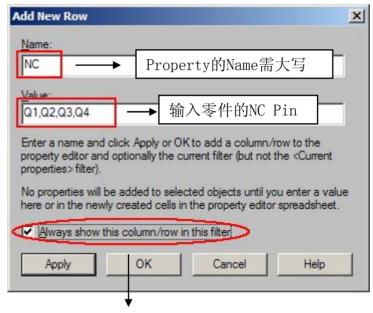

#### 4。NC Pin 定义

有的时候工程师在建Capture零件的时候会把 没有连接Net的Pin省略,而这些Pin在Lavout 实际零件上是有的,针对这种情况需要对 Capture里的零件Part做一下设定:

在Capture中双击Part进入Edit Properties 新增一项NC Property

点击 New Column... | 或 New Row... 出现右边的窗体:

#### 5。非法字符

有些字符在导入网络表时是不允许的,

例如: "

是否保存这Property到Capture, 如果打勾的 话Capture的的Edit-Property就多了NC这项

二. Capture to Allegro的新特性:

可以在Capture中就Part以及Net的相关设定定义好,把这些信息一 起导入到Allegro中。

#### Edit Properties - Part

| CLASS         |   | IC    |

|---------------|---|-------|

| FIX_ALL       |   |       |

| FIXED         |   | YES   |

| HEIGHT        |   |       |

| VALUE         | Г | NE555 |

| TOL           | Г |       |

| ROOM          | Г | T5    |

| PCB Footprint |   | soic8 |

| GROUP         |   |       |

#### Edit Properties - Net

| BUS_NAME                   | DADA1         |

|----------------------------|---------------|

| NET_SPACING_TYPE           | 10MIL         |

| NET_PHYSICAL_TYPE          | 8MIL          |

| PROPAGATION_DELAY          | L:S:2000:3000 |

| MIN_LINE_WIDTH             | 8MIL          |

| MAX_VIA_COUNT              | 2             |

| CLOCK_NET                  |               |

| RELATIVE_PROPAGATION_DELAY |               |

| DIFFERENTIAL_PAIR          |               |

| FCI                        |               |

#### 导入后Allegro中就有了相关设定:

Net: N03503

NET\_SPACING\_TYPE = 10MIL NET\_PHYSICAL\_TYPE = 8MIL  $MIN_LINE_WIDTH = 8 MIL$

BUS\_NAME = DADA1

LOGICAL\_PATH = @o2anew.schematic1(sch\_1):n03503

PROPAGATION\_DELAY = L:S:2000 MIL:3000 MIL

MAX VIA COU $\overline{N}T = 2$

#### 操作步骤:

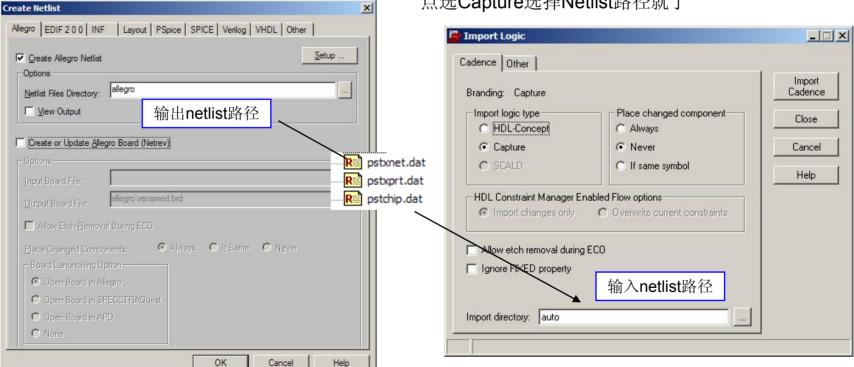

1。在Capture里执行Create netlist 选择Allegro,勾选Create Allegro Netlist,选择输出的路径

注意:这里产生的Netlist 有好几个文件, 所以只要选择路径就可以了

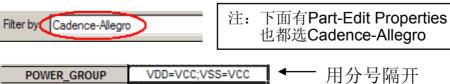

2。在Allegro中执行Import Logic选择Cadence, 点选Capture选择Netlist路径就了

## provide the best service!

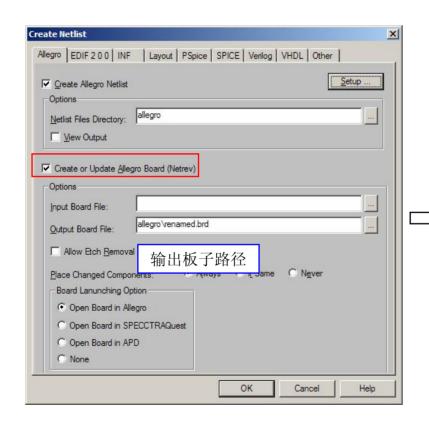

Capture产生网络表直接输出到Allegro板子

这种方法直接可以把网络表输出到Allegro板子并在Allegro中打开

在Create Netlist窗体中选择: Create or Update Allegro Board

#### 其中:

Input Board File:是指输入到现有的板子

Output Board File:是产生新的板子

## 新转法从Allegro回编到Capture

将Allegro中做过 Rename,Swap,Net Logic以及对零件和Net的Property做过修改都可以返回 Capture中,而仅需要一个Allegro的.brd文件就可以了,操作非常方便,具体见下面内容。

#### 操作步骤:

在Capture 中执行Backannotate 选择Allegro, 出现下面窗体:

#### 补充:

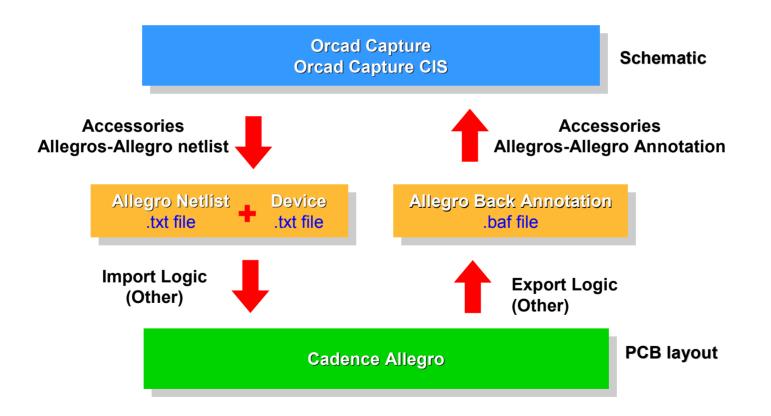

除了以上提到的两种转法以外,还有一种方式,这种只针对9.2版本的Capture有效,这种方式是新转法前的一种比较简单的方法,可以直接产生Device,回编也只要在Allegro输出.baf文件导入Capture就可以了,这里不做详细介绍了。见下面框图:

# THE END!

provide the best service!