# Protel99SE核用说明

\_\_\_\_\_ 本振频率合成及话放调相电路实例

电子技术应用

www.ChinaAET.com

# 一、序言: 电路设计软件简介

本次高频实验所用的电子设计软件叫 Prote199SE, 但确切来说, 功能强大的 PROTEL99SE 已不只是电子设计软件了, 应叫 EDA (ELECTRONIC DESIGN AUTOMATION 电子设计自动化)软件, 不过叫法怎样都不要紧, 但是你应知道 PROTEL99SE 在电子设计软件的地位及其功能。

#### 一、常见的电路设计软件

我们较容易找到的电子设计软件有 PROTEL99SE 、 PSPICE8. 0 、 ELECTRONIC WORKBENCH 5. 0a 和 WINBOARD, 其中 PROTEL99SE 是最强大的, 功能最全面的, 代表着 当今 PC 机桌面 EDA 工具的发展方向。而 PSPICE8. 0 是最专业 PC 上的仿真软件, 仿真功能上能超越 PROTEL99SE 的 SIM(仿真程序模块)。

#### 二 PROTEL99SE 的组成功能模块

\*SCH99:绘制电路原理图的程序模块。

\*PCB99:将原理图进行电路板布线的程序模块。

\*ROUTE99: PROTEL99 中 PCB 的布线引擎,极其强大,我们布线时会将其调用。

\*PLD99:我们正在学的 PLC 就是它,内部有我们做实验的三菱 F1 系列 PLC 模型,可进行编程、编译、仿真等,但不在本文介绍范围内。

\*SIM99:仿真程序模块,可进行模拟、数字混合仿真。

注: 如果对部分英语词汇不理解,请参考附录的 Prote199 词汇.

词汇: Schimietic skimetic v. 绘图。

Simulate simju:ileit v. 仿真。

我们上面电子设计软件比较中,PSPICE8.0 、 ELECTRONIC WORKBENCH 5.0a 同 PROTEL99SE 的程序模块之一 SIM98 进行比较,从而知道 PROTEL98SE 的功能是比别 的电子设计软件多得多,我们的实验中只使用 SCH 和 PCB,这点必须清楚。

本文将详细讲述使用 PROTEL 99SE 的 SCH (SCHIMETIC 绘制电路原理图)和 PCB (电路原理图的电路板布线)来完成我们高频实验指导书 P62 页的高频小信号放

大器的绘图及布线。但在此之前,你必须对 PROTEL98 这个一体化的电路设计软件作一初步认识。

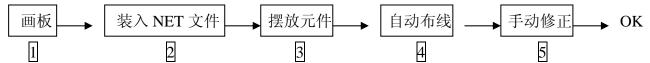

## 2. Prote199SE 的一般设计流程

**A.** 说明:在 SCH 中画原理图,则系统自动生成的文件\*. SCH,在 SCH 可直接调用仿真程序 SIM,检验电路的设计是否正确,如测试输入、输出端的信号波形是否合理.如果正确的话,你就可以让 SCH 生成\*. NET 文件(注:具体方法以后详细介绍),就可以将\*. NET 文件调入布线程序 PCB(注:PCB 只认\*. NET 文件)进行自动布线了.

B. 在本文暂不介绍仿真程序 SIM, 因为其涉及一些较复杂的分析设定. 而且对电路 图是否进行仿真是不影响布线的。影响布线的只是原理图中各个元件的封装。不明白? 不要紧,往下看迟些你自然会理解。所以,我们的设计流程变得更加简单了:

虽然设计流程简化了,但你别高兴,因为在 PCB 中将涉及很复杂且繁锁、细微的操作,因此你真想掌握 PROTEL99SE 的话,非继续认真学不可。

C. 如果对以上内容不太理解的话,也没关系,因为以后就要通过对我们上学期做过实验的本振频率合成从画图到布线具体实现了。

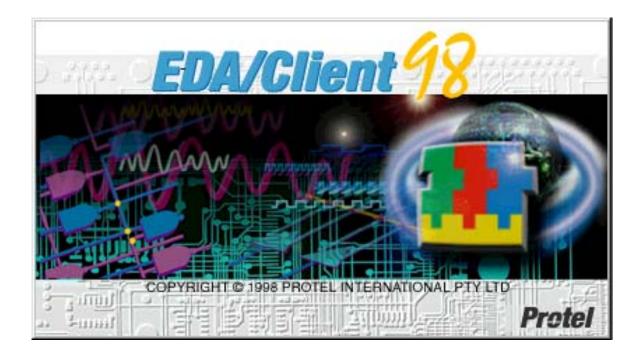

D. 现在让你知道学完部分后,你将画出本振频率合成和话放调相电路的原理图一,以及其布线图 (PCB 部分),其中画原理图是比较容易的,但由原理图的布线就难一点了,要进行很多设定。

本振频率合成及话放调相电路

图一

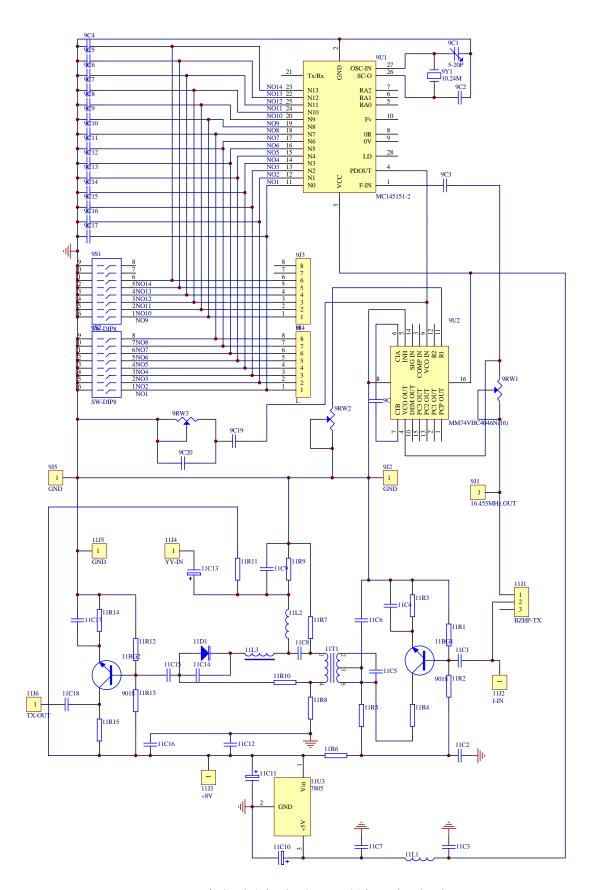

下面先熟悉一下 PROTEL99SE 的主界面的基本组成.

# 二. SCH 部分

在认真学完本节后, 你将能绘出上面图一并且完成对原理图中各个元件的参数设定.

# ❤ 设定图纸的大小

在放置元件前可按自己的需要对电路图纸大小进行设定。

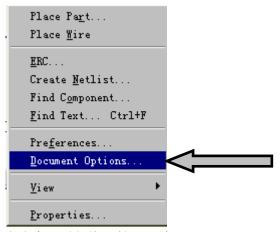

方法: 编辑区中鼠标右键 → Document Options 在对话框的 Sheet Options(工作表选项)的 Standard Style 框(标准类型)或 Custom Style(自定义类型)中设置纸张的大小,

击鼠标右键弹出的对话框

用户自己定义的纸张大小

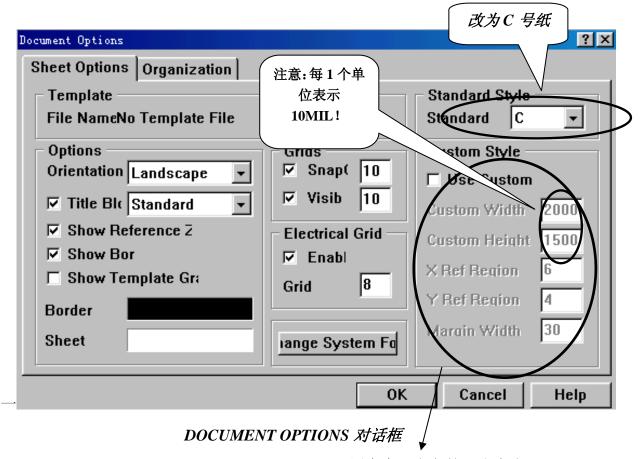

系统默认下,电路图纸为 B,因电路图较大,我现在把它改为 C,在 Standard Style(注:这里选

取的都是标准大小的纸如 A4, B4 等)框的 Sstandard 内容选为 C。

另外,Custom Style 是用户自己定义的纸张大小(选中 USE Custom 才可以自定义大小),系统默认的单位为毫寸(MIL),因为在电子领域国内外都是用英制单位,

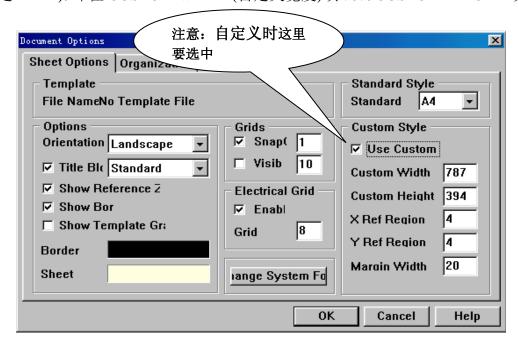

那么,我想用一张非标准大小的纸张,如:宽\*高= 20CM\*10CM,就需先转化为英制单位,宽=(20/2.54X)\*1000=7870MIL,高=(10/2.54)\*1000=3940MIL,但不知何故,在这里的最小单位为10MIL,所以宽X高=787(10MIL)\*394(10MIL),(注:在PCB中则没有这种现象,你所填的数字的单位都是1MIL),即在CUSTOM WIDTH(自定义宽度)填787,CUSTOM HEIGHT填394即可。

用户自己定义的纸张大小设定好后的DOCUMENT OPTIONS 对话框

#### 一、从元件库中取元件.

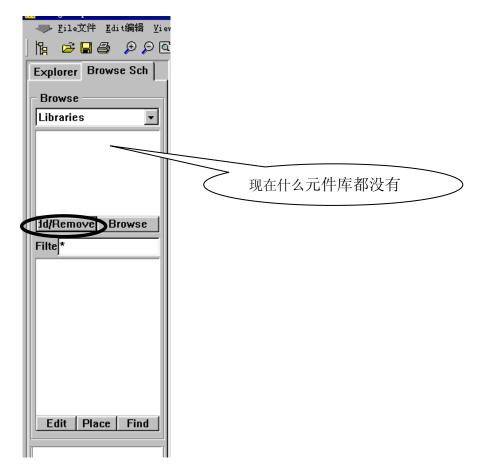

- 2. 装载元件库的方法是:

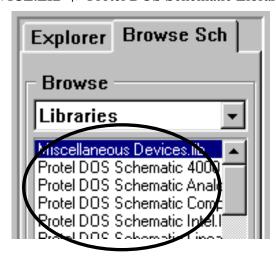

打开设计管理器,选择"BROWSE SCH"选项卡,单击"ADD/REMOVE"按钮添加元库,

在弹出对话框中双击要添加的元件库到列表中或单击底部 Add。再单击 OK 即可。

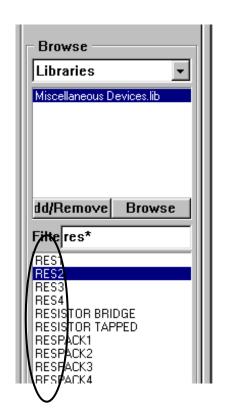

如 MISCELLANEOUS DEVICE.LIB 和 Protel DOS Schematic Libraries 加入后如下图所示:

#### 4. 置(PLACE)自己所要的元件。

可以看到 LIBRARY 框中多了一个 MISCELLANEOUS DEVICE.LIB, 这是当前元件库, 因为现在只装入一个库, MISCELLANEOUS DEVICE.LIB 自然为当前库。

当装入多个元件库时,也只能一个当前库,其它则为备用库。元件则只能从当前库取出,用 LIBRARY 框中的 (下拉按钮) ☑ 点击选取来改变当前库。在 COMPONENTS IN LIBRARY 框中列 出当前库中的元件。(词汇:COMPONENT n.元件)在列表中选取相应的元件,双击即元件处于放置 状态(随鼠标移动),这样就可将元件放到编辑区中相应的位置。

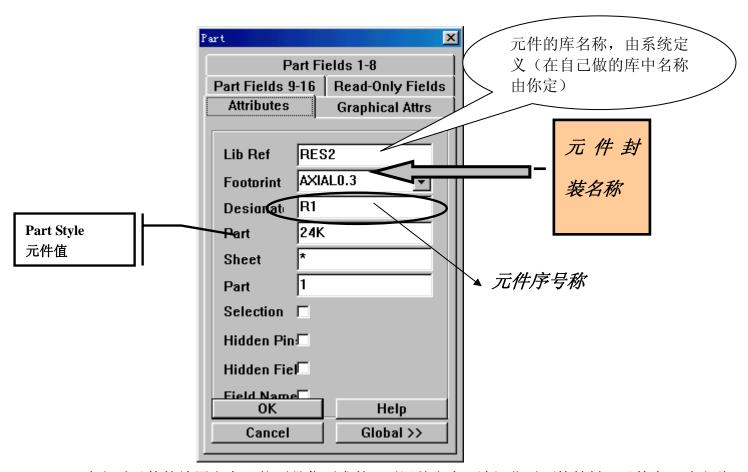

说明:元件列表框中列出的是元件在所属元件库中的标准名称,相应于元件属性对话框(在编辑区双击指定的元件即弹出)中的 LIBREF 的内容如下图所示。其它属性也顺便说一下。

选取后元件的放置方向可能不是你要求的,要调整方向,请记住以下快捷键,元件在已选取移动状态下。

**CTRL+X** : 水平翻转

CTRL+Y : 垂直翻转

**CTRL+空格** : 每次 90 度旋转□ 由于在元件列表框中元件很多,以上方法的放置元件速度是比较慢的,如果在你已记得元件的库名称的前提下,可用另一个快的方法:

方法: 编辑区任意位置单击鼠标右键 → Place Part (词汇:PART n.元件) → 在 Place Part 对 话框中输入元件的库名称 → 输入元件序号 → OK 即可 。

#### 基本常用元件的库名称

| <i>基本吊用几件的件名物</i> |                                |          |  |  |  |

|-------------------|--------------------------------|----------|--|--|--|

| 元件名               | 元件的库名称                         | 符号       |  |  |  |

| 无极性电容             | CAP                            |          |  |  |  |

| 有极性电容             | CAPACITOR POL<br>词汇: POLY n.极性 | _+ (_    |  |  |  |

| 可变电容              | CAPVAR                         | <b>+</b> |  |  |  |

| 电阻                | RES2                           |          |  |  |  |

| 可变电阻              | RES4                           |          |  |  |  |

| 电感                | INDUCTOR                       |          |  |  |  |

| 可变电感              | INDUCTOR3                      |          |  |  |  |

| 带铁心电感             | INDUCTOR2                      | <u></u>  |  |  |  |

| 带铁心可变电感           | INDUCTOR4                      | <u>_</u> |  |  |  |

| 变压器               | TRANS1                         | 318      |  |  |  |

| 带抽头变压器            | TRANS4                         | 312      |  |  |  |

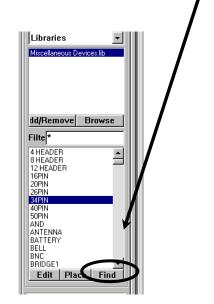

上面所讲的放置元件的方法只适用了已知元件的库名称以及所属元件库的情况下,当不知道元件的所属时,最好就是用 COMPONENTS IN LIBRARY 中的 FIND (元件查找)功能,

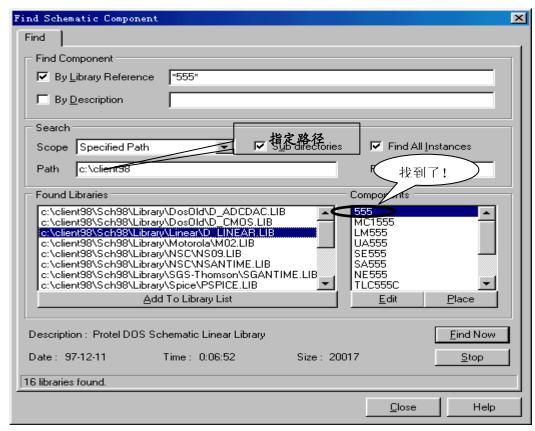

在FIND SCHEMETIC COMPONENTS 对话框

方法: FIND → 在 FIND SCHEMETIC COMPONENTS 对话框的 BY LIBRARY REFERENCE(元件的库名称)中填入\*555\*(支持通配符),其余选项用系统默认值,按 FIND NOW 即可。

一会儿后在 FOUND LIBRARIES 中列出找到含有\*555\*的元件库,在 COMPONENTS 中列出库中的元件,双击即可进入元件的选取放置状态。

通过上面的学习,你应基本掌握从 PROTEL99SE 提供的元件库中找到自己所需的元件。一般认为,画电路图先把所有元件(至少大部分)都从库拿出来放在电路图大概的位置上,再连线,这样做的效率是较高的。

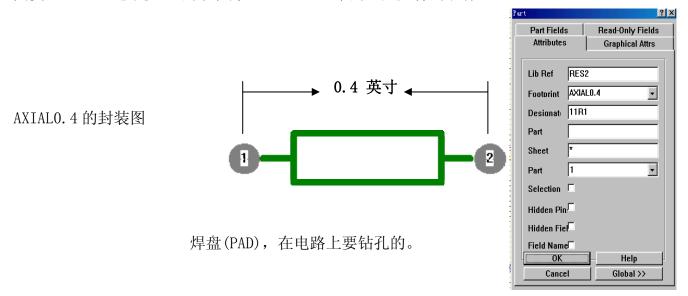

3. 你看看这个电路图就可以发现,它不仅有齐了各种基本元件,电阻,无极性电容,有极性电容,三极管,电感,变阻器等,还有变压器,变容二极管,多项开关,晶振和集成块。这里先介绍元件库里有的元件。由于有极性与无极性电容的封装(FOOTPRINT)不同,所以要区分开来。注:PCB中的元件就是 SCH中元件的封装。如 SCH中的电阻 R,在其属性对话框中设定其封装为 AXIAL0.4,其中的单位是英寸,1 英寸=2.54CM。AXIAL 是柱状封装。

# 元件列表

| 取用元件名称     | 所属元件库                       | 元件封装名称 |

|------------|-----------------------------|--------|

| CAP(注:无极性) | MISCELLANEOUS<br>DEVICE.LIB | RAD0.2 |

| CAPACITOR POL (注:有极性<br>电容) | MISCELLANEOUS<br>DEVICE.LIB       | RB.1/.2     |  |

|-----------------------------|-----------------------------------|-------------|--|

| RES2                        | MISCELLANEOUS<br>DEVICE.LIB       | AXIAL0.4    |  |

| MC7805T                     | Protel DOS Schematic<br>Libraries | TO-220(2)   |  |

| MM74VHC4046N(16)            | 自制的元件库                            | DIP16       |  |

| TRANS4                      | MISCELLANEOUS<br>DEVICE.LIB       | ZZ          |  |

| SW DIP-8                    | MISCELLANEOUS<br>DEVICE.LIB       | DIP16       |  |

| CAPVAR                      | MISCELLANEOUS<br>DEVICE.LIB       | CVAR        |  |

| CRYSTAL                     | MISCELLANEOUS<br>DEVICE.LIB       | XTAL1       |  |

| MC145151-2                  | 自制的元件库                            | DIP28       |  |

| INDUCTOR1                   | MISCELLANEOUS<br>DEVICE.LIB       | AXIAL0.5    |  |

| INDUCTOR2                   | MISCELLANEOUS<br>DEVICE.LIB       | DG          |  |

| DIODE VARACTOR              | MISCELLANEOUS<br>DEVICE.LIB       | DIODE0.4(2) |  |

| NPN2                        | 自制的元件库                            | TO-39       |  |

上表列出本振频率合成及话放调相电路所用元件的名称,所属库,元件封装 说明: **A.**元件名称有些是元件库(DEVICE.LIB)中的标准名称有些是我自己做的元件名称

**B.**在 SCH 中每个元件必须指明封装,才能调进 PCB 中布线,不指明的话,调入 PCB 时元件丢失,并提示出错。

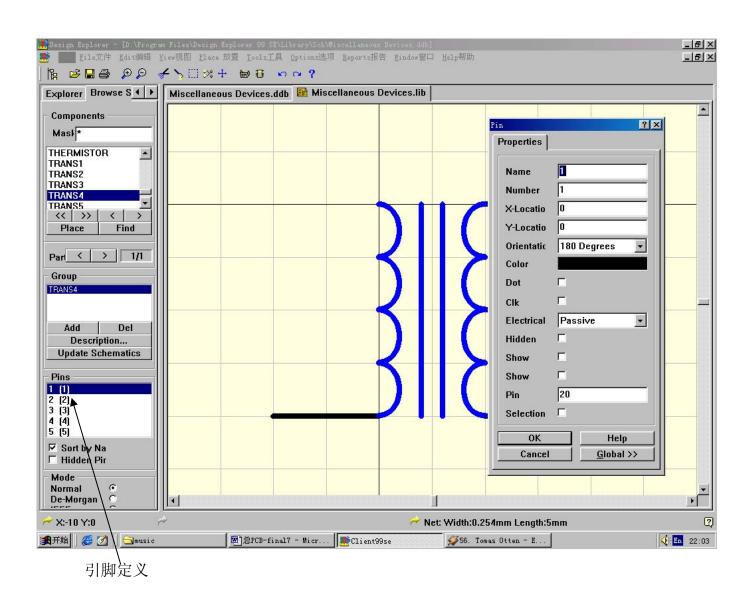

另外,SCH 库中有些元件是找不到的,需要自己做。像 MM74VHC4046N(16)和 MC145151-2 等,可能库里面有,但其实可以自己做,这样可以更能符合自己的要求。而其中有一些元件虽然在库中有它的元件图样,但需要该变一下它的引脚定义(也可改变封装的引脚定义),如我这里的CAPACITOR,MC7805T,DIODE,VARACTOR,NPN2,我都改了它们的引脚定义。做自己的元件库可以这样做:

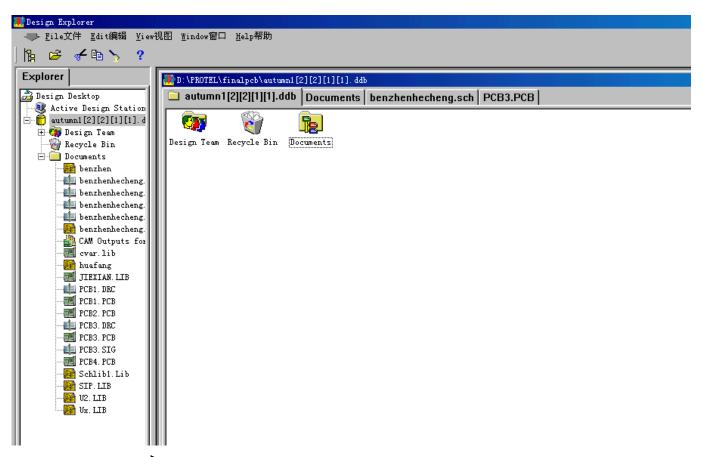

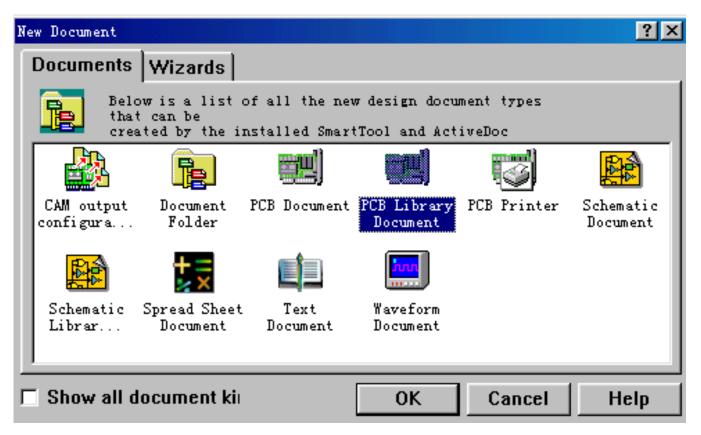

1. 新建元件库,在下面的对话框中双击 Documents 选项卡确定文件存放位置,

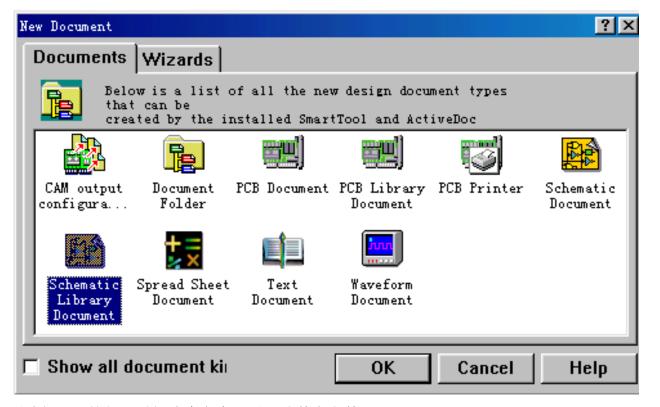

然后选择 FILE ──NEW 在下面的对话框中选择 Schematic Library Document

后选择 OK 就行。最好该个名字,以区分其它文件。

#### 2. 修改元件名

在新建的元件库中,已有一个名位 Component\_1 的元件,执行菜单 Tools — Rename Component,将其名改为自己想要的名字,最好是元件的名字。如这里我用了 MC145151-2 集成块的名字做它的元件名。

3. 放大工作窗口并执行菜单 Edit\_→Jump \_\_→Origin,将光标定位原点。

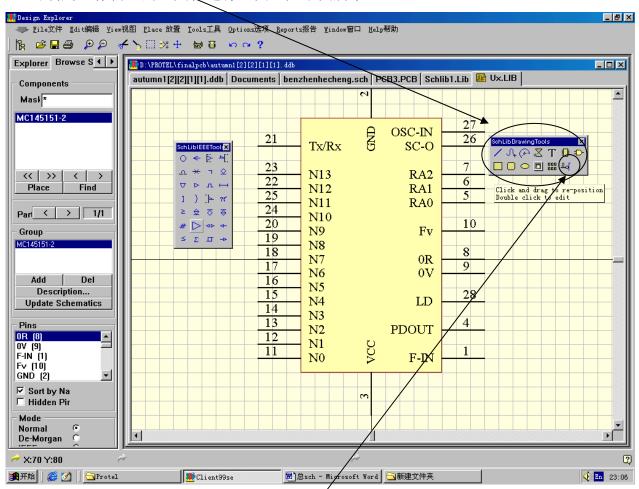

4. 可利用工作窗口的工具栏进行画图,如下图所示:

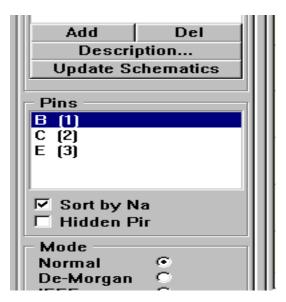

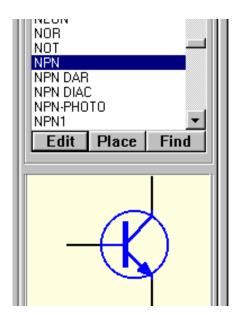

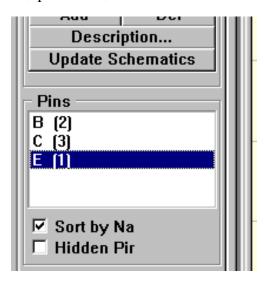

在放置管脚的时候,要选择 Place → Pins 或在工具栏上选择。其方向可以随意该变,但应知道,在移动它的时候,要将大圆头的一边放在向外的一边,表示接另外的电路,否则在封装的时候就会出错(线没接上)。图形可以复制,用 Ctrl+C 的方法可以将图形复制到另外一个元件上,可提高效率。我在改变一些元件的时候就用到了复制,如 NPN2,因它和封装的引脚(pins)定义不同

在 MISCELLANEOUS DEVICE.LIB 中找到 NPN 单击 Edit 就打开三极管的编辑画面,选好三极管的图形复制到我们的库中,然后将 pins 引脚改成下图所示 B(2)、C(3)、E(1)。

名字改成了 NPN2,这样才能和实物的 B、C、E 接脚对上(PCB 部分将会说明)。

5. 最后将做好的元件放在一个库里面了。再点击 ADD/Remove 添加刚才建立的库(文件保存的地方),就能像 MISCELLANEOUS DEVICE.LIB 中的元件一样用了。

除 RES2,CRYSTAL,CAP,SW-DIP8,MC145151-2,MM74VHC4046N(16)的封装能在 PCB 的默认元件库 Miscellaneous Devices.lib 中能找到,其它的都需自己利用 PCB 的元件库编辑程序编制的。

为何要自己编呢?其实 PCB 的库中也可能有合适的封装,但由于我们高频课程设计中用到的元件在软件的 PCB 库中可能找不到合适的封装,那就必须要详细介绍如何自己编辑出元件的封装。

<u>注:</u>SCH 的库与 PCB 的库是完全不同的,PCB 的库只是元件型状,引脚的一种联合,完全没有电气特性,SCH 到 PCB 是靠元件引脚的序号来传递的。

#### 放置元件前应掌握的技巧

放置元件必须熟悉一些基本的操作技巧, 否则你会事倍功半。

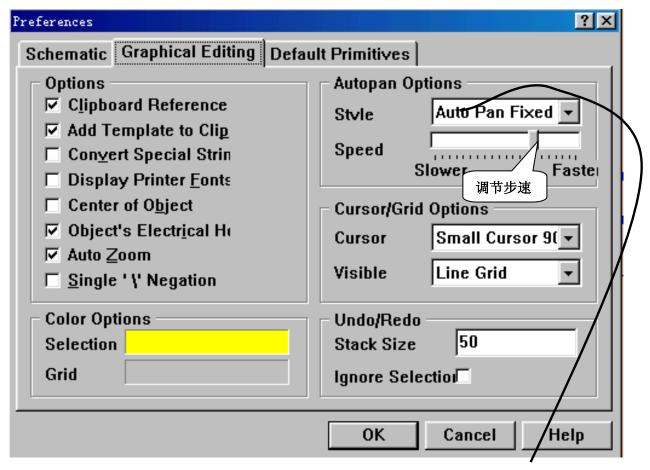

当元件在选取移动状态下,移动鼠标到编辑区的边框时,图纸也随之移动,但你是否感到移动速度是否太快了,以致于有点无法控制。这是 PROTEL 设计者的失误,把拉线的步速设得太大了。

那么就让我们自己来设定步速。

方法: TOOLS → PREFERENCES...(参数) → GRAPHICAL EDITING(图形编辑)选项卡中的 AUTOPAN OPTIONS(自动面板选项) → 设置 SPEED

将滑动块左右移动就能调节步速。但我强力推荐将 STYLE 选为 AUTO PAN RECENTER,这是电路板以鼠标为中心移动,该模式的速度是最快的,而且容易控制。这时 SPEED 调节是不起作用的。

说明一下: 你会在该对话框中看到眼花的各种选项,其中有很多我们是根本不需用的,如果要系统地了解各选项是非常费时的,所以在本文只谈及与本实验有关的选项。

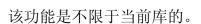

#### 放置元件

放置电阻(RES2)。首先确认元件库管理器的 LIBRARY 内容为 MISCELLANEOUS DEVICE.LIB。 在 COMPONENT IN LIBRARY 中的快速查找 filte 中填入 RES\*再确定,则立即查出各种 RES 开头的元件名,双击 RES2 放置电阻。如下图。重复上面的操作大致放置完所有电阻。

CTRL +空格: 90 度逆时旋转

CTRL + X: 水平翻转

CTRL + Y: 垂直翻转

在这里再次强调放置元件时请记住:

#### 画线

鼠标右键──→ PLACE WIRE 则鼠标处于画线状态

在此之前请记住将 PREFERENCE... → GRAPHICAL EDITING → STYLE 设为 AUOT PAN RECENTER。

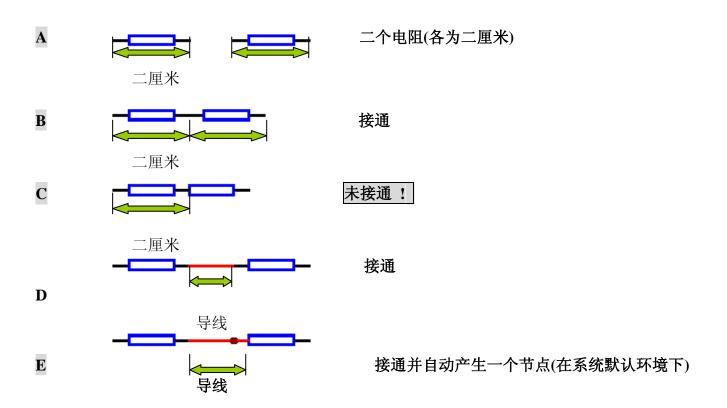

在这里只谈一点最重要的,就是怎样画才能使元件间或导线与元件是接通的,因为有些连接看上去是连通的,实际却是不通的。

**总结:**不接通的情况只有一种(**C**):就是元件的引脚(pin)交接到了要连接元件的"元件体"时就是未接通了,这点必须注意,因为这样的错误会引起在 PCB 出错。

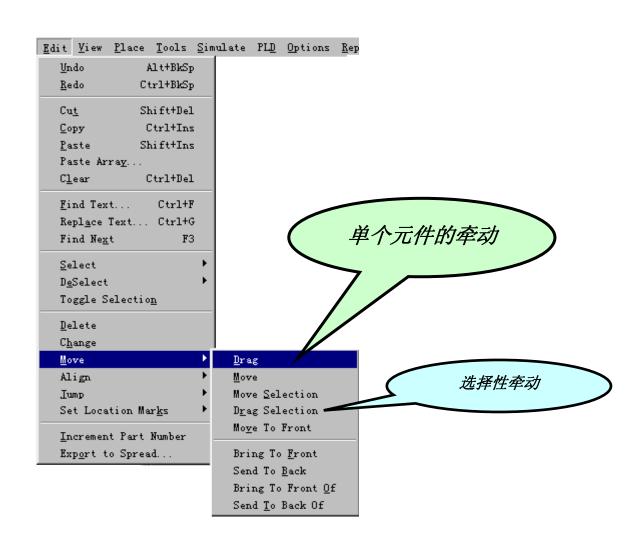

▲ 在画线时还必须掌握一些基本技巧,在这里只谈及单个元件的牵动及选择性牵动。

#### A.单个元件的牵动(DRAG)

你在电路图用鼠标拖动已接好的元件时,发觉拖动使原来已接好的线都断开了,改变电路图的电气特性,这样就不便于整理元件在电路图中的位置。那就需牵动来解决,牵动是不影响电路图的电气特性。

# 方法: EDIT 菜单 \_\_\_\_\_MOVE \_\_\_\_\_DRAG

启动该命令后,会发觉鼠标的状态变了十字架,单击需牵动的元件,按住鼠标左键牵动到适 当的位置即可。

#### B. 选择性牵动(Selection Drag)

当你大概完成整张电路图的绘制时,发现某电路图部分的位置挤得太紧或太松,想调整一个某部分的位置时,如果逐个元件改动,则效率实在太低了,利用选择性牵动则可大为提高效率。

方法: 选择要牵动的部分 → EDIT → MOVE → DRAG SELECTION 与单个元件的牵动类似,只是首先按住鼠标左键拉出方框,将要牵动的电路部分选中,则该部分的颜色会改变。还有一点值得注意的是放置信号端或地。

|    | <b>900</b> 0<br>О | 圆形(CIRCLE)         | )              |        |

|----|-------------------|--------------------|----------------|--------|

| 信号 | vc:               | 箭头形(ARROW)         |                |        |

| 端  | woc<br>T          | 条形(BAR)            |                | 4 种信号端 |

|    | 1000<br>1         | 波形(WAVE)           |                |        |

|    | <del> </del> +    | 电源地(POWER GROUND)  | $\bigg]\bigg)$ |        |

| 地  | 4                 | 信号地(SIGNAL GROUND) | }              | 3 种地   |

|    | ж                 | 一般地(EARTH)         |                |        |

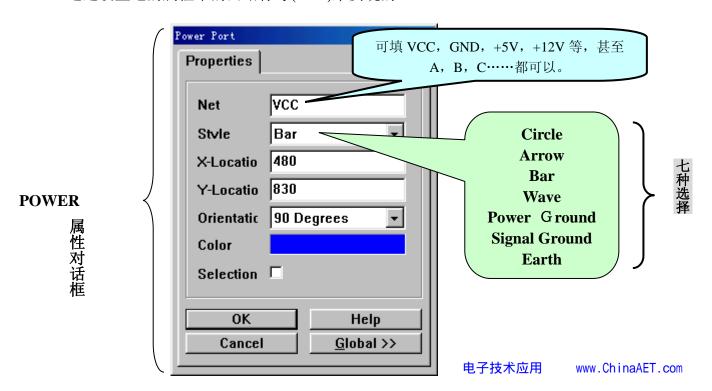

Protel 99SE 提供了 4 种信号端和 3 种地。它们有什么区别呢? 从外表看最明显的就是形状的差别,用来区分不同的信号端或地,例如有些电路的变压器的初级和次级的地是需要隔离的,那么使用不同外形的地进行外形上的区别,如初级用 —— 次级用 —— 次级用 —— 次级用 —— ,但实质上隔离是通过设置地的属性中的网络标号(NET)来实现的。

注:网络标号在 SCH 中是有电气特性的,相当于电路图中节点的名称,若不同位置的节点名称相同的话,则分别连在这些节点的所有元件都实质上全连通了。

网络标号与节点名的区别在于节点名是由系统自动分配的,网络标号可以是自己在电路图上插入,或对可设置网络标号的元件(如:信号端和地等)进行设置。

按上面所说,把初级网络标号设为 GND,次级设为 0 V,则无论使用哪种形状的地,初级、次级的地都是连通的。

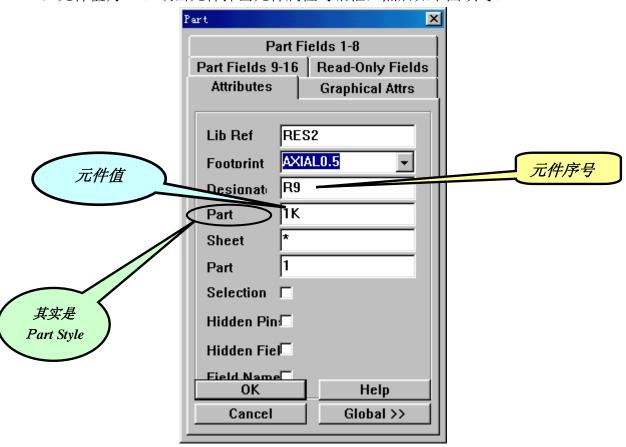

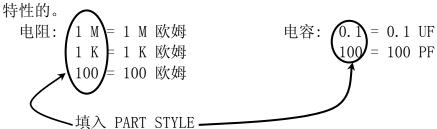

但各元还没有排好元件序号(DESIGNATOR)和元件值(PART STYLE),如把电阻的元件序号设为R9,元件值为1K。双击元件弹出元件属性对话框,然后如下图填写。

注意: 在图中的 PART STYLE 由于 WINDOWS 中字体的不同,而引起只显示了 PART。该项是有电气

注: 电阻:在 PART STYLE 填入 1K,则系统能自动识别出该电阻为 1 K 欧姆

电容:要想设为 0.1uF,则在 PART STYLE 填入 0.1 或 0.1u 都可以。现在就可以按电路图分配各个元件的序号和元件值。这步完成后则 SCH 的任务基本完成。

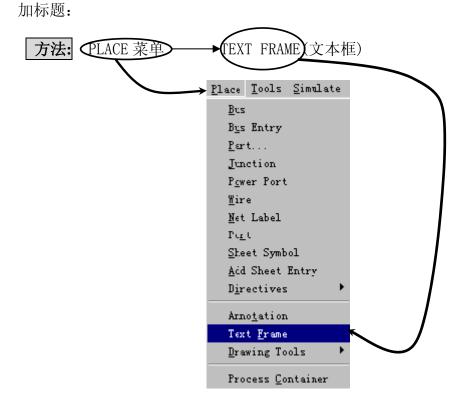

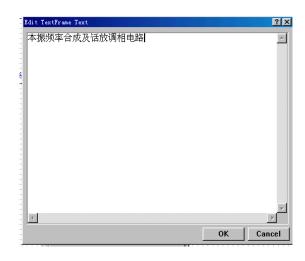

启动该命令后, 鼠标变成十字架状态:

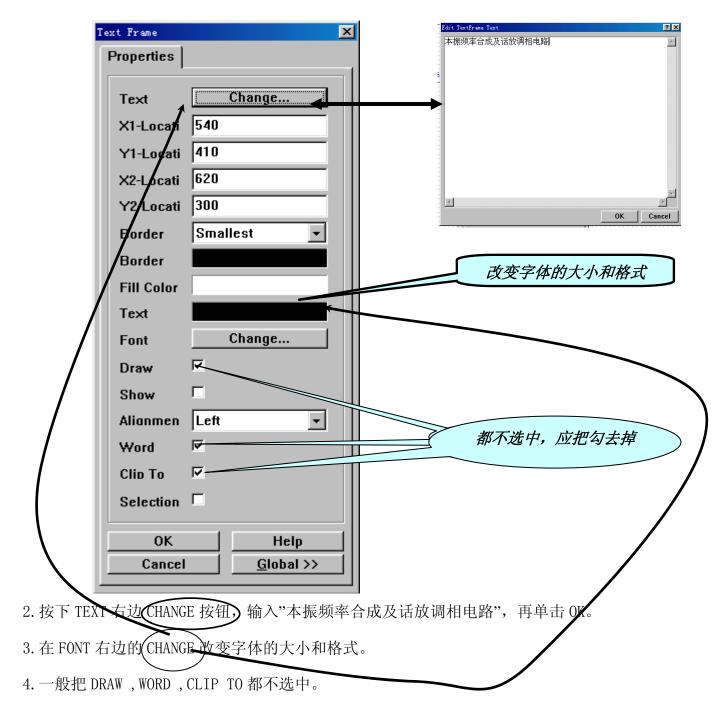

1. 按一下鼠标左键定位文本框的左上角,再按第二下定位文本框的右下角,再双击文本框出现 TEXT FRAME 属性对话框:

5. 再按 OK 即把"本振频率合成及话放调相电路"标题放置在电路图上,用鼠标拖动 TEXT FRAME 的 边框即可改变边框大小。

#### SCH 部分完

### 三: 本振频率合成及话放调相电路的 PCB 制作

第一部分已介绍的用 SCH 绘制本振频率合成及话放调相电路图,由于 SCH 使用比较简单,很多内容我都是点到即止,没有加上详细说明。但到 PCB 就不能这样了,PCB 的使用比 SCH 难多了,要用 PCB 对一个原理图按自己的要求成功地完成布线,就要很多工作要完成,进行很多布线规则设定(如焊盘大小,走线宽度等)特别是高频布线,那就要求你对本部分的内容要认真去理解了。

# 3-1、布线的基础知识

## <1>认识电路板

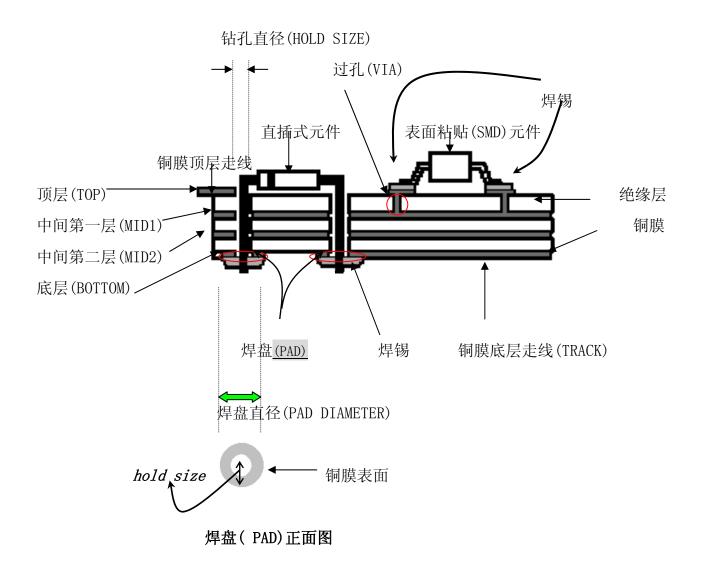

印刷电路板 (PCB --- PRINT CIRCUIT BOARD) 就是将我们的电路原理图做成铜膜走线,放在绝缘板层上。现在看看电路板的结构,虽然我们的实验数据最多只用到两层板,但为了你更易理解 PCB中的一些选项及设定,现介绍市面上技术成熟的四层板。

## 电路板结构截面图

该图是底层、顶层(BOTTOM, TOP)各一层,中间两个电源层(VCC 及地)共四层。板层的多少能在设定规则中设定,将在后面详细介绍。本实验电路板就只用了两层板(顶层和底层),

#### <2>设定封装

#### 1.封装介绍

PCB 的元件就是封装,如 SCH 中,本实验的电阻的封装都设为

长度为 0.4 英寸,约 1.0CM

其实 AXIALO. 4 就是 PCB 的默认库 ADVPCB. LIB 中的一只元件的名称。

- 2. 封装设定在 SCH 部分已介绍过,有一部分封装在库里面是找不到的,要你自己按照实物的尺寸来做一个 PCB 库。

- a. 在 SCH 的原理图中给所有电阻的封装都设定为 AXIALO. 4

如果逐一给各只电阻设定封装则比较费时,能否一次给所有电阻都设定封装为 AXIAL 0.4 呢? 这就要掌握一些技巧。

| Part                                                          |                                       |                                       |       | ? ×          |

|---------------------------------------------------------------|---------------------------------------|---------------------------------------|-------|--------------|

| Attributes   Graphical Attrs   Part Fields   Read-Only Fields |                                       |                                       |       |              |

|                                                               | Attributes To Match By Copy Attribute |                                       |       |              |

| Lib Ref                                                       | RES2                                  | Lib Ref                               | RES2  | 0            |

| Footprint                                                     | AXIAL0.4                              | Footorint                             | *     | AXIAL0.4     |

| Designato                                                     | 11R1                                  | Designati                             | *     | 0            |

| Part                                                          |                                       | Part                                  | *     | 0            |

| Sheet                                                         | *                                     | Sheet                                 | *     | 0            |

| Part                                                          | 1 _                                   | Part                                  | Any   | ☐ Part       |

| Selection [                                                   |                                       | Selection                             | Any   | ☐ Selection  |

| Hidden Pin <sup>[</sup>                                       |                                       | Hidden Pir                            | Any   | ☐ Hidden P   |

| Hidden Fiel                                                   | -                                     | Hidden Fie                            | Any   | ☐ Hidden Fie |

| Field Name                                                    | -                                     | Field Nam                             | e Any | ☐ Field Nar  |

| OK Help                                                       |                                       | Change Scope                          |       |              |

| Cancel << Local                                               |                                       | Change Matching Items In Current Docu |       |              |

在元件属性对话框中点击 GLOBAL, 在 LIB REF 中填入 RES2, 在 FOOTPRINT 填入 AXIALO. 4 确定,即可给所有库名为 RES2 的电阻都设定封装为 AXIALO. 4。

- b. 给无极性电容都设定封装为 RADO. 2. (方法与上类似. 略)

- c. 给有极性电容都设定封装为 RB. 1/. 2. (略)

- d. 给 NPN 三极管都设定封装为 NPN2. (略)

- e. 给变压器都设定封装为 ZZ. (略)

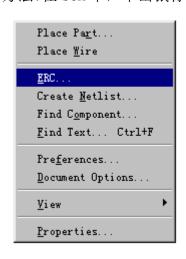

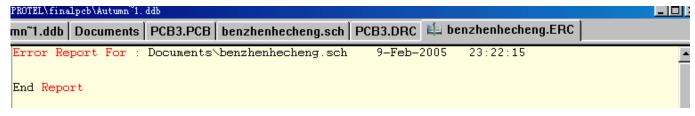

- 2. ERC 校正

方法:在 SCH 中,单击鼠标右键 — ERC... 在 SETUP ELECTRICAL RULE CHECK 中单击 OK。

右键对话框

#### ERC 对话框

#### 查看结果, 可以看到没有错误

#### 3. 错误列举

在这里列举最常见的二种错误:

a. #1 ERROR DUPLICATE DESIGATORS \*\*\*. SCH U? AT (620, 510) AND \*\*\*. SCH U? AT (379, 226)

电路图名

说明:这句子的意思是指元件序号名重复了,在这里出错原因是放置元件时没有填写序号而系统自动分配了U?为元件序号,所以多个元件也是如此时,则都使用了U?的元件序号,所以重命名了(其中(620,510)和(379,226)是重命名元件的位置。

解决方法:给元件分配序号就是了。

b. #2 FLOATING INPUT PINS ON NET NOO012 ◆ 节点号

说明:是输入节点悬浮,PROTEL对输入节点悬浮会给出出错提示,但我们知道,有时输出点是不需接任何东西的,这个错误如果不是人为接错,则不影响布线的。

解决方法:把 ERC 的 FLOATING INPUT PIN 项不选中,则不提示这种错误。

有一点要注意,当你有一个电阻接了一端,而另一端不接悬空时,PROTEL99SE 在默认的系统状态下是不报错误的,但该错误却直接导致 PCB 布线出错,所以需细心检查才行。

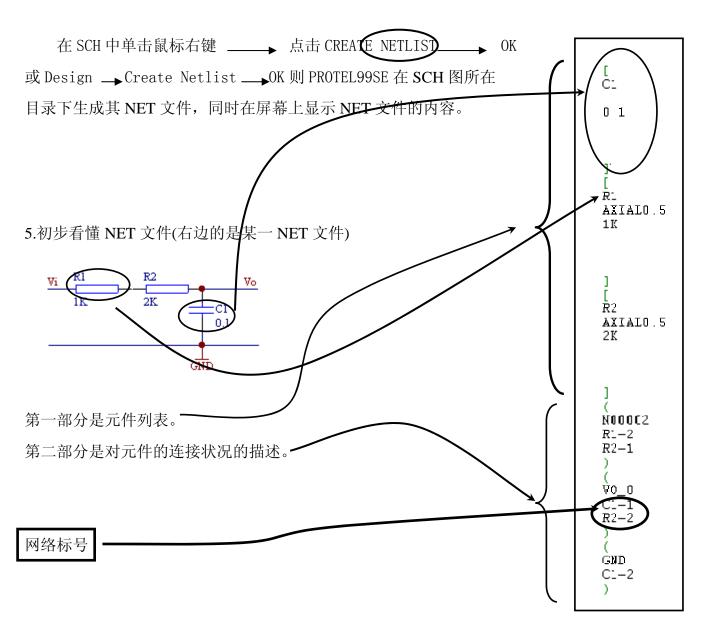

#### 큍 4. 生成 NET 文件

当你 ERC 校正无错时,就可以生成\*. NET 文件。 单击鼠标右键出现右图:

# 3-2 画电路板框

#### 1. 画出指定大小的电路板框

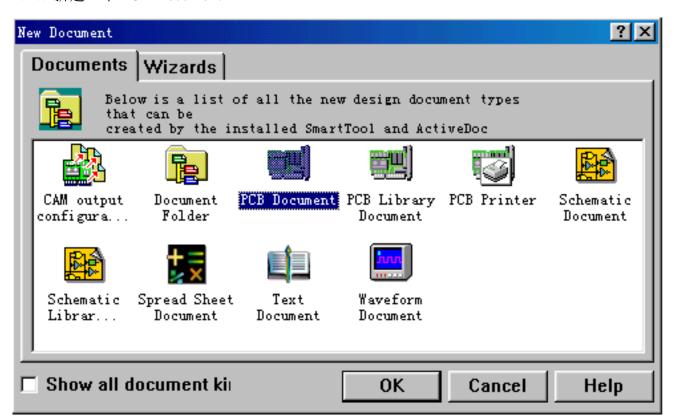

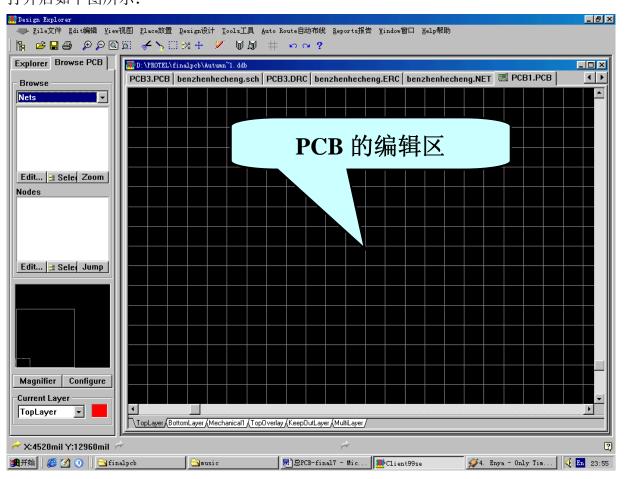

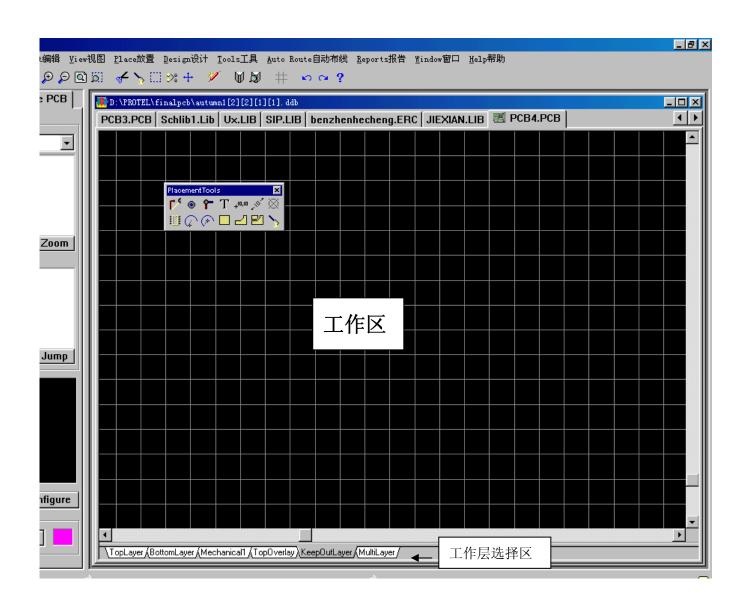

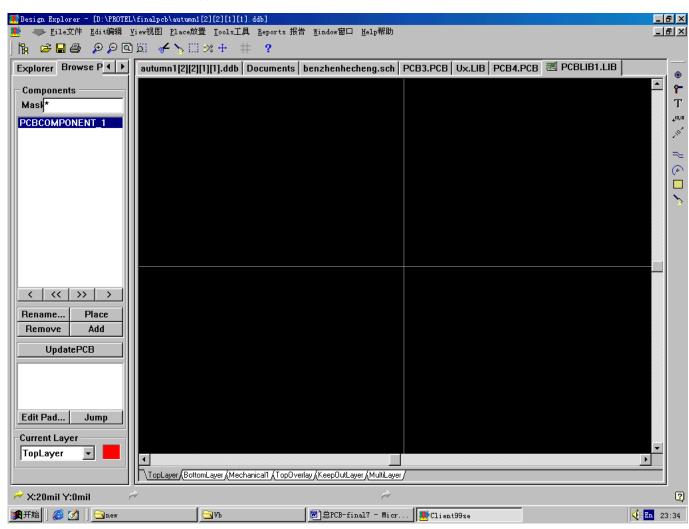

经过前面的各种准备后,SCH 的任务已暂时完成。现在该<u>启动 PCB 程序</u>了。 在 FILE \_\_\_\_\_ NEW 新建一个 PCB Document

#### 打开后如下图所示:

在 PCB 中的一般工作流程为:

由于所用元件封装有些是自己做的,所以在工作流程 [1], [2] 之间还要插入一个很重要的内容 \_\_\_\_\_ 自编辑元件封装,这在后面将详细讲述。

现在首先是画板,本实验做的板的尺寸为 13CM X 9CM, 而 PCB 工作区是用毫寸 (MIL) 为坐标的,要快速画出指定大小的电路板,有两种方法: A.鼠标法 B.键盘式。 下面分别介绍

A 鼠标法: 操作直观, 但不易准确控制尺寸

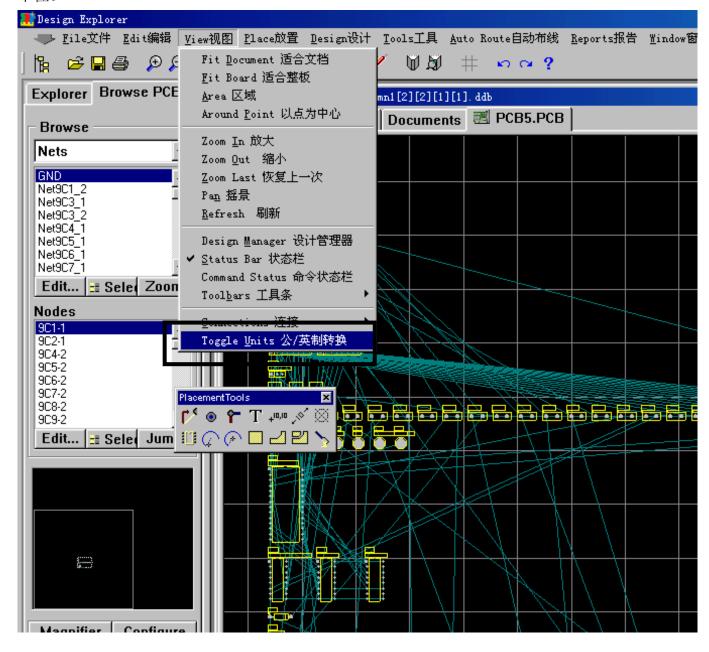

在画板前,首先把坐标单位转换为毫米 (MM),这样我们就不用将电路板块的尺寸转换为 MIL单位。

方法: VIEW 菜单 \_\_\_\_ TOGGLE UNITS) 或直接按 Q 键转换单位。

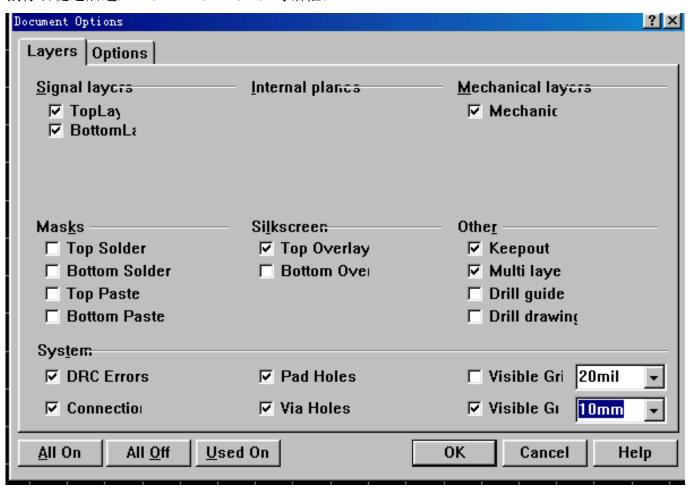

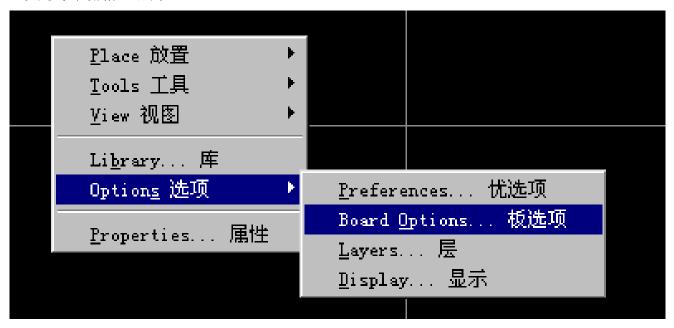

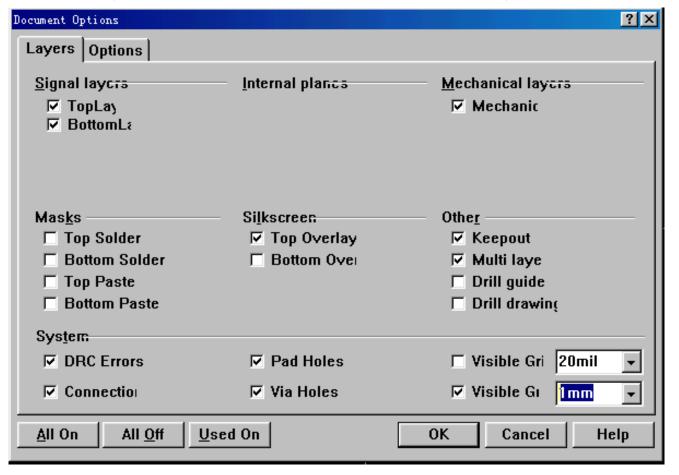

再把 PCB 编辑区的栅格大小设定为 1cm 每格,这样是最容易控制板块尺寸的。在 PCB 编辑区单击 鼠标右键之后进入 BOARD OPTIONS 对话框:

方法:在上面的对话框中前面打钩的 VISIBLE GRID (指定工作区正方形栅格边长)中填入 10mm。 点击 OK,这样就可使 PCB 编辑区以 mm 为坐标单位且栅格边长为 1cm。

实现这一点很重要, 否则你可能在尺寸转换中花去不少时间。

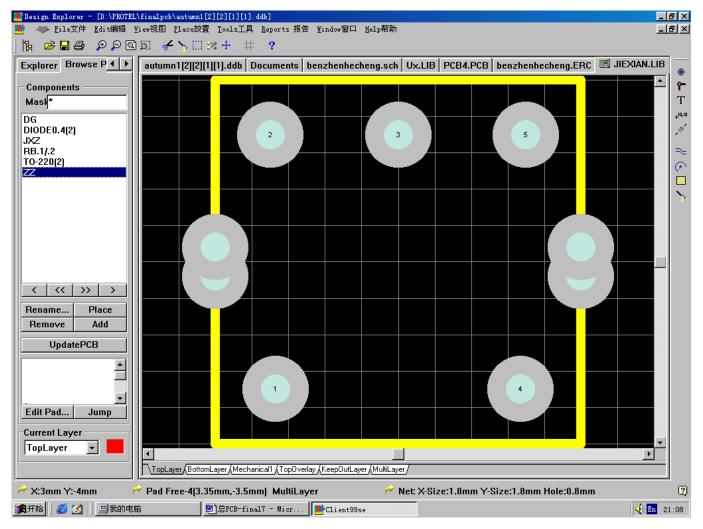

先切换到 KeepOutLayer 布线层,即禁止布线层。(不能用其它板层)

方法: 用鼠标在工作层选择区点击 KeepOutLayer 层,就能将当前工作区切换到 KeepOutLayer 禁止布线层。

# 现在开始画板

点击放置走线(Place Trace)

然后在编辑区任意位置双击确定电路板的左上角坐标,向下 13cm 即 13 格双击确定左下角坐标, 这样已画出电路板的左边。再向右 9cm 即 9 格画出下边,按上步骤画出一个 13cm X 9cm 的矩 形。该矩形是 PCB 板做出后的形状,元件和布线都将在这个矩形上做。这也叫设置禁止布线边框。 即布线不能超出矩形外。

**↑** T +0,0 × ⊗

但有一点必须注意,就是画最后一边时,必须与左上角的点闭合,闭合时会出现一个闭合圈。

(1) 按 J+A 跳到原点 B. 键盘法: (要点): (2) 按 J+L 跳到坐标......

### 3-3 装入\*.net 文件

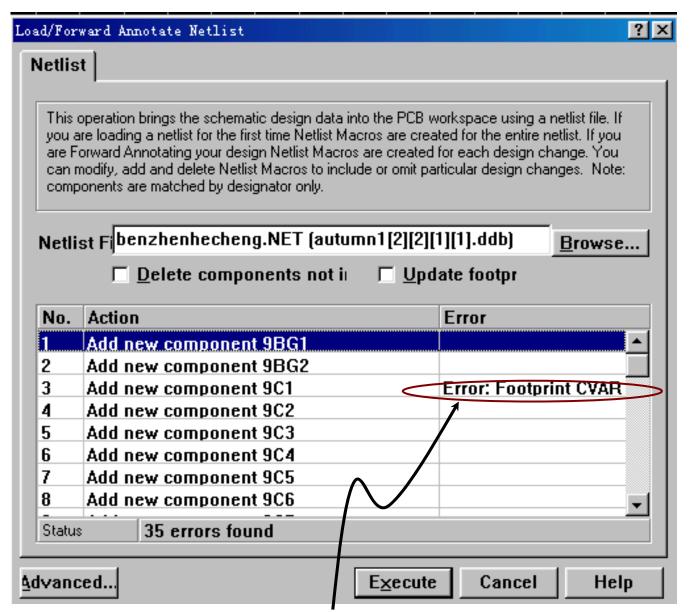

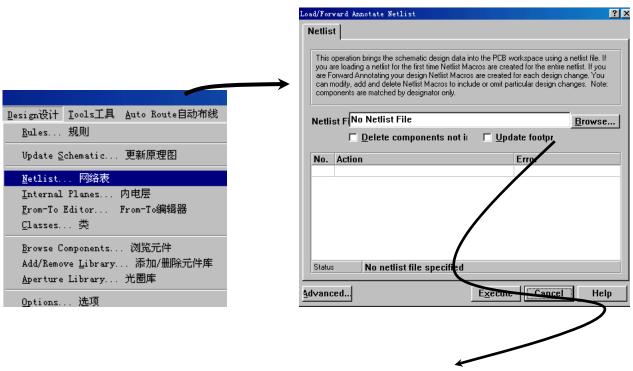

方法: 在 Design 菜单 \_\_\_\_ nelist... \_\_\_\_ Browse...(浏览) \_\_\_\_ 找出生成的 net 文件 \_\_\_\_

Exceute \_\_\_\_ OK

将 net 文件装入 PCB, 实际是将 sch 文件转化为 PCB 的宏命名, 在这里, 你会看到"×× ERROR FOUND", 怎会出现这么多错呢?

再看看其中出错提示: Error Footprint CVAR not found in library, 意思是元件 9C1 的封装 CVAR 在库中没有找到,还记得在 sch 中,这个可变电容的封装为 CVAR,元件的封装是自己编的,因为现在我还未把我的封装库调到 PCB 当前的库中,所以出现以上错误,而你还没有做好的话就不能调入了。现在我们就先编辑需要自己做的封装,再重新装入 net 文件。

# 3-4 编辑 PCB 元件

首先,点击 File New 在 Document 中新建一个 Pcb Library Document 文件

打开新建的 PCBLIB.LIB 文件,如下图所示:

再定义编辑区的每个栅格为 1mm。这里我习惯了每个格用 1 毫米,这样比较容易控制元件封装的尺寸大小。因为在实际测量的时候,用游标卡尺测得的数值都用毫米为单位。

a.将编辑区坐标由 mil 制改为 mm 制

方法: view 菜单 → toggleunits (按Q键)

这时你用鼠标在编辑区移动时,可看到状态栏的坐标变化单位为 mm。

b.设定每个栅格边长为 1mm。

#### Board options 对话框

这样就可将每个栅格边长设为 1mm 了。

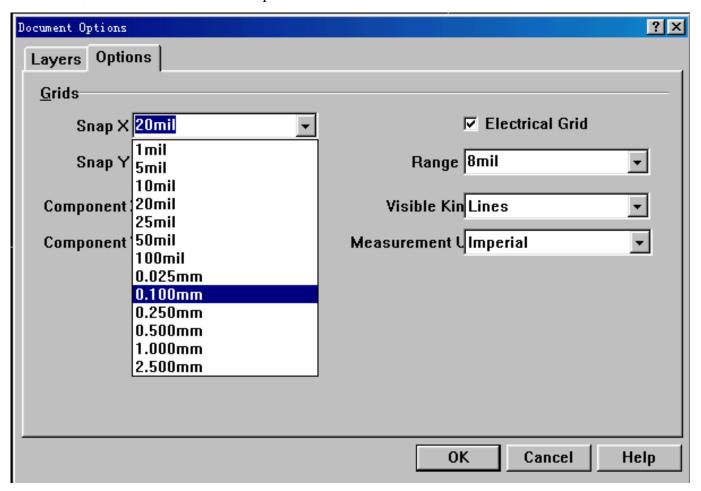

还有一个很重要的设置,在 Options 选项卡上,有两个选项 Snap X 和 Snap Y 它们是调整鼠标在编辑框里移动的最小距离,分别是 X 方向和 Y 方向上的移动距离,即分辨率。这里要根据所摆元件的尺寸数量级来确定所用的 Snap 值。,

#### 开始编辑元件

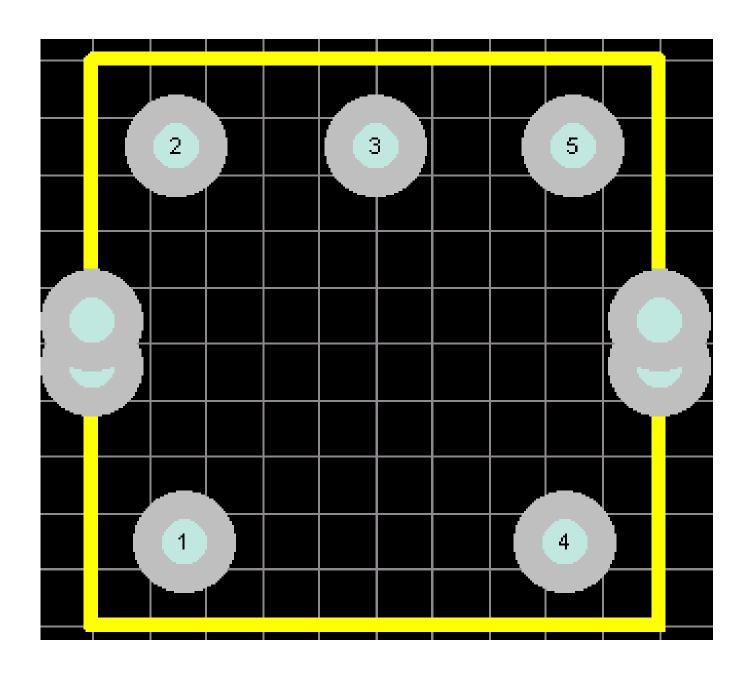

在这里只以一个变压器封装 ZZ 为例,其它元件的设计方法类似。

下图是编辑完成变压器封装 ZZ 的图形,它是按照实物的尺寸大小来制作的,要用游标卡尺精确量度,注意管脚的间距和引脚直径的大小。引脚(焊盘孔直径)的大小最好能留一些公差,即有可以松动的余地;而管脚间的距离就要比较精确了,否则可能整个元件都不能放进去了。还必须注意元器件的轮廓设计,元器件的外形轮廓一般放在 PCB 的丝印层上,要求与实际元器件的轮廓大小一致。如果元件的外形轮廓画得太大,则浪费了 PCB 的空间;如果画得太小,元件可能无法安装。

下面一步一步来学习怎样画出这个图形:

A. 先放置五个焊盘,注意焊盘间距,点击放置焊盘按钮)

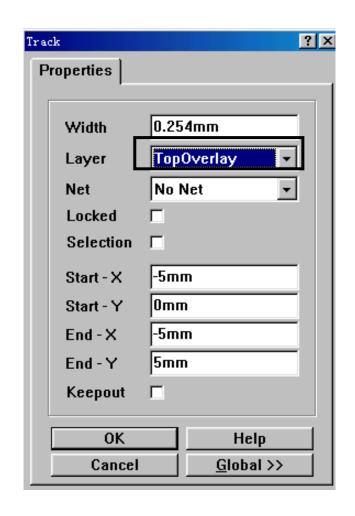

## B. 画轮廓线

按下 place track 按钮, 按照测量得到的元件外形数据,将外框画在五个焊盘的外边,并将所画的线的属性设置为在 TopOverlay 层上(后面回讲到),如下图所示。这里画轮廓线的准确度可以比焊盘间距和焊孔大小的准确度小些,因为外轮廓的大小主要是用来确定元器件在 PCB 板上占据的面积空间,即使是画大了,在调整位置的时候可以适当使元件有足够大的空间让它放上去就行了。而焊盘的放置就不同了,它直接影响着元器件能否插进 PCB 板从而进行焊接,所以焊盘的放置一定要谨慎些,太大太小都不好,应适当留有间隙,使元器件能插进焊孔中后又可以随意抽出。

- C. 设置焊盘,圆弧、走线的属性(重点)

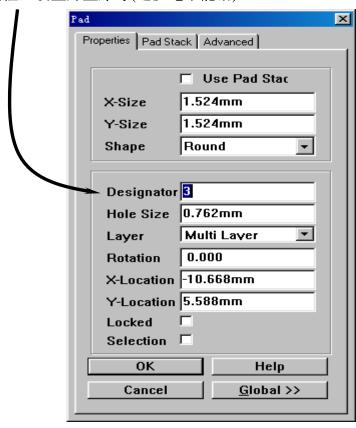

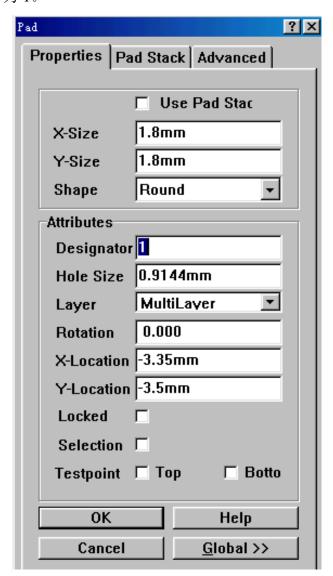

- a. 设置焊盘属性,设置焊盘序号(这步绝不能错)

PAD 属性对话框

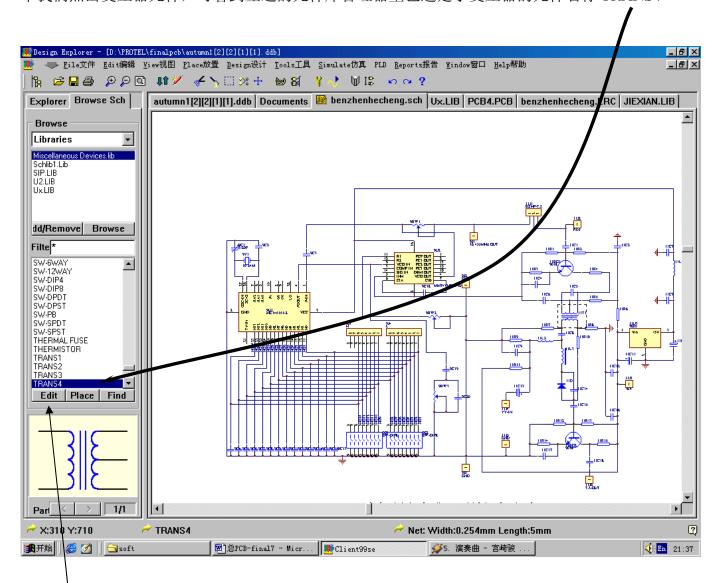

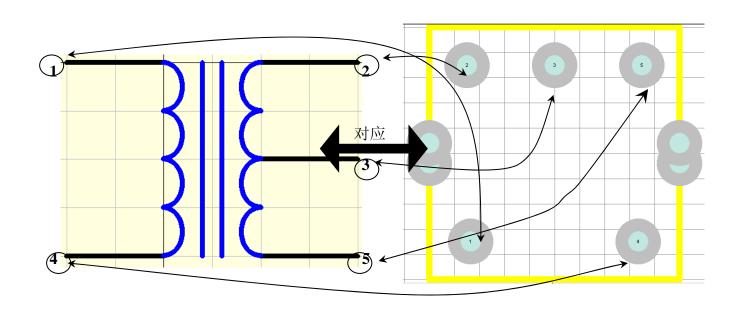

Tr 有五个焊盘, 怎知道哪个是 1 号, 哪个是 2 号···, 这就需要返回到 sch 中查一查了。在 SCH 中我们点击变压器元件, 可看到左边的元件库管理器里已选定了变压器的元件名称 TRANS4

按下 Edit 按钮就可打开它的 LIB 编辑画面如下图。可以看到引脚的定义在左边的管理器上的 Pins 框上。在编辑元件图上双击第一个引脚,得到它的属性框如下图所示。可看到 name 项和 number 项, name 为它的标号,而 number 则是它的焊盘序号,也就是 pins 号。上面做好的变压器封装图 ZZ 上已设置好它的焊盘序号,所以这里的 Number 号码必须和封装上的序号对应,这个脚对应封装图上左下脚的那个焊盘,序号为 1,其它的类似。全部设置好保存后就可以了(这里已不用改变了,因我的封装里焊盘的序号是按照元件图上的 Number 按顺序设置好的,所以不用改原图的序号)。

注意: 如果我的图和封装的焊盘序号不同,那就要改原图了。这样因为保存后这个改变了引脚电器特性的库文件覆盖了原来的那份,要用的时候就要改以下了,所以最好就用 SCH 部分的方法,在上面的库里新建一个元件,将图形复制到新建的元件里面,再改变它的引脚特性保存后再用,就更好了。

引脚对应图

从上面已经可确定 pcblib 中各焊盘的序号了。

将第 1 只焊盘设定焊盘 pad 的直径大小为 1.8mmn(X-Size 和 Y-Size),形状为 Round,焊孔 Hole Size 为 0.9144mm,设定 layer 为 Multi layer (焊盘所在的层,焊盘只能在这一层上),意思是焊盘为穿透多层板,设定序号为 1。

Pad 属性对话框

图中有 9 个焊盘,设定焊盘直径,形状及布线层 layer 的工作是相同的,只是序号不同。为了不重复 9 次,设置好 1 个焊盘后单击 global,再单击 ok,则 9 个焊盘都被设置为上述所示,但序号都为 1 了。然后再打开其它 pad 属性,修改序号就是了。4 个固定用的焊盘就不用设置序号了。

## b.设置(track)属性:

Track 的 layer 属性应为 Top Overlay。这是放置一些文字或图案的层,以便于安装与维修,这一层通常叫做顶层丝网层,也就是 Top Overlay。

TRACK 属性对话框

设置完成后可以看到 Track 由红色变为绿色,这是因为系统对不同板层的 Track 用不同的颜色表示。至此这个变压器的封装已差不多完成了,最后将它保存一下就行了。

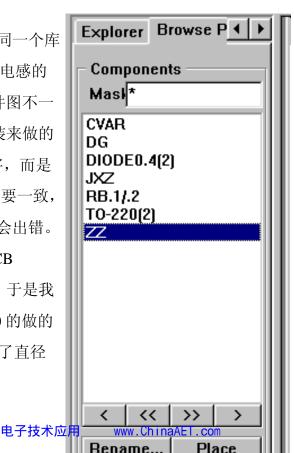

按以上方法同样可画出其它的元件封装,将它们放在同一个库里面如右图所示。CVAR 为变容器的封装,DG 是一个可变电感的封装,它和变压器的封装是一样的,因为在原理图上的元件图不一样所以要做两个。DIODE0.4(2)是按照 DIODE0.4 的封装来做的另一个封装,原来的封装 DIODE0.4 的焊盘的序号不是数字,而是A和 K,在原理图上的元件图的引脚命名是用1和2,它们要一致,要么都用A和 K,或都用1和2。否则在装入 NET 文件时会出错。JXZ 是接线柱的封装,RB.1/.2 是有极性电容的封装,在 PCB Footprint.lib 封装库里面,两脚的距离是 0.1 英寸的并没有,于是我做了一个。TO-220(2)是按 PCB Footprint.lib 库里 TO-220 的做的一个 7805 稳压器的封装,主要改变了它的焊孔大小,改成了直径 .9144mm,和上面的固定孔改成了直径 3.5mm。

做完上面的工作后,电路所需的封装都已经齐全。我们将刚才的封装另存为一个库 mypcb.lib。 在 Document 窗口里将刚才新建的 PCBLIB.LIB 文件,右键将它 Rename 为 mypcb.lib 就行了。

## 3-5 再装入 net 文件

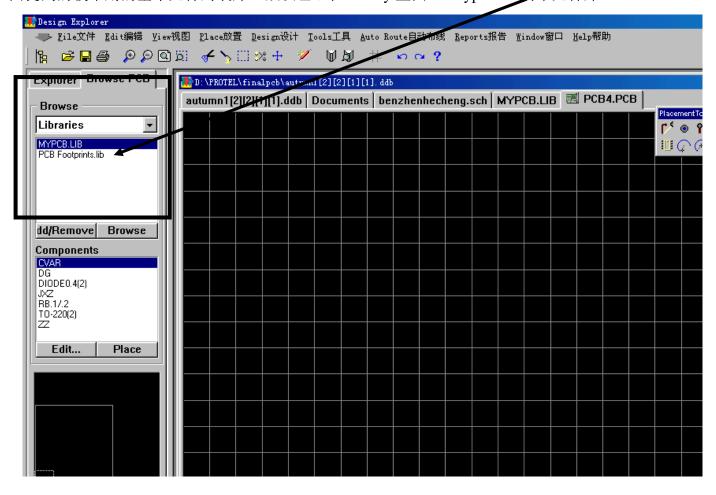

现在所需封装都齐全了,在 pcb 的元件库管理器的 Browse 框中同时装入 PCB Footprint.lib(上面提到的较常用的基本元件封装库,默认已经在 library 里面),mypcb.lib 两个元件库

方法: 单击 Add/Remove → 找出 mypcb.lib 单击 add → OK

这两个库任一个作为当前库都可以,因为在调入 NET 文件时,系统会按照 SCH 中各元件属性中所指定的封装名,在 PCB 所调入的库(而不只是当前库)中扫描,当封装名与元件名相同时,就转化为宏命令,如: add new component ZZ, ZZ 是元件名(封装名),那么 ZZ 就由 SCH 中调进了 PCB, 若在调入的元件库中找不到相匹配的元件,就出错提示,如: Error: Footprint ZZ not found in library。

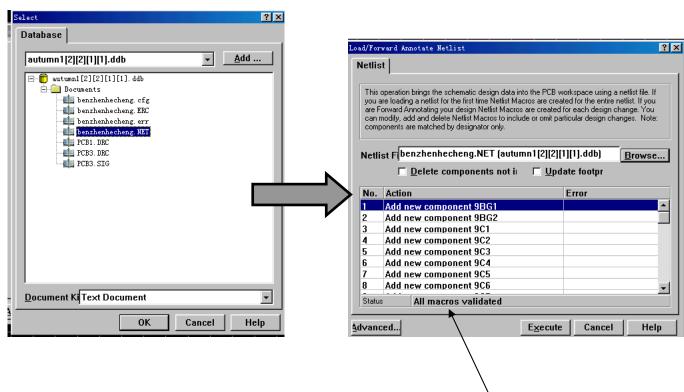

现在按前述方法再调入刚才生成的 NET 文件。

方法: Design 菜单 → Netlist → 点击 Browse 找出刚才的 NET 文件后双击它,如下图所示:

可以看到,网表宏转化框(netlist macros)的状态(status)中为 All macro validated,意思为所有宏有效,即 SCH 原理图中所有的元件及节点都已成功转化为宏命名供 PCB 使用了。最后点击 Execute就可将网络表文件中的元件调到当前印制电路板中。如果出现了错误,就要看错误的表述,认真查错。先看是否装入了所必需的 LIB 文件,元件的封装是否做好。原理图的 ERC 检测是否有错,有就要先改正。象上面的分析方法来解决问题,最后使出现的错误为 0,然后才 Execute。由于错误很多,需要根据实际情况来判断改正。这里就不多说了。

# 3-6、布局

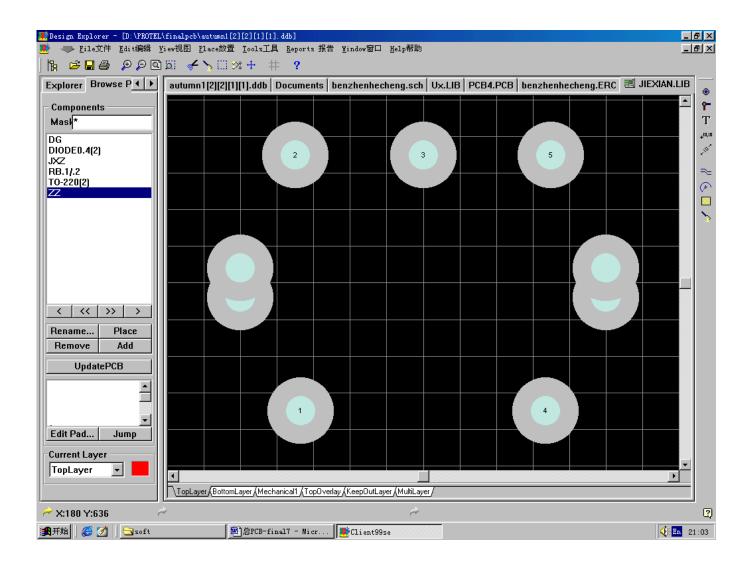

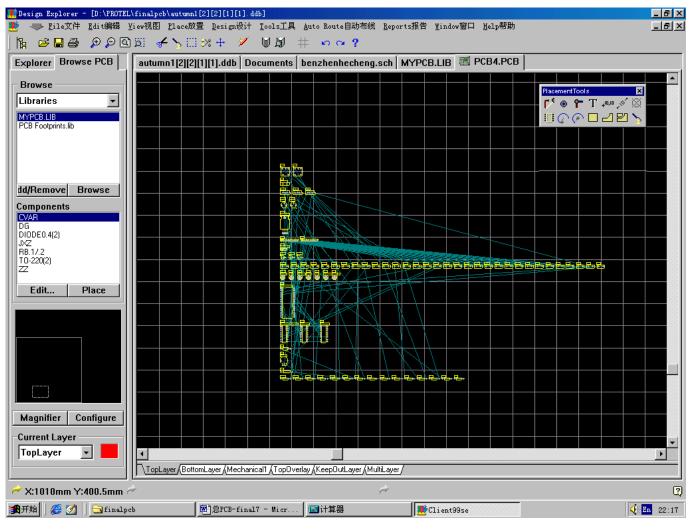

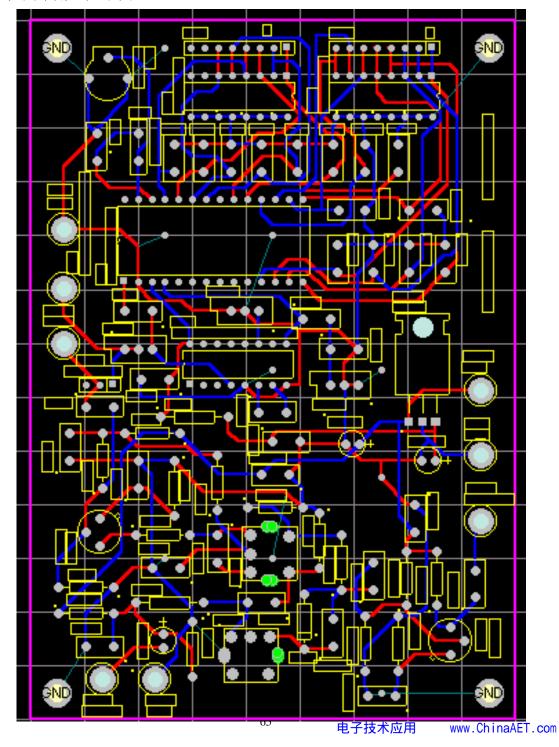

按了 Execute 调出元件后, 会看到很多元件整齐地排在一起, 如下图所示:

Protel99 可以进行自动布局,也可以进行手动布局。我在布局的时候先是按照原来实验板的摆位来布局元件的,然后进行手工调整。

#### 先设置元件布局参数:

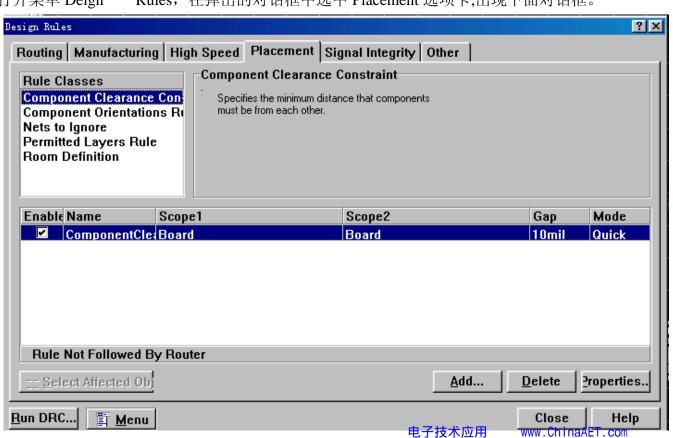

打开菜单 Deign → Rules,在弹出的对话框中选中 Placement 选项卡,出现下面对话框。

## 各参数的含义是:

Component Clearance Constraint: 设置元件之间的最小间距。

Component Orientations Rule: 设置元件放置的方向。

Nets to Ignore: 设置在采用分组形式进行自动布局时应忽略的网络。

Permitted Layers Rule: 设置允许放置元件的层面。

Room Definition: 设置限定或排斥某些特定对象的矩形区域的范围。

各项一般选择默认就行。

注意: 布局时要把元件都放在刚才在 KeepOutLayer 层上画好的禁止布线框里面。否则就不能进行自动布线了。(只要最后将要进行布线时元器件都在框里就行)

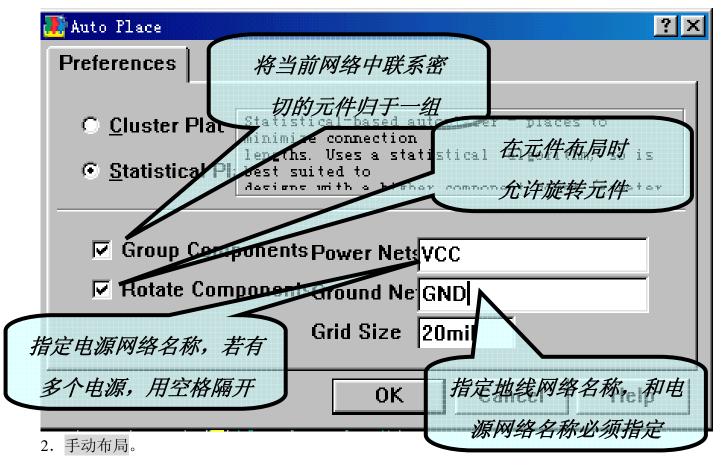

## 1. 自动布局,

选择菜单 Tools → Auto Placement → Auto Placer,通常设置成以下形式,按下 OK 就可以自动布局。这样做好后还要用手工进行调整以符合电路的电器特性,和走线的规则设定。

我没有用自动布局,先是按照实验板的本振频率合成电路布局,后借鉴话放调相的电路板来重新布局,然后再将两个电路重新安排位置,零件布局,应当从机械结构散热、电磁干扰、将来布线的方便性等方面综合考虑。先布置与机械尺寸有关的器件,并锁定这些器件,然后是大的占位置的器件和电路的核心元件,再是外围的小元件。最好能把电路分成不同的工作部分,如这个电路是由本振频率合成电路和话放调相电路组成,而本振频率合成电路可分为外部晶振部分,分频、鉴相、参考分频部分,VCO部分等。话放调相电路可分为,前置放大部分,调相部分,话音输入部分,输

出放大部分。将各个部分的元件组合好,再把各部分按照机械结构、电磁干扰、布线方便简洁等因 素摆好方位。完成布局。

你需要有足够的耐心。布线的关键是布局,多数设计者采用手动布局的形式。用鼠标选中一个元件,按住鼠标左键不放,拖住这个元件到达目的地,放开左键,将该元件固定。Protel99 在布局方面新增加了一些技巧。新的交互式布局选项包含自动选择和自动对齐。使用自动选择方式可以很快地收集相似封装的元件,然后旋转、展开和整理成组,就可以移动到板上所需位置上了。当简易的布局完成后,使用自动对齐方式整齐地展开或缩紧一组封装相似的元件。

提示:在自动选择时,使用 Shift+X 或 Y 和 Ctrl+X 或 Y 可展开和缩紧选定组件的 X、Y 方向。在选择元件时看不到元件的编号和标值时用 PageUp 和 PageDown 键放大缩小,当放大到一定程度时就能看到了。

# 3-7 布线规则

布线有自动布线和手工布线,在电路原理图复杂的情况下,如果使用手工布线,不仅效率低,难度也很大,这时可以充分利用 Protel99se 强大的自动布线功能。本实验板的设计主要是以自动布线为主,手工布线为辅。自动布线毕竟不能完全正确,所以还需要人来检查线路,以改正错的地方。1. 布线规则:

无论自动布线还是手工布线都要先设置布线规则。由于高频电路工作频率高,高抗干扰性的影响就较其它电路大,要考虑的因素就较多,所以高频电路有较高的布线要求,要设定较多的布线规则。

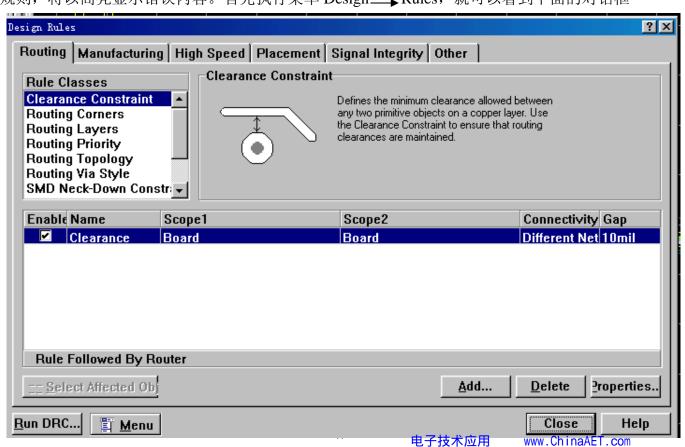

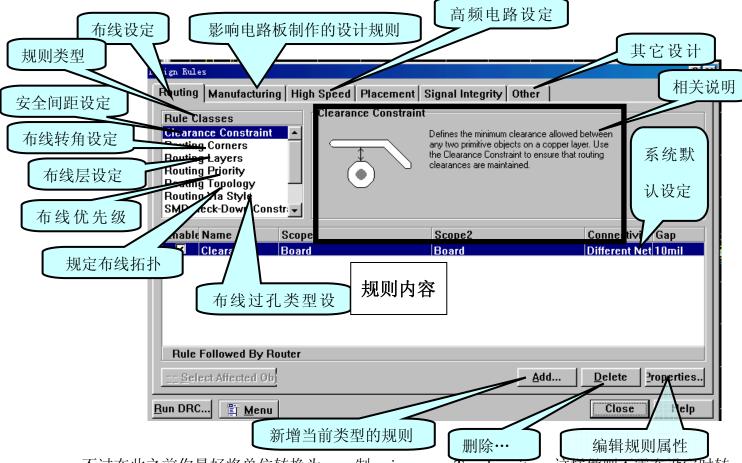

设计规则制定后,程序自动监视 PCB,检查 PCB 中的图件是否符合设计规则,若违反了设计规则,将以高亮显示错误内容。首先执行菜单 Design → Rules,就可以看到下面的对话框

对话框共有六个选项卡,分别设定与布线、制造、高速线路、元件自动布置、信号分析及其它方面有关的设计规则。

下面就介绍设计规则, protel 99 的设计规则很细致,这正是 protel 99 的优势所在。在这里不可能面面俱全,只介绍与本印制板有关的几项设定。

不过在此之前你最好将单位转换为 mm 制: view \_\_\_ Toggle units 。这样做则不需在设定时转换单位了。下面来介绍几个较常用的设置:

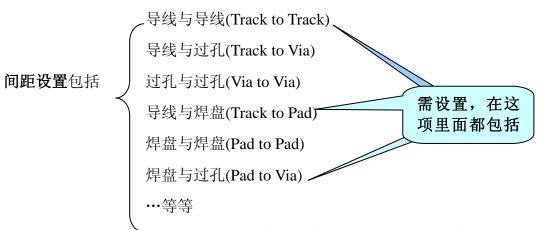

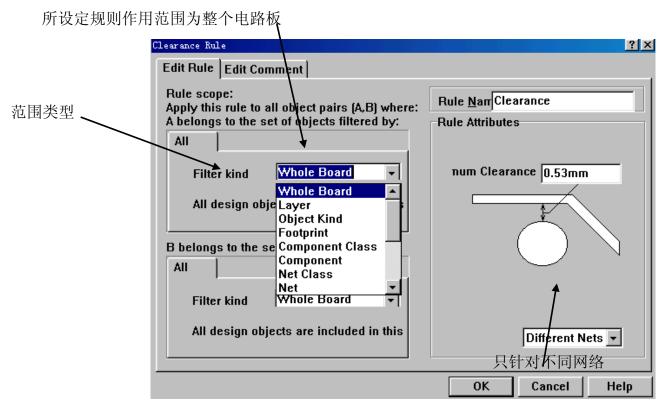

## Clearance Constraint 安全间距设置

双击 Clearance Constraint 就可以添加规则,双击规则内容,就可以修改规则,都出现下面的对话框。

它规定了板上不同网络的走线焊盘过孔等之间必须保持的距离。一般板子可设为 0.254mm,

较空的板子可设为 0.3mm, 较密的贴片板子可设为 0.2-0.22mm, 极少数印板加工厂家的生产能力在 0.1-0.15mm, 假如能征得他们同意你就能设成此值。0.1mm 以下是绝对禁止的。

在这里设 Track to Pad 的 minimum clearance(最小间距)为 0.53mm。其实还有很多选项,而且有的很复杂,有的需在 sch 中进行一些定义才能用,在这里你只要按下图设定即可,不再展开讨论。

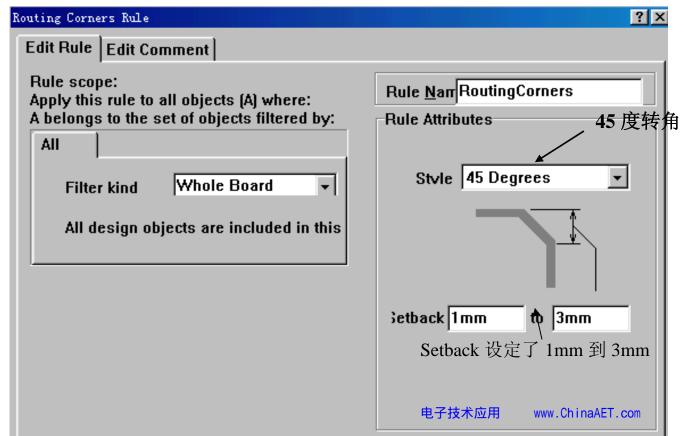

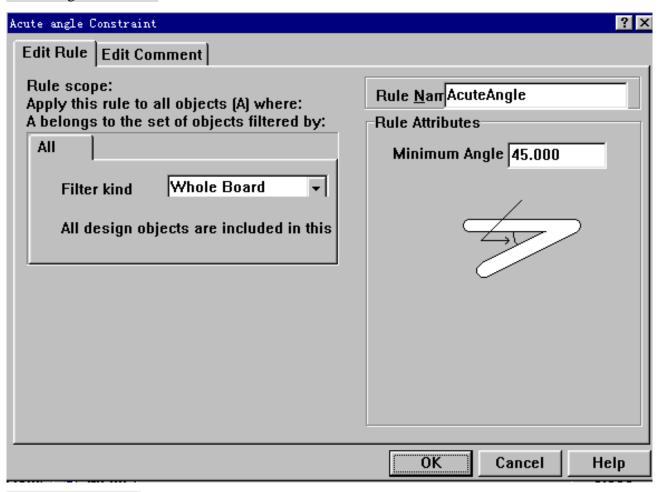

Routing Corners 设定 Track 的转角方式,高速电路器件管脚间的引线弯折越少越好。高频电路布线的引线最好采用全直线,需要转折,可用 45 度折线或圆弧转折,这种要求在低频电路中仅仅用于提高钢箔的固着强度,而在高频电路中,满足这一要求却可以减少高频信号对外的发射和相互间的耦合。注意设定的是最小转角,如果是 45 度的话,还要设定转角的高度范围 setback。

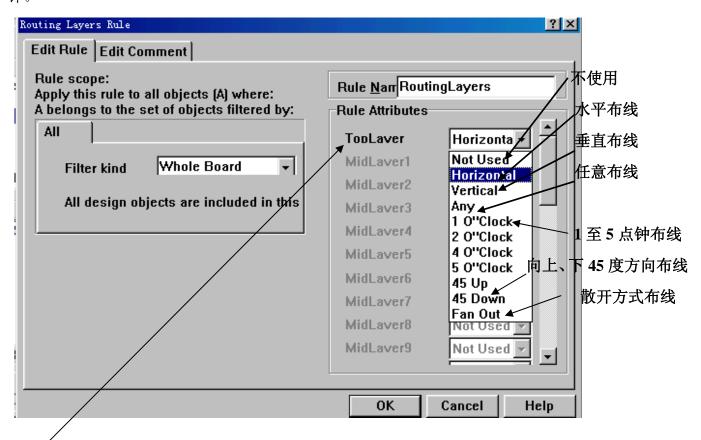

Routing layers 高频电路往往集成度较高,布线密度大,采用多层板既是布线所必须的,也是降低干扰的有效手段。合理选择层数能大幅度降低印板尺寸,能充分利用中间层来设置屏蔽,能更好地实现就近接地,能有效地降低寄生电感,能有效缩短信号的传输长度,能大幅度地降低信号间的交叉干扰等等,所有这些都对高频电路的可靠工作有利。有资料显示,同种材料时,四层板要比双面板的噪声低 20dB。但是,板层数越高,制造工艺越复杂,成本越高。在这里我们用了双层板设计。

板层名,TopLayer 为顶层,BottomLayer 为底层,1~30 为中间层

把 TopLayer 层设为 Horizontal 水平布线,BottomLayer 层设为 Vertical 垂直布线即可,同一层内的平行走线无法避免,但这是双层板,这样设置符合在高频电路布线中最好在相邻层分别取水平和竖直布线交替进行的约定。

Routing priority 略,按默认即可。

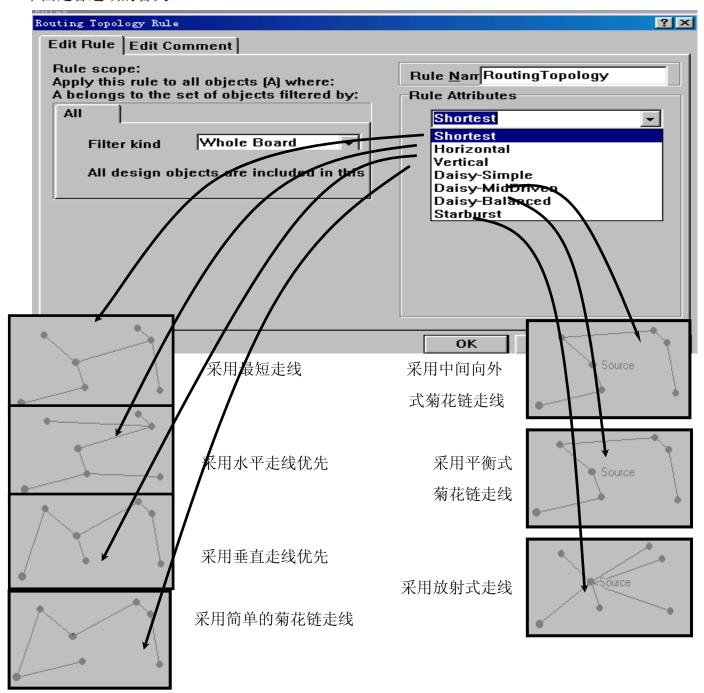

### Routing Topology 本选项设定走线的拓扑。

高频电路器件管脚间的引线越短越好。所以我用了 Shortest 走线。但各类信号走线不能形成环路,地线也不能形成电流环路。Prote199 自动布线的走线原则除了前面所讲的最短化原则外,还有基于 X 方向、基于 Y 方向和菊花状(daisy)走线方式,采用菊花状走线能有效避免布线时形成环路。所以应以电路的具体情况来决定使用哪一种走线方式。

## Routing Via Style 过孔形状

它规定了手工和自动布线时自动产生的过孔的内、外径,均分为最小、最大和首选值,其中首选值是最重要的,这里我用默认值。

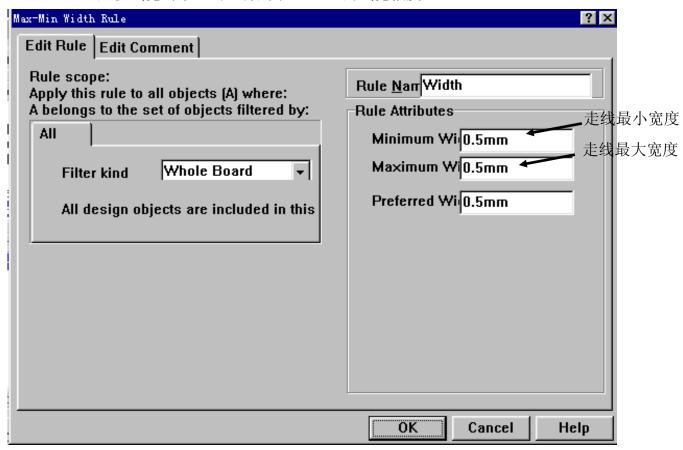

#### Width Constraint 本选项设定线宽

它规定了手工和自动布线时走线的宽度。整个板范围的首选项一般取 0.2-0.6mm,另添加一些 网络或网络组(Net Class)的线宽设置,如地线、+5 伏电源线、交流电源输入线、功率输出线和 电源组等。网络组可以事先在 Design-Netlist Manager 中定义好,地线一般可选 1mm 宽度,各种电源线一般可选 0.5-1mm 宽度,印板上线宽和电流的关系大约是每毫米线宽允许通过 1 安培的电流,具体可参看有关资料。其中 Whole Board 为对整个板的线宽约束,它的优先级最低,即布线时首 先满足网络和网络组等的线宽约束条件。考虑到本试验板的电流不大和为了布线方便,我用了

Whole Board 整板线宽约束,而且都用了 0.5mm 的线宽幅度。

\* Manufacturing 影响电路板制作的设计规则

这里只介绍几个:

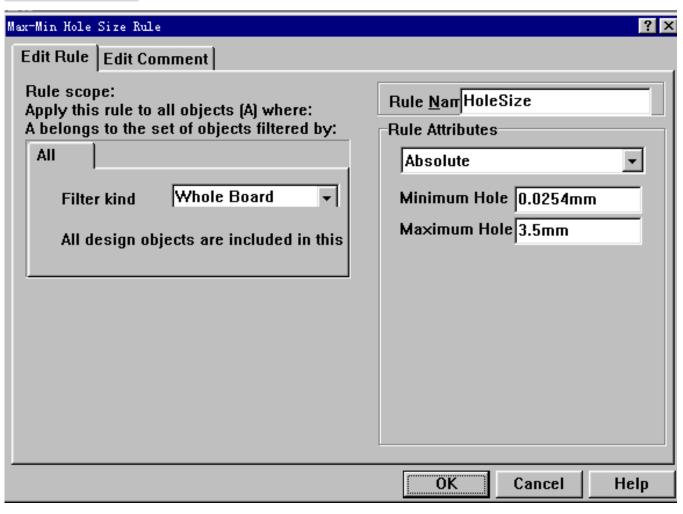

Hole Size Constraint 孔的大小设置

这是设置板上的锡盘孔和过孔大小的设置项,可以限定孔的最大和最小直径。这里我只设置了最大值 3.5mm。高频电路器件管脚间的引线层间交替越少越好。所谓"引线的层间交替越少越好"是指元件连接过程中所用的过孔(Via)越少越好,据测,一个过孔可带来约 0.5 pF 的分布电容,减少过孔数能显著提高速度。

## Polygon Connect Style 敷铜连接形状的设置

建议用 Relief Connect 方式导线宽度 Conductor Width 取 0.3-0.5mm 4 根导线 45 或 90 度。

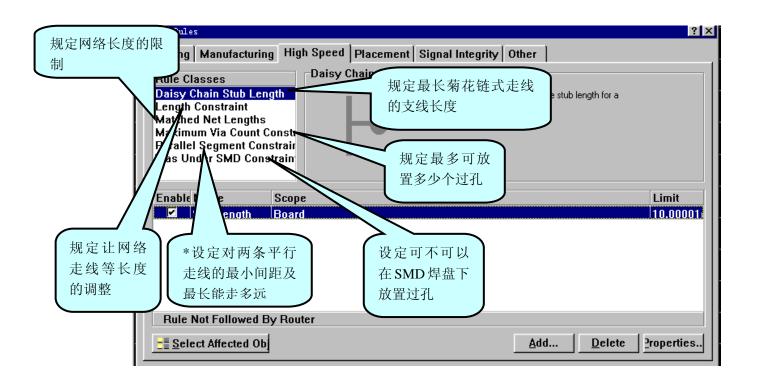

**High Speed** 这里就是高频电路相关的设计规则,虽然实验板由于体积大,而对该项要求不太严,但作为高频电路课程设计,在这里有必要详细讲述。

高频电路泛指工作频率在 1MHZ 以上的电路,但这样定义的电路类型太广泛了,例如高速数字电路,即属于数字电路,又属于高频电路,所以高频电路的一些技术,同样适用于数字电路。

印制导线工作在较高频率的情况下,它的电阻值、电感量、及分布电容等不能被忽视。

## A.电阻的变化

低频时,导线电阻一般很小,可以忽略,但在高频时,由于趋肤效应,像厘米波电流流过导线时,导线的中心就几乎没有电流流过,这样一来电流流过导体的有效面积大为减小。在这里给出一条公式:

$$R_f/R = 0.107 \sqrt{f}$$

高频时电阻(Rf) 直流电阻(R) 工作频率(f)

## B.电感的变化

L= 2l( ln 2l/w+t +1/2) (nH) (w>>t)

高频时导线的电感量(L) 线长(l) 线宽(w) 线厚度(t)

由以上公式可知, t 是确定的, 所以主要影响为 w 和 l, 尽可能缩短印制导线的长度或增加其宽度, 可有效减少高频带来的电感量。

C. 电容的变化: 电感随着频率的增加, 其特性可以从感性变到容性。

由以上分析知道, 高频电路须合理设置布线参数, 尽可能减小高频带来的额外性能开消。

以下是 High Speed 里面各项的简单说明:

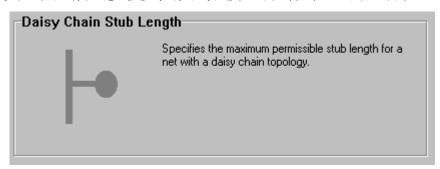

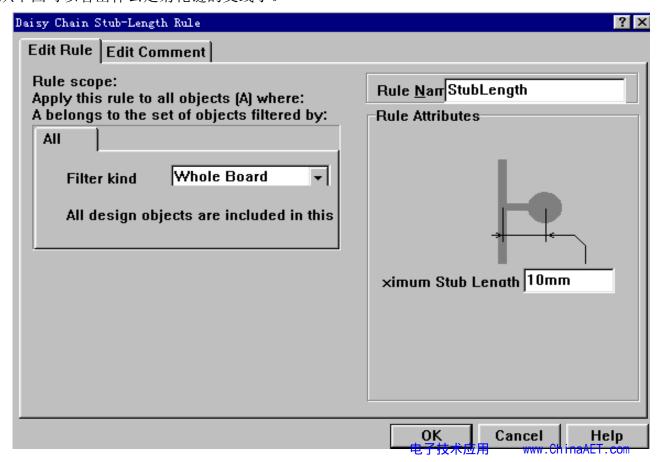

## Daisy chain stab-length Rule

本项规定布线时,最长菊花链式走线的支线长度,可以看到右边的区域中,也配合有简单的说明。

从下图可以看出什么是菊花链的支线了。

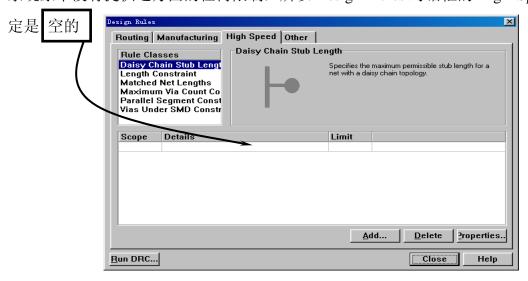

系统原本没有提供这方面的任何限制,所以 Design Rules 对话框的 High Speed 选项卡下该项的设

单击 add…新增规则,可以看到系统已预设支线最大长度为 10mm,但在这里我们无须规定支线长度。

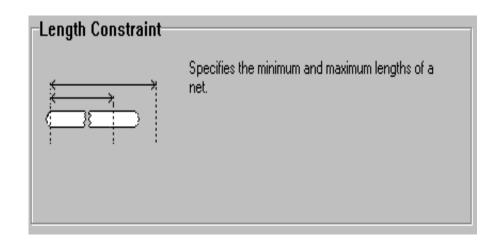

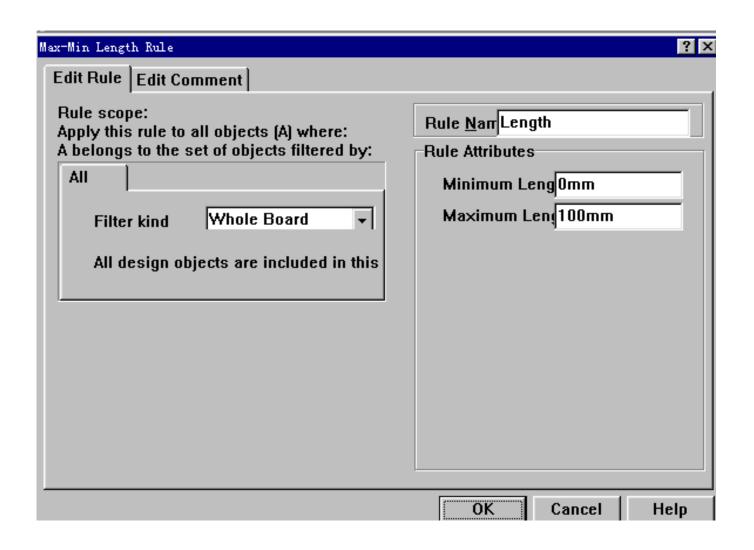

## Lenth constraint

本项规定网络的长度限制,网络长度是指走线的长度,下图是相关的说明:

就是设置一个网络连接最小和最大的长度。

单击 add…可新增规则,

默认系统预置值最小为 0cm, 最大为 25.4cm。

若不更改就单击 ok,下图是我的设置。在高频电路里面,走线的长度尽量设置得短一些,以减少高频干扰和走线与走线之间的电容效应。

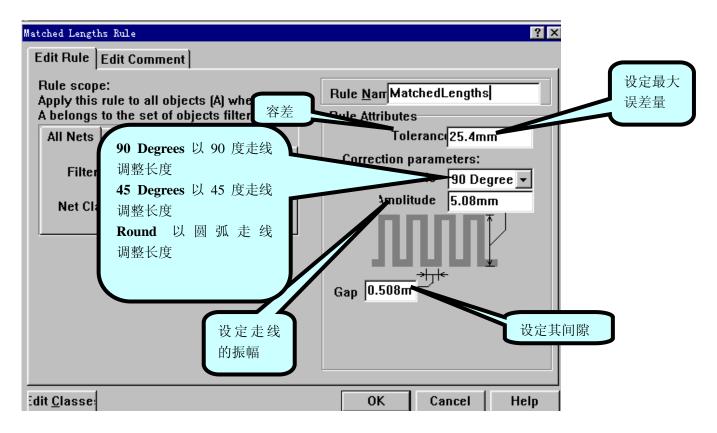

## Matched Net Lengths

本项规定让网络作走线等长度的调整,同样也有相关的说明

与前面几项一样,系统原本没有提供这方面的任何限制,单击 add···可新增规则,如下图:

本项的设定较为重要,因为频率较高下,径直的走线就容易辐射电糍波,同时本身又作为电磁波的接收天线,不但干扰外电路,又被外电路干扰,所以限制其长度可以减小高频对电路性能的影响。由于本实验的线路还没有须要用到设置这项,所以在这里可以不设定。

#### Maximum Via Count constraint

本项设定最多过孔的数目,这块实验板在顶层和底层都大面积敷铜,所以过孔所造成的分布电容 不是很大。这里就没有设定了。

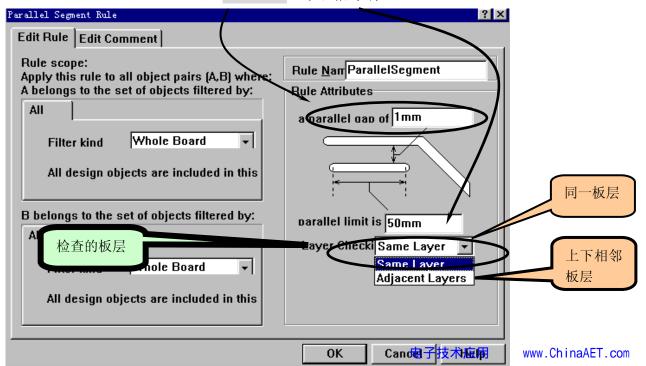

## Parallel Segment Constraint

本项设定对于两条平行走线的最小间距及最长能平行走多远

高频电路布线要注意信号线近距离平行走线所引入的"交叉干扰"。所以要设定平行线之间的最小间距和走的最长距离。也可在平行信号线的反面布置大面积"地"来大幅度减少干扰,这个电路板的设计就用到了。

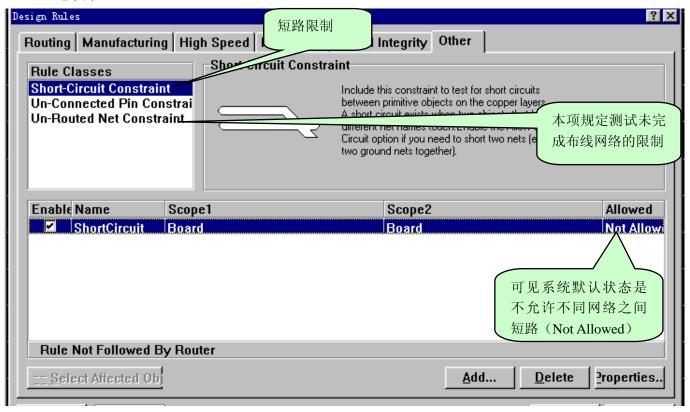

## Other 选项卡

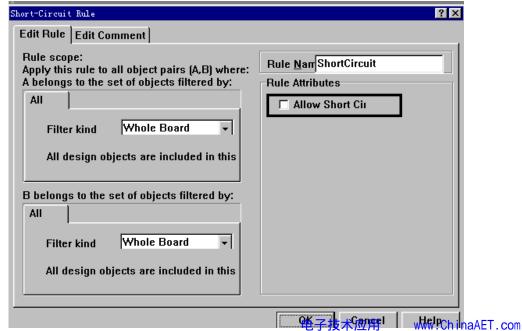

#### Short-circuit constraint

本项规定允许短路,或许你认为哪有可能"短路"!如果我们完成电路板设计后,猛然发现 CMOS 及 TTL 的电源引脚并没有相连。因为 CMOS 的电源引脚属于 VDD 网络,而 TTL 的电源引脚属于 VCC 网络,虽然我们认为它们应该相连接,但如果将"分属不同网络的走线连接就是短路",所以程序不会为它们连接,就算我们以手工强制连接两条网络,也无法连接。但设定本项后,就可连接了。

到此,布线规则已花了很大篇幅简介了一遍,你可能会问,很多都与本实验板无关的,但因为 PCB 的强大优势就在其众多的布线规则的设定,在这里也只能抛砖引玉地让你了解一下,真正地 掌握还有待参考有关书藉及亲自动手试验。

# 3-8 自动布线

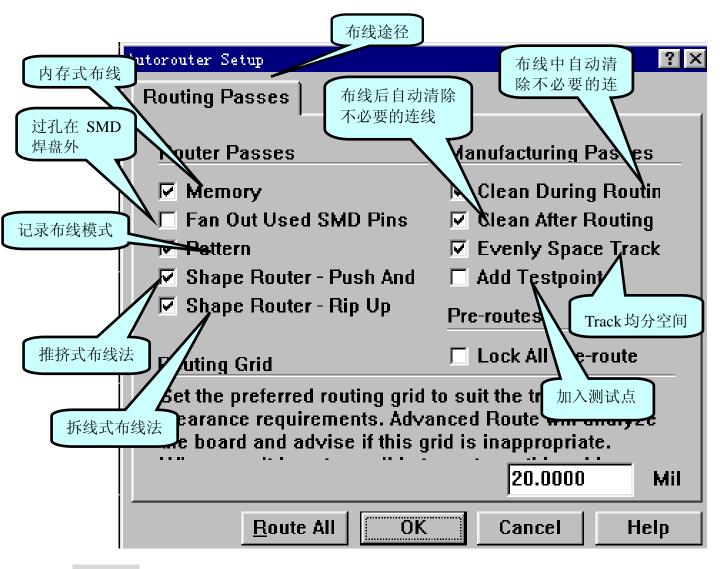

## 1、点击菜单命令 Auto Route/Setup 对自动布线功能进行设置

选中除了 Add Testpoints 以外的所有项,选中其中的 Lock All Pre-Route 选项,可以锁定元件以免不小心改了

## memory

本选项设定采用内存式布线程序,什么是内存式布线程序? 那我们看看内存 IC,以 6264 为例,内存 IC 不外乎好几只地址引脚,好几只数据引脚,相同地址的引脚接在一起,相同数据的引脚也接在一起,所以就形成规则的走线模式,这种规则是波浪状走线,这就是内存式布线程序。本振频率合成电路用到了两个 IC (MC145151-2 和 MMVHC4046N(16))。所以把它选中就是了。

#### Fan out used Smd pins

不选,看字面就知与Smd(表面粘贴)元件有关,这里没有SMD元件,所以不选。

#### Pattern1

本布线程序是将好的布线模式记录下来,布其它网络时,可节省时间。

## Shape Router Push and Shove

选,采用推挤式布线法:(略)

## Shape Router --- Rip up

选,采用拆法式布线法:(略)

## Evenly Space Tracks (evenly: 平均)

选,本选项的功能是设定如果在两焊盘间设定可布两条导线时,第一条走线会先偏向一边,留较大空间给第二条走线。如果第二条导线无法通过,或根本不须要通过第二条走线时,则第一条走线将以两 pad 的中点为中心移动,不再偏向一边。如果第二条走线能顺利通过,则两条线将在两焊盘间平分空间

## **Routing Grid**

Routing Grid 是布线的解析度,可选 1mil 等。自动布线开始前 PROTEL 会给你一个推荐值可不去理它或改为它的推荐值,此值越小板越容易 100%布通越小,但布线难度和所花时间越大。大可照用它的推荐值。

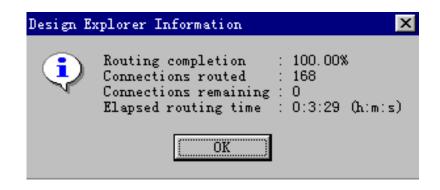

假如不能完全布通则可手工继续完成或 UNDO 一次(或用撤消全部布线功能 Tools→Un-Route→ All,但它会删除所有的预布线和自由焊盘、过孔)后调整一下布局或布线规则,再重新布线。通常都能一次布线通过(这是因为 Protel99SE 的布通率很高,也是我的经验)。布线通过后,布线信息报告如下图所示:

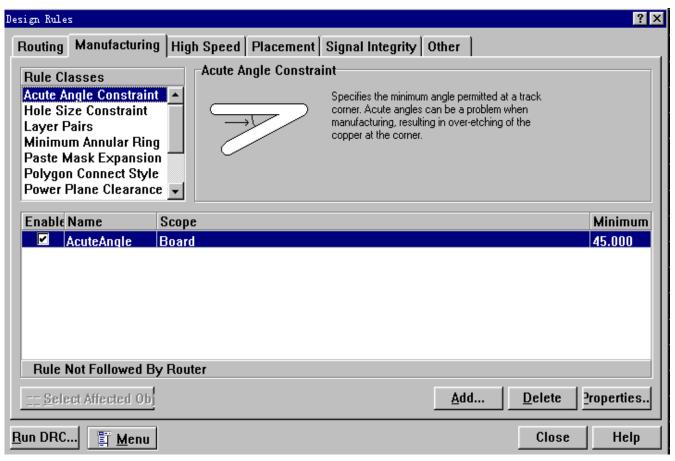

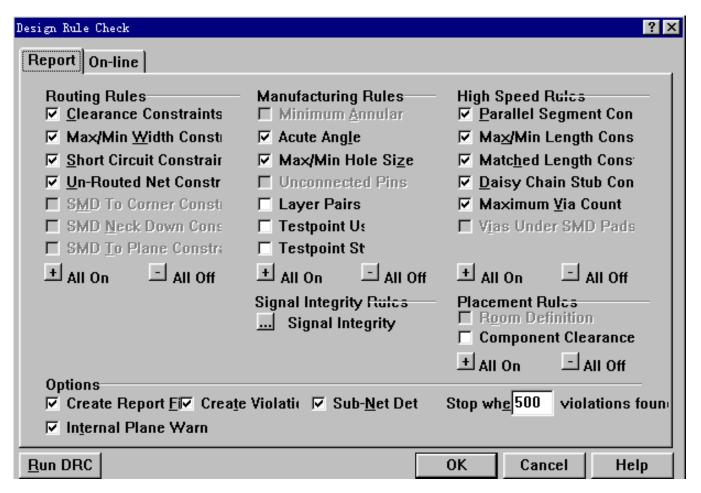

完成后执行菜单 Tools \_\_\_Design Rules Check,有错则改正。Design Rule Check 简称 DRC 检测,用户可以用这项设计规则检查功能对完成布线的印制电路板进行检查,确定布线是否正确、是否符合已设定的设计规则。执行 Design Rules Check 后出现以下对话框:

Routing Rules、Manufacturing Rules 和 High Speed Rules 三栏分别列出了与布线、制作及高速电路 有关的规则,若需要利用某个规则作检查,则选取相应的复选框。在上面有设定的 Rules 才会在 DRC 的检查报告中出现。这里主要选中以下几个常用的选项就行了。

Clearance Constraints: 安全间距监测。

Max/Min Width Constraints: 导线宽度检查。

Short Circuit Constraints: 短路检查。

Un—Routed Net Constraints: 未布线网络检查。

通常选择默认值就行了。按下 Run DRC 按钮,就开始进行 DRC 检查,检查完毕后,将给出一个检查报告。如下图

```

Processing Rule: Parallel Segment Constraint (Gap=1mm) (Limit=50mm) (On the board), (On the

Rule Violations : 0

(违规数: 0)

(平行走线限制)

Processing Rule : Length Constraint (Min=Omm) (Max=100mm) (On the board )

Net GND Actual Length = 565.91962mm

Violation

Net Net11R11_1 Actual Length = 145.73266mm

Violation

Ru是规数: 25 cms : 2

(走线长度限制)

Processing Rule : Daisy Chain Stub Length(Maximum =10.00001mm) (On the board )

Rule Violations:0

(违规数: 0)

(支线长度限制)

Processing Rule: Acute Angle Constraint (Minimum=45.000) (On the board ), (On the board )

Rule Violations : 0

(急转角大小限制)

Processing Rule: Hole Size Constraint (Min=0.0254mm) (Max=3.5mm) (On the board)

Rule Violations : 0

(孔大小设定限制)

Processing Rule: Width Constraint (Min=0.5mm) (Max=0.5mm) (Prefered=0.5mm) (On the board)

Rule Violations : 0

(线宽设定限制)

Processing Rule: Clearance Constraint (Gap=0.53mm) (On the board ), (On the board )

Rule Violations : 0

(间距限制)

Processing Rule : Broken-Net Constraint ( (On the board )

Violation

Net GND

is broken into 2 sub-nets. Routed To 98.44%

Subnet : 11C9-2

11C6-2

11C4-2

11R9-1

11C2-1

11J5-1

11R8-2

11R1-1

11R3-1

11C12-1

11C7-2

11C11-2

9RW3-2

11C10-2

9RW3-1

11C16-1

9C20-2

9J5-1

9C16-2

11R14-1

9C17-2

9RW2-3

902-5

9C12-2

9RW2-2

9C15-2

11R12-1

9U1-2

9C10-2

9C13-2

11C3-2

952-11

9J2-1

952-10

952-12

952-9

952-14

9S2-15

9C9-2

952-16

9C1-3

9C1-1

9C11-2

9C8-2

9C5-2

9C7-2

951-11

951-13

9C6-2

951-10

951 - 14

951-9

9S1-15

951-16

Subnet : 11L3-

11L3-

Rule Violations :1

(未通网络限制)

Processing Rule: Short-Circuit Constraint (Allowed=Not Allowed) (On the board ), (On the board

Violation between Pad 11L3-(1105.836mm,1111.612mm) MultiLayer and Pad 11L3-(知路展制,1112.412mm) MultiLayer

Violation between Pad 11T1-(1103.992mm, 1135.808mm)

MultiLayer and

Pad 11T1-(1104 792mm 1135 808mm) MultiLaver

```

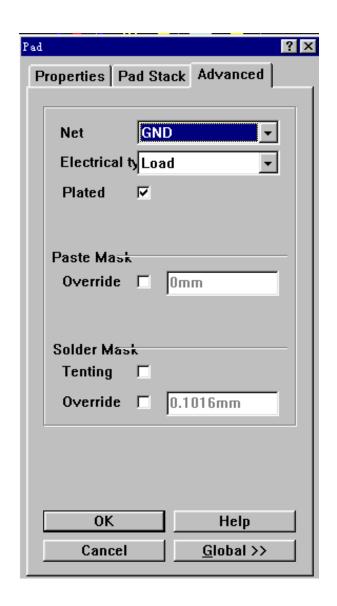

可以看到除了走线长度限制有两个错误,未通网络限制有一个错误,短路限制有三个错误外,其他的都已经没有错误了。这差不多是最后的成品了。所以错误已经是很少的了,或者说已经是没有错误了,因为这些错误在以后的大面积覆铜之后就会没有了。大面积覆铜后会将 GND 的走线和焊盘都连在一起。所以走线长度限制中 Net GND Actual Length 就不会过长了。而且未通网络限制中 Net GND is broken into 2 sub—nets Routed To 98.44%,GND 的网络被分成了两部分,这里有很多未连通的 Nets(Protel 中用来表示要用电线互相连上的网络标号)11C9—2、11R1—1等都属于GND 的网络。在覆铜后将会把分开的部分都连上,因为覆铜都是 GND。而短路限制的错误是我在做变压器的封装时,将两个焊盘叠在一起后成为一个大焊盘所致的。这里两个焊盘短路了。但只要将这两个焊盘的 Net 属性都设为 GND(如下图),在覆铜后就没错了。

第一次自动布线通常都会有很多的错误出现。远不止上面几个错误,有时还是原理图里面有错,则应先及时改正更新原理图和网络表,并重装网络表后再布线。

# 3-9 手动布线修改

虽然 Protel 99SE 的布线率很高,但还是会出现很多较机械的布线方式,影响了电路板的性质和美观。一块成功的电路板,其设计往往是在自动布线的基础上,经过多次修改,才能达到令人满意的效果。

1. 撤消布线可以用 Undo/Redo 操作,在操作中也用到自动拆线,Tools Un-Route 的子菜单中,有不同的选择:

All: 拆除电路板图上所有的铜膜线。

Net: 拆除指定网络的铜膜线。

Connection: 拆除指定的两个焊盘之间的铜膜线。

Component: 拆除指定元件所有焊盘所连接的铜膜线。

2. 改线。通常由于电脑的机械性,自动布线通常会造成走线冗余,走线过长、走线有可能会造成

电磁干扰等的错误。这就需要用手工改正走得不好的线。

方法: 1、用鼠标单击要修改的走线,则该走线一段直的部分被选中。

可以进行: a 删除--按键盘 Del 键; b 拖动--用鼠标按住左键拖动。

也可以用拉线技术,Edit Move Break Track:截断连线,截断后就能用鼠标拖动截断点。Edit Move Drag Track End: 拖动连线端点。Edit Move Re-Route 是重新走线,它和 Break Track 的差不多,只是 Re-Route 能连续的拖动截断点,同时画出有不同转角的线。

最常用的方法: 就是选中不满意的 TRACK, 然后按 DEL 将其删除, 再 Place → Track。自己重新画一条。

3. 添加电路输入端/输出端和电源端的焊盘,过孔等。在本实验板上我已经用一个封装将电路输入端/输出端和电源端做好了,就是那个 JIEXIAN 的封装,它是一个接线柱。在板上我用过孔做了四个螺孔,放在四个角上如下图:

并把它们的 Net 属性改为了 GND,这样在覆铜的时候过孔就和地连在一起了。这能增强电路板的屏蔽能力。同时我在板的一些空位上加上了一些小过孔,把上下两边的覆铜能更好的连接。进一步减短器件接地端到地的距离。而且把所有的地都连成共地。这些都是为了减少电磁干扰,让高频实验板的成功率更高。

- 4. 加粗地线、电源线、功率输出线等。这部分我并没有做,因为电流不是很大,而且我在后面将会用到覆铜,这样就相当于加粗了地线。同时我已经设好了间距限制,如果再调整线宽将要考虑很多。要花费很多时间,但有时间最好都做好它。

- 5. 你还可以对所有过孔和焊盘补泪滴,补泪滴可增加它们的牢度,但会使板上的线变得较难看。顺序按下键盘的 S 和 A 键(全选),再选择 Tools-Teardrops,选中 General 栏的前三个,并选 Add 和 Track 模式,如果你不需要把最终文件转为 PROTEL 的 DOS 版格式文件的话也可用其它模式,后按 OK 钮。完成后顺序按下键盘的 X 和 A 键(全部不选中)。

在修改布线的时候通常需要切换到单层显示模式下(点击菜单命令 Tools/Preferences,选中对话框中 Display 栏的 Single Layer Mode)以观察走线是否正常。将每个布线层的线拉整齐和美观。

手工调整时还应经常做 DRC, 因为有时候有些线会断开而你可能会从它断开处中间走上好几根线,而且经修改后就可能有不符合原来设定规则的现象。这些都得有耐性的去修改。快完成时可将每个布线层单独打印出来,以方便改线时参考。

# 3-10 屏蔽层

在高频电路中为了减小干扰,可采用大面积接地,这就是上面我所说到的大面积覆铜了。这是指多边形栅格(条)铜箔面,如果在放置它时就把多边形取为整个印板的一个面,并把此栅格(条)与电路的 GND 网络连通,那么,该功能将能实现整块电路板的某一面的"铺铜"操作,经过"铺铜"的电路板除能提高刚才所讲的高频抗干扰能力外,还对散热、印板强度等有很大好处,另外,在电路板金属机箱上的固定处若加上镀锡栅条,不仅可以提高固定强度,保障接触良好,更可利用金属机箱构成合适的公共线。

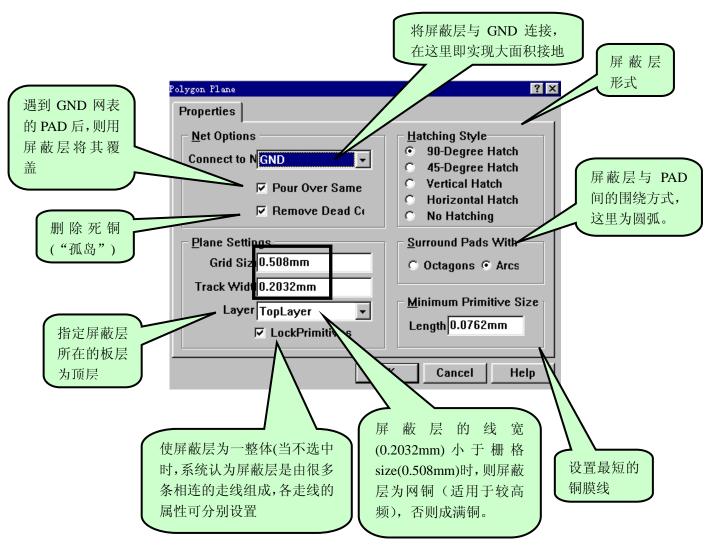

将设计规则里的安全间距暂时改为 0.5-1mm(这里照用了间距限制 0.53mm) 并清除错误标记, 选 Place Polygon Plane 在各布线层放置地线网络的覆铜。下图即为在顶层放置覆铜的设置对 话框:

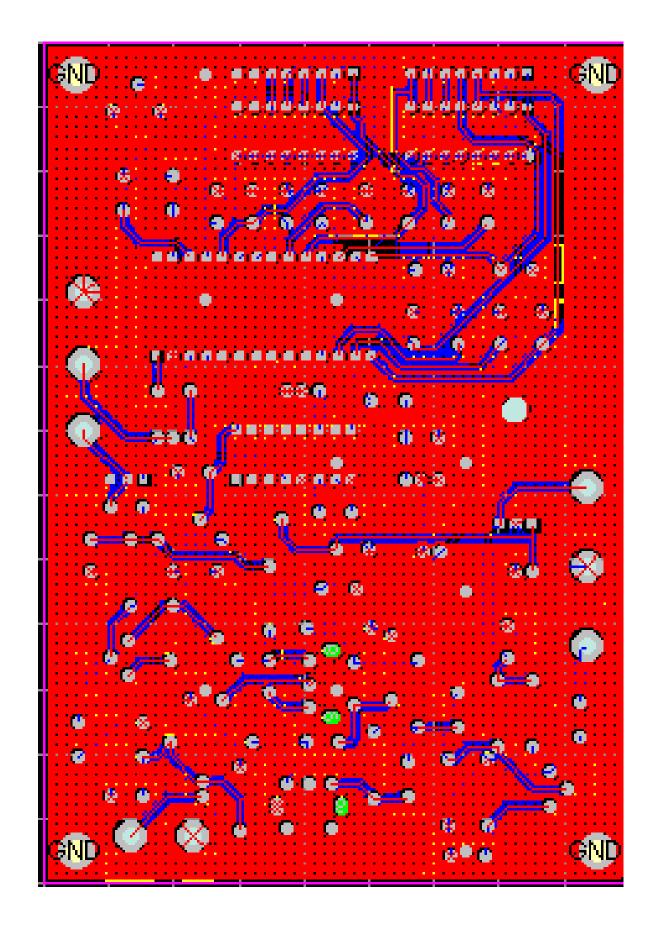

设置完成后,再按 OK 扭,画出需覆铜区域的边框,最后一条边可不画,直接按鼠标右键就可开始覆铜。它缺省认为你的起点和终点之间始终用一条直线相连。框出要使用屏蔽层的区域后,系统将自动生成屏蔽层,下面是顶层和底层都覆铜的图片:

经试验用 0.53mm 的间距限制基本上能把板上的各个部分都布满铜,但最好设置间距限制大一点,因为太近的距离制作工艺要高一点(保证不会短路)。在设置大的间距时可能布不满铜,有些较大面积没有覆铜的地方,那就在对面层有覆铜处放一个过孔,双击覆铜区域内任一点并选择一个覆铜后,直接点 OK,再点 Yes 便可更新这个覆铜。几个覆铜多次反复几次直到每个覆铜层都较满为止。将设计规则里的安全间距改回原值。最后再做一次 DRC 检查,有错就改。

到这时 PCB 部分已经差不多了,最后的任务就是认真的检查电路板上的各个部分有否问题, 和遗漏,经检查没错后就可以拿去生产商做板了,只需要那个.PCB 文件就行了。