# FPGA 经典 100 问之<下载验证 16 问>

### FPGA 是什么?

FPGA 即现场可编程逻辑门阵列(英语: Field Programmable Gate Array, FPGA),是一个含有可编辑元件的半导体设备,可供使用者现场程式化的逻辑门阵列元件。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

现把历年来众多网友和专家联手打造的 FPGA 经典 100 问奉献给大家,包括<HDL 28 问>、<仿真 20 问>、<设计实现 31 问>、<下载验证 16 问>、<入门与提高 5 问>。初学者必备!

FPGA 经典 100 问 之《HDL 28 问》&《仿真 20 问》下载 点击下载>>45 篇博文精粹《菜鸟变高手,草根成长记》 点击下载>>特权同学倾力巨献---FPGA 学习资料下载汇总

### 1、nios2 cycloneII 速度问题

### yuan ya 问:

在 EP2C8-208-Pin 中,老师把程序放在 EPCS4 里面,然后映射到 SDRAM 里面,我的问题是: 1.如果没在 SDRAM,程序直接在 EPCS4 里面运行,速度能达到多少?有 SDRAM 的话,速度达到多少?

2.板子里面的 CLK 是 25MHZ,有倍频到 100MHZ 的一个设置,是不是这个 FPGA 的速度最大是 100MHZ? 不是的话那么我们常说的它能跑多少 MHZ 指的是它的什么速度? 谢谢。

#### ilove314 答:

这个问题很复杂。你要去深入了解一般嵌入式系统的工作方式。从 ROM 直接启动并运行与 从 ROM 启动但 RAM 运行,性能差异非常大。ROM 肯定要比 RAM 慢很多。另外,SDRAM 的时钟频率不是 CPU 的运行速率,这个不能对等,你要去了解 CPU 的工作机制,什么取指、译码、操作等等,这样你才能够去评估系统的运行速率。

查看更多回答与讨论>>

# 2、nios 运行时卡死

### sangreal599 问:

本人在 EDN 第一次发帖:

我使用的是 quartus 11.0 和 nios IDE 11.0,当 run as hardware 的时候,卡在下图中半个多小时都没有前进:

### 赤子旭升 答:

可能是连接的问题,你在运行之前,这样操作一下: Debug Configurations -> Target Connection -> Refresh Connections -> Apply 试一下看看吧查看更多回答与讨论>>

# 3、讨教 NIOS 2 开发板中 TFT-LCD 例子的一个问题

#### xdx8088 间:

关于 SF—NIOS 2 开发板,TFT——LCD 的例子中,有个问题一直没有想明白,请问下面函数 里面为什么 y, x address 分别是向左移动 10 位和 1 位,根据 as\_LCDwr 模块内设置,应该 是低 9 位为 x 地址, 因此应该是 y 向左移动 9 位, x 不需移动吧?急盼高手指点。

IOWR 16DIRECT 函数的偏移地址跟 avlone 总线的地址是什么关系呢?

```

void lcd_wrdb(alt_u16 xaddr,alt_u16 yaddr,alt_u16 cor)

{

IOWR_16DIRECT(AS_LCDWRM_BASE,((yaddr<<10)+(xaddr<<1)),cor); //LCD 显示内存映射地址写入色彩数据

}

```

### ilove314 答:

NIOS2 是 32 位的,但 alalon 的默认寻址是 8 位的,而我们所使用的 LCD 外设定义的一个显示数据是 16 位,即对应两个地址

查看更多回答与讨论>>

### 4、关于 SDRAM 串口调试代码中的疑惑

### jokeboy999 问:

SDRAM 串口调试程序里面的 sdram ctrl 模块里面

这段代码中,是如何计算的呢?比如 TRP\_CLK = 9'd4,这个 4 怎么和 18ns 联系上的?如果按照你设的时钟是 100M 的话,4\*10ns 应该是 40ns 啊?不理解,另外

`I\_PRE: init\_state\_r <= (TRP\_CLK == 0) - `I\_AR1:`I\_TRP; //预充电状态

`I\_TRP: init\_state\_r <= (`end\_trp) - `I\_AR1:`I\_TRP; //预充电等待\_TRP\_CLK\_个时钟周期

这个('end\_trp) - 有自增功能吗?我这段代码看不明白,'end\_trp 是常数 TRP\_CLK = 9'd4 吧? 希望给指点下

### yuechenping 答:

仔细看一下芯片的资料,例如,TRP=18ns 预充电有效周期是芯片规定的最小的预充电有效周期,只要大于等于这个预充电有效周期就可以, TRP\_CLK = 9'd4,表示这个预充电设置为4个时钟周期,可以满足芯片设计要求, 至于后面的初始化,建议你多看看 SDRAM 的初始化过程,以及 SDRAM 的参数设置。

查看更多回答与讨论>>

### 5、请教 FPGA 烧写问题?

## 今生缘 问:

我焊了一块 EP2C5T144C8N 的板子,代码已经烧进配置芯片 EPCS4 中。现在等好长时间上电后,FPGA 能跑,但断电在上电后有时能跑有时不行。不好时,nSTAYUS 和 CONF\_DONE 管脚一直为低电平,nCONFIG 为高电平,正常的配置成功应该都为高电平。还有 nCONFIG 通过开关接地,如用万用表正端接 nCONFIG 管脚,负端接地,按开关拉低松开后拉高,这样有时会配置好 FPGA 使它正常运行,但两端没万用表就不行。板子的电路没问题,因为焊了 2 块另一块是好的。请问可能会是什么问题呢?帮忙看看,谢谢!

### jlx cuc 答:

个人猜想啊,会不会是你的这个板子上的这个开关焊的有问题呢?我曾经有过一个教训,和你差不多,但我用的是按键,按键有 4 个腿,其中两个是连在一起的,另外的才是两路接口……悲剧的是我方向弄反了,所以出现了你说的这样~

另外, 你接上拉电阻了么?

查看更多回答与讨论>>

# 6、关于 xilinx 的 genesys 实验板程序烧录到 rom 的问题

### ersh 问:

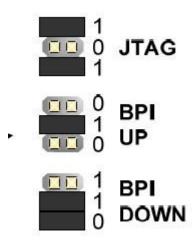

现在我用的是基于赛灵思 virtex5 的 genesys 实验板,但是我在烧录程序时遇到一点问题。使用 BPI-UP 模式下载程序到 rom 里面,已经按照说明文档的做法盖上跳线帽(第二种)。

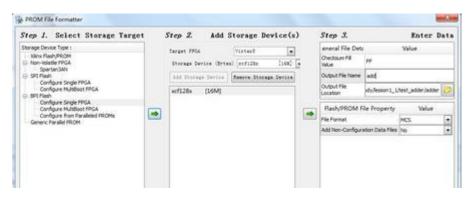

然后在 iMpact 里面选择合适的 pRom,想问问我这样配置是否正确?

最后是下载界面会出现错误的提示信息

INFO:iMPACT - Common Flash Interface Information from Device:

INFO:iMPACT - Verification string: 51 52 59

INFO:iMPACT - Manufacturer ID: 89

INFO:iMPACT - Vendor ID: 01 INFO:iMPACT - Device Code: 19 Setting Flash Control Pins ...

ERROR:iMPACT - '1': The part size read from the flash device does not match the part selected. 想问问这个 size not match 是什么意思?我在用户手册看到的是 16M 的 flash,配置选型的时候选的是 xcf128x【16M】。

谢谢大家了!

#### sieg70 答:

IMPACT 中左邊選 SPI flash - configure single FPGA 是對,其它部份圖不清楚無法判斷. 當真的要寫入時,應選 PCB 板上所用的 flash 型號,這並非 Xilinx 自家的 PROM,所以要對著板子上的晶片型號來選.應是選 Numonyx P30.

查看更多回答与讨论>>

# 7、FPGA 的 JTAG 不能下载。JTAG 是不是烧了?高手帮忙

## 海盗先生 问:

JTAG 口不能下载,现象和烧坏一样,可网上都说烧坏的表现是 JTAG 引脚和 GND 短路,现在 我这 JTAG 引脚没短路,只是有个引脚和 3.3V 之间电阻很小,只有 100 欧。这属于烧坏吗?如果是,还有什么解救办法吗

### EE2012 答:

以前能下载吗,如果可以的话,请先断电后拔下,等一会再插上去再试下,一定断电操作。 查看更多回答与讨论>>

### 8、求助 ACTEL 的 FPGA

### 可乐兑 问:

我想咨询各位大侠一下,谁用过 ACTEL 的 FPGA 不? 是不是它的烧写次数只有几百次啊??那岂不是很容易以不小心就烧写坏了啊?

### jlx cuc 答:

您说的这个问题应该不会。。。ACTEL 分两类,一个是 FLASH 的,一个是反熔丝的,虽然相比其它两个厂家有些不太一样,但也不会是几百次的

查看更多回答与讨论>>

# 9、JTAG 的 TDI 和 GND 短路如何处理

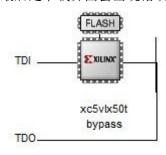

# <u>《whlgsxy》</u> 问:

如题,求指导,另外求如图所示的 FPGA 板子原理图

### coyoo 答:

找到短路点,然后再想法解决

查看更多回答与讨论>>

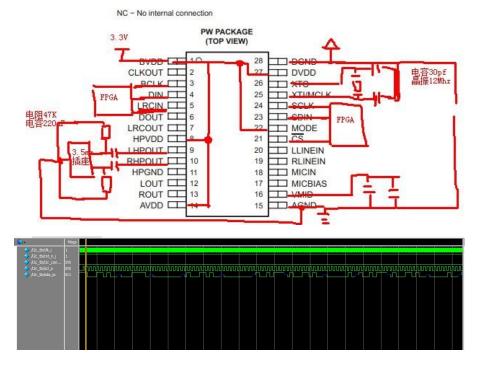

# 10、FPGA 做音频播放,与 TLV320AIC23 调试的难题!!

#### johnnyluck 问:

求助各位大大,我现在在用 FPGA 做一个音频播放系统,使用 TLV320AIC23 做 DAC。其他模块都搞定了,但是 AIC23 怎么调试都不行。

求助各位,有没有用过 AIC23 这款芯片的,应该怎么配置啊?

我使用 verilog 写了 I2C 和 SPI 模式来配置 AIC23,设置了寄存器 CLKOUT=1/2 MCLK。但是 AIC 的 CLKOUT 依然还是输出 MCLK。

SPI 和 I2C 时序用仿真看都正确。

时间很急,各位帮帮忙,谢谢!!!

怀疑是不是我电路没有接好?

把我的电路图和代码仿真图都上了,希望能帮帮忙!! 头痛中啊~~~~

I2C 时序的时候, 我试过给 SCL 和 SDA 加上拉电阻, 但是还是配置不进去。

看到有些原理图,需要在电源和地之间加上几个电容,我没有加,是不是这个有问题? 麻烦各位了。。。。。

#### kgeneral 答:

I2C 必须要加上拉电阻才能使用的呀,至于 IIC 不能配置 audio 芯片原因有很多,比如频率是否正确,通信时序是否标准,依照你的应用,IIC 的同步时钟频率应为 100k,再依照 audio 芯片的手册好好对比一下通信时序吧;

### 局域网的游客 答:

逻辑分析仪抓取波形就知道了,I2C 通信时有没有 ACK 应答。 alter 芯片的话直接用 signaltap 就搞定。

查看更多回答与讨论>>

## 11、求助! JTAG 检测不到!

# <u>lincomcn</u> 问:

用的是 cylone3, 144pins, 有两个问题:

1: AS 方式可用,从 quarters 看下载成功了,但是,电路板上的 config\_done 还是低电平,程序没有成功下载,写了个小分频程序,没有检测到,应该是没有配置成功! 完全按照 Handbook 设计的? 这个是怎么回事?

2: JTAG: no devices detected, 感觉硬件设置都对,就是看到一些说法,是需把芯片底下的地 pin145 ,连接好,但是我的设计把这个地悬空了,是这个原因么?求解答,Msel=010,这个 1 接的是 VCCA=2.5V。

希望高手给我解答一下,着急啊! 毕设相关,别最后毕业不了了!

# jonson simth 答:

试一下试把它连接起来吧! 试一下又没有什么影响!!! 多试!

### ppc68 答:

把芯片底下的地 pin145 确实是需要接到地的,曾经就因为这脚没接到地导致 JTAG 接不上查看更多回答与讨论>>

## 12、nios2 中 run as hardware 时 printf 函数输出乱码

### luceky 问:

请问,在 nios2 中 run as hardware 时 printf 函数输出出现乱码是什么原因?这个问题困扰很久了。比如说说出一个字符串 initialing sd card is ok!输出结果为 initi ss ccdd ii kk

### 赤子旭升 答:

可能是 RAM 空间太小了 查看更多回答与讨论>>

### 13、用 JIAG 配置 EPCS 时出现问题,跪求大神

#### qiyei2009 问:

使用 JTAG 方式配置 EPCS 芯片时,转换文件时,出现 Size of file(s) in EPCS1 exceed memory capacity 为什么我的会出现这种情况啊,我的程序不大啊,很小的一个程序。 跪求大神解 决方案

# coyoo 答:

这个跟你程序大小没有关系,而是跟你使用的 FPGA 器件容量有关系。问题应该是 EPCS1 无法配置你使用的 FPGA 的容量,即 FPGA 的容量超过 EPCS1 的范围,还是选一个大一点的配置芯片吧。

查看更多回答与讨论>>

## 14、xilinx 的 fifo 问题

# <u>lincomcn</u> 问:

大家好:

我用 xilinx ipcore 生成一个长度为 128,宽度为 1byte 的 fifo,core generator 上说实际的长度 有 127 个。但是我每次烧程序后,第一次写 127 个 byte 就满了,以后每次都要写 129 个 byte 才满。这是怎么回事?

还有 spartan3 能否使用 chipescope,我用 inserter 想要生成 ICON 核实,上面说 No parameter exist in this device。

希望大侠们解答我的疑惑!

### xiaofeng2001 答:

不用管,继续下一步就可以了,我也遇到过这个问题。如果是从 ISE 环境生成 chipscope 的话,就是这样的,没关系,继续下一步就可以了

查看更多回答与讨论>>

### 15、stratix iv GX 高速收发器的问题

### coolcheng13 问:

使用 ALTGX IP 核, 参数设置为,basic 协议,16 位数据,使用 8b/10b 编码,数据传输速率为 2500Mbps。

通过光纤发送接收数据,结果发现接收到 16 位数据的高 8 位与低 8 位字节对调了,高 8 位变成了低 8 位,低 8 位变成了高 8 位,论是片内环回调试,还是通过光纤连接调试,都是一样!求高人指点!

### 冲出藩篱 答:

仔细看手册,有一个 rx\_ctrldetect 的指示信号根据你 K 码的位置,调节是否进行高低 8bit 的 互换

### paradoxfx 答:

楼主再仔细看一下这个 IP 的用户手册,时序图之类的吧。。。不过 IP 有 bug 也是正常的事情, 所以经常要更新啊

查看更多回答与讨论>>

### 16、HC244 输出问题

### enovowangwei 问:

HC244 输入一个 3.3V 的 1Mhz 的方波后,期望得到 5V 的 1Mhz 方波,但是输出却含有杂波 而且幅值也是 5V,求高手指点。图中黄色为 3.3V 原波形,蓝色为 244 输出波形(将输入改为 500HZ 后,依然存在同样问题)

补充: 3.3V 原波形的上下冲很严重 怎么解决(波形由 FPGA 直接输出)

# <u>糖糖.exe</u> 答:

1MHZ 的方波是由 FPGA 分频产生的吧?我做过,可以输出很好的方波,经 74HC244 后幅值在 5.4V 左右(5v 供电),74HC244 不用的引脚都接地.你的程序有问题。查看更多回答与讨论>>